Lectures and lab sessions |

| Chapter 1: Combinational circuits | ||||||||||||||||

| W1 | L1.1 | L1.2 | ||||||||||||||

| W2 | L1.3 | L1.4 | Lab1.1 | L1.5 | PLA1 | |||||||||||

| W3 | L1.6 | L2.1 | Lab1.2 | L2.2 | ||||||||||||

| W4 | L2.3 | L2.4 | Lab 2 | L2.5 | PLA1 | PLA2_3 | ||||||||||

| W5 | L3.1 | L3.2 | Lab3 | L3.3 | ||||||||||||

| W6 | L4.3 | L4.1 | Lab4.1 | L4.2 | PLA2_3 | PLA4 | ||||||||||

| W7 | AR1 | Q1-4 | ||||||||||||||

Midterm exam |

Chapter 1 | 7 April 2026 (18:00 - 19:30) | ||||||||||||||

| W8 | Lab4.2 | |||||||||||||||

| W9 | PLA4 | |||||||||||||||

|

Fig. 1. Symbol of a generalised combinational circuit. This block is described by its truth table or the equivalent canonical equations product of maxterms or sum of minterms. |

| Due dates for P_Ch1 post laboratory assignments after having practised in lectures and lab sessions: | ||||||||||||||||

| PLA1 | Due date: 4 March | Circuit analysis using pen & paper (method I), Proteus (method II), VHDL EDA tools (method III) and Wolfram Alpha (method IV). | Q & A | |||||||||||||

| PLA2_3 | 22 March | (A) | Circuit design using single-VHDL file plan A and plan B and multiple-file hierarchical plan C2. Standard arithmetic and logic circuits. | |||||||||||||

| PLA4 | 22 April | Gate level measurements and technology: how fast is a circuit operating? Laboratory prototype FPGA + PCB + measurements. | ||||||||||||||

| Chapter 2: Sequential systems | ||||||||||||||||

| W7 | L5.1 | |||||||||||||||

| W8 | L5.2 | L5.3 | L6.1 | |||||||||||||

| W9 | L6.2 | L7.1 | Lab6 | L7.2 | PLA6_7 | |||||||||||

| W10 | L7.3 | L8.1 | Lab7 | L8.2 | ||||||||||||

| W11 | PLA6_7 | |||||||||||||||

| W12 | L5.4 | |||||||||||||||

|

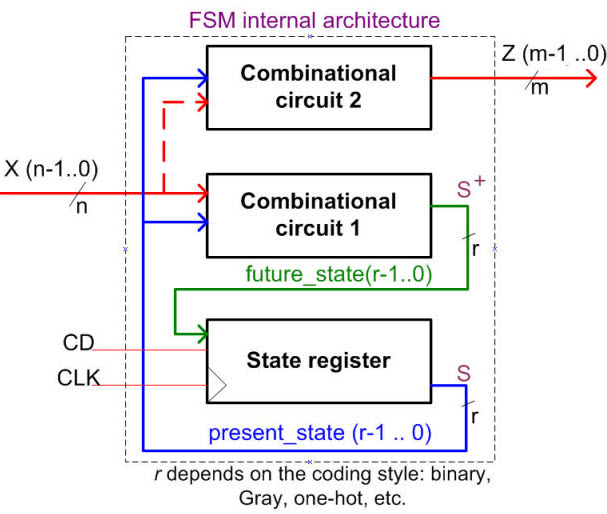

Fig. 2. Internal architecture of a synchronous canonical finite state machine as studied in CSD. The state register contains a bank of r D_FF memory cells. r depends on state coding style selected. The FSM, even if structured internally in three blocks, is implemented in a single VHDL file with processes instead of components (the only time where plan C1 is used in CSD). |

| Due dates for P_Ch2 post laboratory assignments after having practised in lectures and lab sessions: | ||||||||||||||||||||||||

| PLA6_7 | Due date: 10 May | (A) | Designing FSM, datapath and dedicated processors | Q & A | ||||||||||||||||||||

| Chapter 3: Microcontrollers | ||||||||||||||||

| W11 | L9.1 | Lab9 | PLA9 | |||||||||||||

| W12 | L9.2 | L9.3 | ||||||||||||||

| W13 | L9.4 | L10.1 | Lab10 | L10.2 | PLA9 | PLA10_11 | ||||||||||

| W14 | L11 | L12.1 | Lab11 | L12.2 | ||||||||||||

| W15 | L12.3 | AR2 | Lab_AR | Q5-12 | ||||||||||||

Final exam |

Chapter 2 |

Chapter 3 |

5 June 2026 (15:00 - 16:30) | |||||||||||||

| W16 | PLA10_11 | |||||||||||||||

|

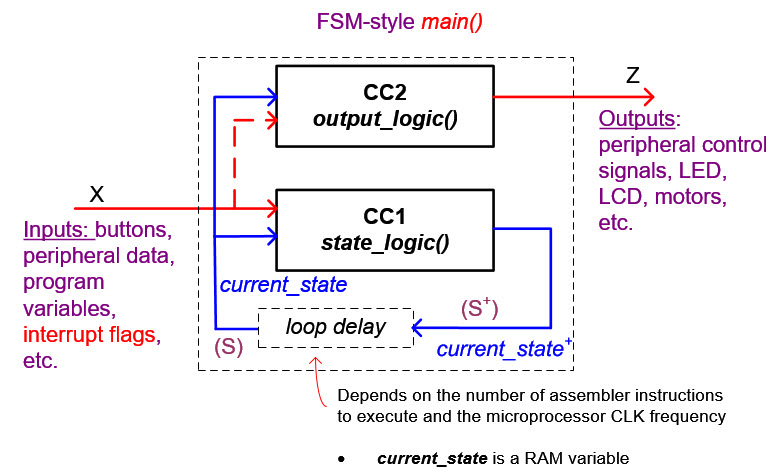

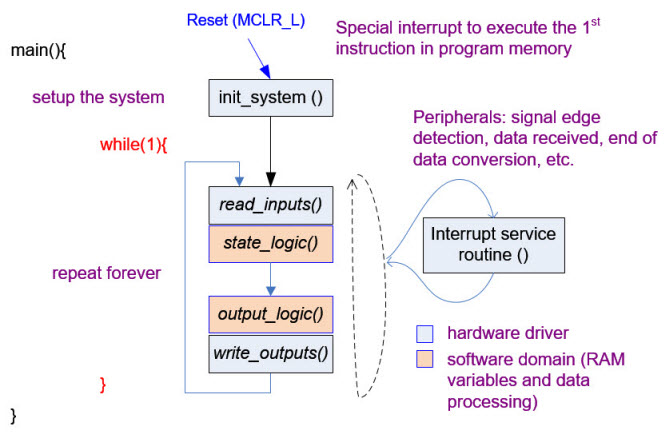

Fig. 3. The key concept in Chapter 3 is adapting the FSM structure to software environment in C language. Our programming style and code organisation will mimic concepts studied in previous chapters. |

| Due dates for P_Ch3 post laboratory assignments after having practised in lectures and lab sessions: | ||||||||||||||||||||||||

| PLA9 | Due date 20 May | Microcontroller. Basic digital I/O pins | ||||||||||||||||||||||

| PLA10_11 | 14 June | (A) | Phase #1: Adapting FSM to μC, interrupts; #2: LCD; #3: TMR | Q&A | ||||||||||||||||||||

Key note: PLA2_3, PLA6_7 and PLA10_11 are online submissions at the Atenea platform. Only materials submitted before due dates are considered for grading. To avoid any problems with file types or sizes, please, do not wait until the last minute. Be sure and check that your files can be downloaded and unzipped correctly and also that you include a valid link to your video presentation. Add as well your own self-assessment indicating what grade you might get with respect to our marking guidelines.

Current term classes and laboratory sessions: