PLA4: Circuit speed, technologies and prototypes |

Specifications

Prerequisite training: Study in detail and execute in your computer these tutorials P1 design, P2, P3, P4, Lab 4.1, Lab 4.2 before attempting this PLA.

This group assignment covers two parts:

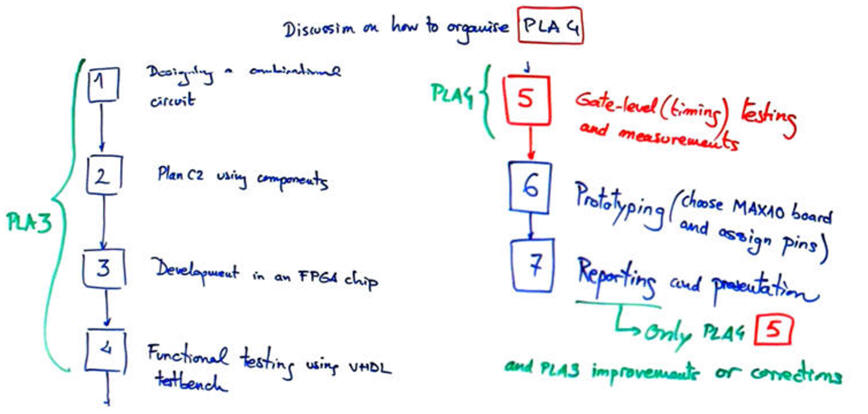

(Part 1) Lab groups will continue their PLA2_3 adding the section #5 from our VHDL design flow to perform timing measurements. NOTE: if you were assigned several projects, choose only one for solving this part 1.

(Part 2) Lab groups will experiment on lab prototyping and measurements (VHDL design flow section #6) to operate and characterise the ALU_9bit prototype from Lab 4.2.

|

|

| Fig. 1. Concepts and ideas to develop in this assignment. This map is also translated in the series of questions below in roman numerals: I, II, III, ..., IV. Imagine that each question is marked with 1p. |

|

NOTE: This is cooperative group work. You must explain in the planning section of your report who is in charge of each section, who is leading the tasks, who is developing the components or sections, who is measuring or testing, etc. It is fundamental in order to obtain good assessments that you explain very well which is the contribution to the final project of each one of the group members. We aim you practise efficient teamwork. |

Questions on Lab 4.1 (PLA2_3 project section #5)

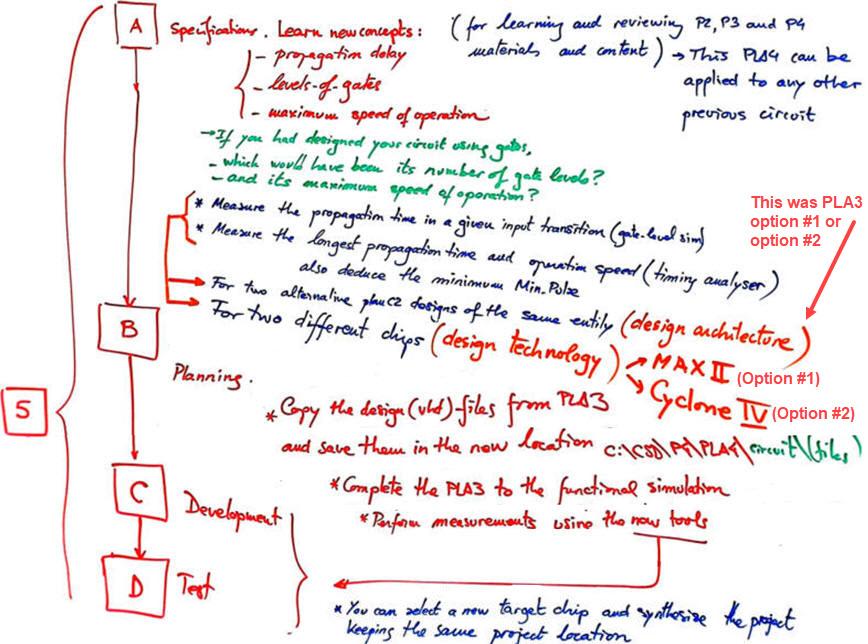

The new VHDL design flow section #5: characterising how fast is the circuit for the given internal design architecture you solved in PLA2_3, and for a two target chip options to see which is faster.

Initial work to do:

I) Solve one of the tutorials from Lab 4.1 in your computer to learn how to perform gate-level simulations and how to use the timing analyser tool.

Example of exam question: If instead of CPLD/FPGA chips, we were designing using classic chips, how many NGL (number of levels of gates) will contain your circuit? (To answer this question imagine that your architecture is based on plan A (NGL = 3) and plan C2).

II) If your PLA2_3 circuit is not yet fully operational or were not correctly synthesised or tested, take some time to correct and complete it. PLA2_3 sections 1 - 2 - 3 - 4 do not have to be reported again, explain only in an annex what was wrong and repaired.

Simulations and calculations

Using the same VHDL files at the new project location C:\CSD\P4\your_circuit\..., you will repeat measurements for two target chip options (technology) in order to compare results:

III) Measure the propagation delay tPt in a given transition using gate level simulations and vertical cursors on the wave diagram. Draw an schematic indicating the operands or inputs that are switching and the expected results.

Note: Quartus Prime timing analyser can be used for any target chip. However, remember that for running ModelSim gate-level simulations, if you were assigned the FPGA option MAX10, you have to change it by MAXII or Cyclone IV. Intel Quartus Prime does not generate MAX10 delay files (sdo).

IV) Using the timing analyser, determine the propagation delay tP, the longest propagation path from a given input port to a given output port. Draw an schematic to explain the meaning of this measurement.

V) Calculate the theoretical maximum speed of operation of your circuit. Which technology is faster?

VI) Demonstrate that your circuit does not calculate or operate correctly its truth table when the testbench Min_Pulse parameter is shorter that the circuit's propagation delay tP. Thus, reframing the question: what is the minimum value for Min_Pulse in gate-level testbenches?

Questions on Lab 4.2 (project section #6)

The final section #6 on prototyping will be carried out using the ALU_9bit in Lab 4.2. Remember that this kind of experiment will allow you as well to study and review all Chapter 1 materials for solving exams.

We will write a report on experiments and lab measurements. Some interesting questions to answer are for example:

Experiment discussion

VII) Draw a paper flowchart of the sequence of measurements and ideas that you will discuss in this part with your group, other students and instructors.

VIII) Solve a pre-lab question that you find interesting or relevant. For example the E2425Q1 exam P1 that is focused in this ALU_9bit and some of its internal components. Review the concepts on logic bitwise operations, arithmetic operations using 2C, sign bit. Apply other input vectors if necessary. Play with your ALU_9bit to verify that it is running arithmetic and logic operations.

IX) Draw a paper sketch of the experiment for measuring the static power consumption, at DC or low frequency (1 kHz). Remember that you have to unplug the USB; all the power is drained from the VB8012 power supply of 5 V. Indicate the instruments used for measuring power.

X) Draw a paper sketch of the experiment for measuring the propagation delay from B(0) to C. Let us use operands that switch all outputs.

1. Check that the circuit works when clicking the pushbutton RTN_L.

2. Attach the Wavegen generating an square wave (pulse) of 3.3 V and 1Hz, to see that the circuit is switching the same as before when you were clicking the push-button.

3. Connect the oscilloscope CH1 probe to monitor the Wavegen signal B(0) and the CH2 to observe the C output. Increment the Wavegen frequency to visualise the real analogue signals. Do the experiment cables and layout generate unwanted transients or unexpected glitches (signal noise)?

4. Connect the logic analyser to visualise the digitalised signals. Find and zoom a signal transition to perform propagation delay measurements.

XI). Dynamic power consumption at 5 MHz or higher, how to measure it? Which is the circuit's fMAX?

Optional: If you have interest and time you are invited to prototype your PLA2_3 circuit in the DE10-Lite platform once the course ended.

P_Ch1 marking grid for projects PLA1, PLA2_3 and PLA4

P_Ch1 (work in progress, reports and presentations) represents 15% of the final grade:

=> PLA1 (30%) + PLA2_3 (report + video, 50%) + PLA4 + (20%)

| PLA2_3 handwritten report and video presentation: | ||||

| Video | Report | |||

| 4p | 6p | |||

Notes on lab assessment: student grades are not simply reflecting report or video quality, but implicitly, they include subjective items considered by instructors such laboratory participation, questions and answers, problem solving skills, attendance and punctuality, active attitude and group work. Work in progress includes completing tutorials, sample reports, sketches, diagrams, discussions, Q & A, presentations, live demonstrations, results, measurements, etc.

Reflect and give us your group feedback on what you learned in chapter 1 (from P1 to P4). Add a short paragraph in the final section of your PLA4.2 discussing aspects that you consider positive and negative.