Lecture 5 |

L2.5: Incomplete functions The concept of incomplete function (example: water level meter) |

[5 Mar] |

1.5.2.1.2. Minimised equations: SoP or PoS

- Don't-care inputs ("x" or "-")

- Incomplete functions: don't cares outputs

For some circuit applications not all outputs are of interest for given input combinations, and thus they may be considered as "don't care" in the truth table.

This Tank_level_meter project exemplifies incomplete output functions.

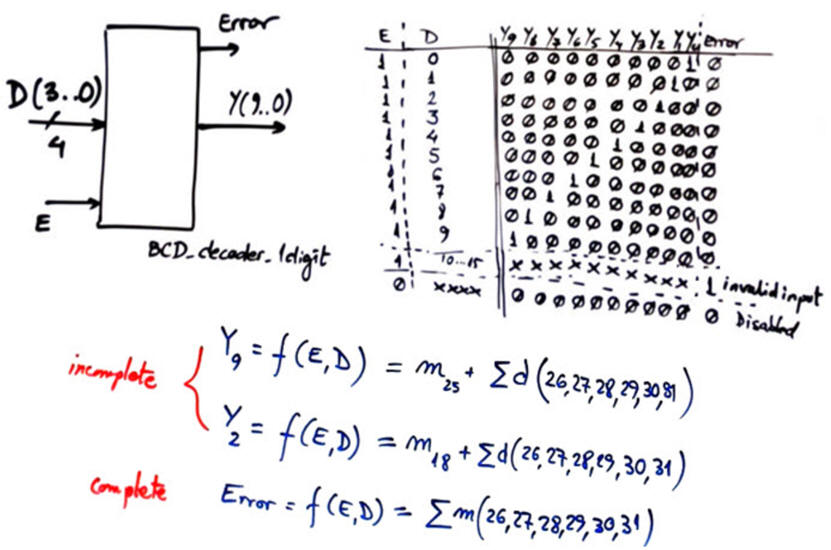

Another circuit that has incomplete logic functions is the BCD_dec_1digit represented in Fig. 1 because for this Binary Coded Decimal (BCD) the combinations from "1010" to "1111" are invalid, meaning that we are not interested in circuit outputs when they do not correspond to valid BCD input numbers. An Error output is used to signal (flag) such incorrect input situation.

|

Fig. 1. The BCD_dec_1digit truth table and examples of its canonical equations as incomplete logic functions. Error signal is a complete function whereas Y(9..0) are incomplete functions. |

Activity #1: Initial discussion of the BCD_dec_1digit in Fig. 1. Prepare the (1) specifications & theory, and (2) planning for one design strategy in VHDL:

Plan A: Obtain the logic function Error = f( E, D3 D2, D1, D0). Obtain the logic function Y7 = f( E, D3 D2, D1, D0). Obtain the minimised output equations using Minilog.

Plan B: Plan a flowchart or an schematic to capture the truth table in VHDL.

Remember that a project as a class activity requires this initial paper work:

(1) Specs & theory (our map of concepts)

(2) Planning. How we solve design projects using VHDL tools? Which design strategy to translate into VHDL files? a) sketch (enough for exams and peer discussion) and b) totally annotated schematic/flowchart required to start development

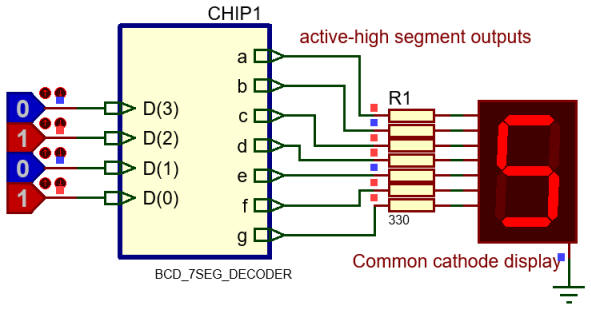

Activity #2: Another similar circuit example of incomplete logic function is the BCD to 7-segment decoder represented below. It contains 6 illegal inputs from which we don't care about the generated output values; the display must be blanked. And this condition will simplify the internal logic circuit.

Plan A: Obtain the minimised output equations using Minilog.

Plan B: Plan an schematic to capture the truth table in VHDL.

Remember that a project as a class activity requires this initial paper work:

(1) Specs & theory (our map of concepts)

(2) Planning. How we solve design projects using VHDL tools? Which design strategy to translate into VHDL files? a) sketch (enough for exams and peer discussion) and b) totally annotated schematic/flowchart required to start development

Important remark: Now that several weeks of classroom activities and post-laboratory projects have passed, it is time to reflect on how you are studying and managing your 10 hours per week in CSD.

Learn to organise your timetable carefully, and limit your CSD work once you have reached your weekly allowance, so as not to disadvantage your other subjects. Your primary goal should be to pass all the subjects in which you are enrolled.

Moreover, from this point onwards, many assignments will be set for your cooperative group, which both facilitates and complicates the management of your study time. Bear in mind that efficient teamwork can dramatically enhance your projects and your understanding of the course while saving a considerable number of study hours.