Electronic design automation (CAD/EDA) tools |

1. Enriched text editor

|

Notepad++ is a free source code editor and Notepad replacement that supports several languages. |

2. SPICE-based simulation and PCB EDA design tools

|

Proteus VSM from Labcenter Electronics (commercial) is a virtual laboratory and SPICE-based simulation of electronic circuits. Analogue electronics, digital circuits and microcontrollers simulation, all in one. |

Available at the EETAC. Download and install the current professional version in your home or portable computer and run our cloud licence as an EETAC student. Proteus examples. Contact us to get your you user/password. |

|

KiCad includes the open source spice simulator ngspice to provide simulation capability in graphical form through integration with the schematic editor. NOTE: Our current CSD and DEE KiCad symbols, footprints and 3D components are available in these three libraries DEE_libraries.zip to be unzipped and saved using these KiCad installation instructions. |

Free and absolutely recommended software. Full featured for students and hobbyists. |

|

Multisim from National Instruments (commercial) is the schematic capture and simulation program designed for schematic entry, simulation, and feeding to downstage steps, such as PCB layout. |

Available at the UPC, student licence. Instructions on how to setup the software. |

|

Fusion 360 (includes Eagle). |

Available at the UPC, student licence. |

3. Mechanical design

|

Mechanical design. FreeCAD is made primarily to design objects for the real world. It works with KiCad to build 3D component models (ref.). |

Free software. |

4. Numerical engines and other digital simulators

|

WolframAlpha. A powerful computing tool available from Wolfram Research. Examples on how to use it. |

|

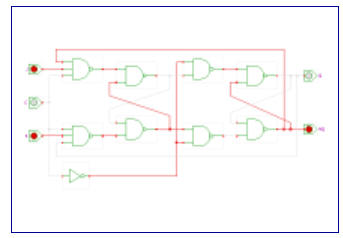

HADES Java applets, a framework for interactive simulation from University of Hamburg. Here it is more information on how to use and install it. |

|

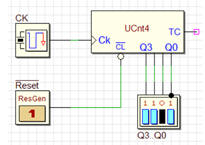

DEEDS Digital Electronics Education and Design Suite. Giuliano Donzellini, University of Genoa, Italy. |

|

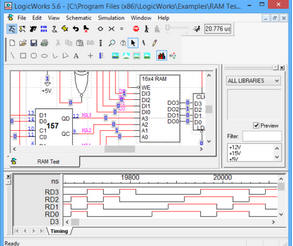

LogicWorks is a schematic drawing and interactive digital simulation package for demonstrating logic design principles and practices within the education sector and industry. |

|

EDA playground is a free online simulation platform from Doulos company. |

5. Minimisation of logic functions

| Minilog.exe application and tutorials on how to use it. (© W.M.J. de Valk). Minimisation program (source Wikipedia EXPRESSO). | |

|

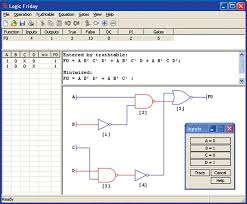

Logic Friday. Logic Friday takes the help of Espresso logic design minimiser to efficiently reduce the functions in your electronic design. Instead of using the traditional Karnaugh map method of min term reduction, the program manipulates the function iteratively to give a closely approximated result, eliminating redundancy. (ref.) |

6. Lattice Semiconductor EDA tools for CPLD and FPGA

|

Lattice Semiconductor Diamond. |

|

Lattice Semiconductor ispLEVER Classic. |

7. AMD EDA tools for CPLD and FPGA

|

ISE. Download and use the version 14.7 (2013). (ref). ISim is the integrated VHDL simulator that will be used to check our designs. This legacy software runs encapsulated in a virtual machine (Oracle VM) that opens a Linux operation system. The Digilent Adept application is required for downloading the configuration .bit file to the board. It can work as an standard alone program. |

|

Vivado is the new EDA tool from AMD to cover newer FPGA. To synthesise for a Basys 3 development board (Artix 7), it is enough the old version 2016.2 that can be installed in a virtual machine running Windows 7 . |

8. Intel EDA tools for CPLD and FPGA

|

Intel Quartus Prime. From its web page you can get the latest vendor version. However, to simplify the installation process, we currently use the version 20.1 shared in our Google Drive. ModelSim Intel Starter Edition is the integrated VHDL simulator that will be used to check our designs. Installation and examples. NOTE: from version 21.3, ModelSim Intel Starter is replaced by Questa-Intel FPGA Starter Edition. Mentor Graphics was acquired by SIEMENS. |

9. Microcontroller programming environment

|

Microchip integrated development environment. Indications on MPLABX-XC8 installation. |

|

XC8 C compiler. C language reference. µC configuration header: "config.h". LCD libraries: "lcd.h", "lcd.c". This software driver is copied from this reference. Learn how to use them in this tutorial P11.

|

|

10. Instrument control and board drivers

|

VB8012 - ADP5250 Waveforms driver |

|

Intel - Altera driver for programming FPGA |