CSD EXA1: midterm exam examples and solution ideas |

2425Q1 |

2324Q2 |

2324Q1 |

2223Q2 |

2223Q1 |

|||||

2122Q2 |

2122Q1 |

2021Q2 |

2021Q1 |

1920Q1 |

1819Q2 |

1819Q1 |

1718Q2 |

1718Q1 |

1617Q2 |

2425Q1 |

Problem 1

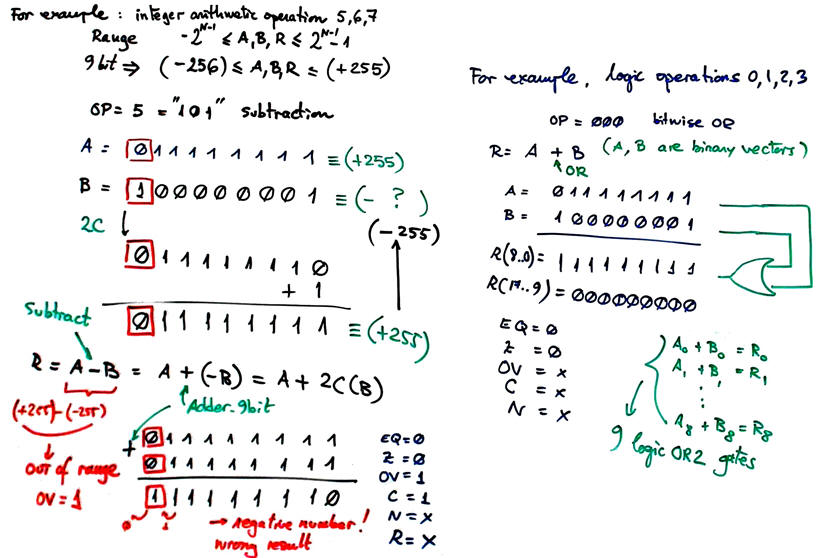

1. The ALU_9bit is designed in LAB4_2. Complete (at least) the 8 lines of the truth table using the given values A and B. The idea of an ALU is discussed in L4.2. This slide below shows how to explain two operations, one of them logic and the other arithmetic. Your aim is to be as clear as possible, as if you had to solve and explain the problem to a large audience repeating procedures and formats found in lectures and examples.

2. An example of a similar Int_Add_Subt_8bit and its internal architecture is presented as the highlighted project P4. L4.1 also explain how to operate integer numbers and the idea of its internal design using components such Adder_8bit.

3. An example of and Adder_1bit using MoD will use a Dec3_8 and two OR gates, as the examples in L3.4. The Adder_1bit is the basic component found in practically all digital systems, it is specified in detail in P3.

4. An example of and Adder_1bit using the MoM is in LAB3.

Problem 2

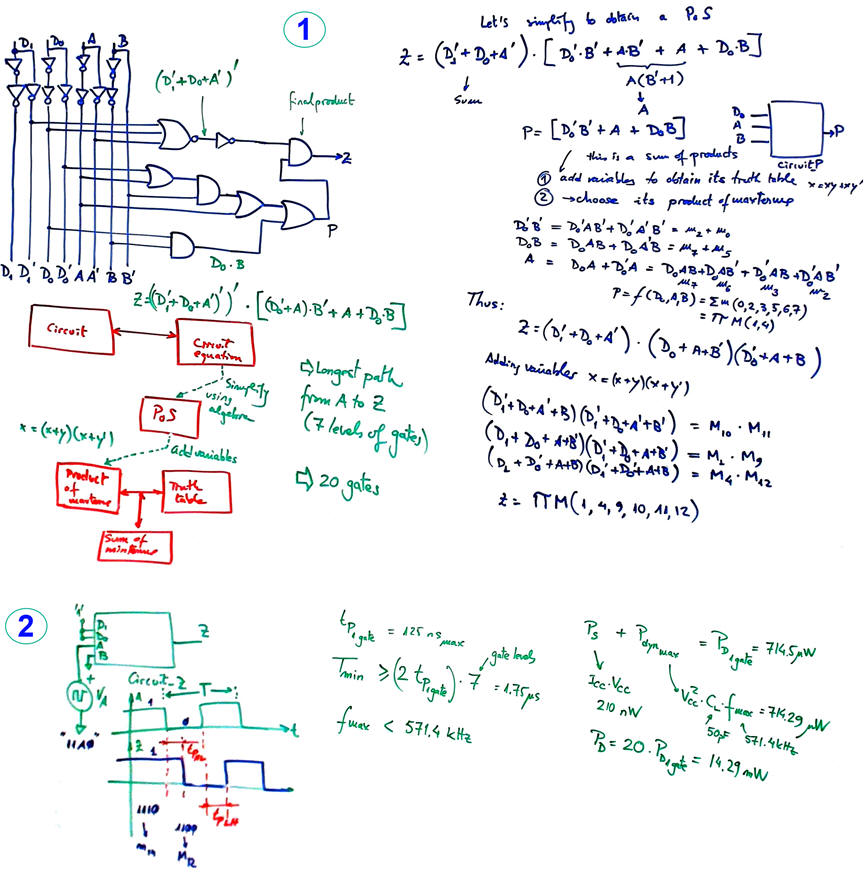

The Circuit_Z is a variation of the highlighted Circuit_C in P1. This is a solution of Circuit_Z using method II. In the slide below a subcircuit Circuit_P is proposed to infer an intermediate result PoS before expanding Z into a product of maxterms. Alternatively, you can expand the expression Z = (D1' + D0 + A')·(D0'·B' + A + D0·B) to be a SoP and thus deduce the sum of minterms instead.

Problem 3 - Problem 4 - Problem 5 - Problem 5

1. The questions are related to PLA2 circuits: D1.10 (bin - Johnson), D1.10 (Johnson - bin), D1.9, D1.7. Use your reports and feedback to write the answers following exactly our conventions.

2. Plan A equations, estrategies (1) - (2) - (3) and (4), are in L1.4 and propagation delay and levels of gates in combinational networks are explained in L4.3. Using canonical sum of minterms or product of maxterms, or minimised SoP or PoS implies 3-levels of gates when the equation is drawn as a logic circuit.

3. How to drive LED is in found in L2.4 and basic electrical characteristics in L1.6. Draw the circuit that is driving the LED in the first place, in order to deduce the LED's bias equation and be aable to apply values from datasheets.

4. Plan B implies drawing an schematic to show how the full truth table is captured in VHDL, or drawing a flowchart to interpret the truth table sections, as explained in LAB2 or in many other products solved using this high-level behavioural plan.

2324Q2 |

Problem 1

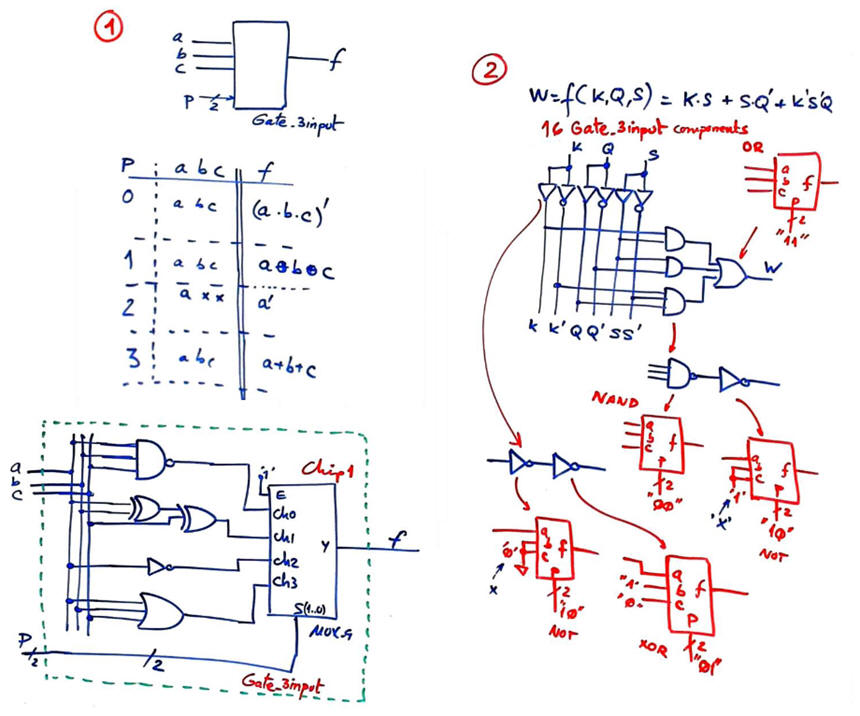

1. Truth table examples of incomplete

functions are found in L2.5.

2. Only-NAND, only-NOR circuits are explained in

L1.5

3. MoM is

explained in L3.3.

4. MoD and decoder expansion examples is

found in

L3.3.

5. Plan B example schematics using capturing the full truth table or

the circuit's flowchart are in

LAB2.

6. Propagation delay and levels of gates in combinational networks

are explained in L4.3.

7. Power consumption is explained in

L4.3.

8. How to drive LED is found in

L2.4 and basic electrical characteristics in

L1.6.

Problem 2

Standard binary encoders using plan A are presented in L2.3 and in this product Enc_10_4.

Problem 3

An example of 8-bit arithmetic circuit for integers in 2C is available at the highlighted project P4.

Problem 4

The programmable gate is another example of circuit that can be solved using plan C2 and the MoM.

2324Q1 |

Problem 1

1. Method 1

on algebraic logic equations from any

P1 project analysis. Solve the

same circuit using the other three methods and compare solutions.

Prob1

circuit in Proteus. Method 3 in

LAB1.2 shows how to

translate equations into VHDL to run synthesis and simulations in

VHDL.

2. Propagation delay: L4.3.

3. Power consumption L4.3 and noise margins

L1.6.

4. Method 1

on algebraic logic equations from any

P1 project analysis.

5. Method 1

on algebraic logic equations from any

P1 project analysis.

6. Only-NAND, only-NOR circuits are explained in

L1.5.

Problem 2

7. 8. This is comparator for radix-2 (L3.1) and two's complement integers (L4.1) proposed in D1.17.

9. 10. How to build chained comparators (L3.2, plan C2) and how to test them can be found in several example tutorial projects: Comp_1bit using the MoM, Comp_4bit, Comp_10bit.

Problem 3

11. Designing circuits using a single-file

flat architecture in Plan B is

studied in L2.3,

LAB2 and and truth table and

flowchart examples are found in many design

tutorials.

12. 13. MoD and decoder expansion examples

is in L3.3.

14. MoM is explained in L3.3.

15. This plan C2 example shows

how to expand multiplexers:

MUX_8

16. How to drive LED is found in

L2.4.

Problem 4

17. 18. 19. The highlighted project

P4 shows the design and

simulation of an adder/subtractor for integer numbers.

20. Gate-level and timing analyser tools are proposed in

LAB4_1. The basics on propagation delays through a chain

of

multiple components is explained in

L4.3.

2223Q2 |

Solution ideas.

2223Q1 |

Example solutions.

2122Q2 |

Example solutions Prob1, Prob2.

2122Q1 |

Example solutions. Prob1 and Prob4 in Proteus.

2021Q2 |

Example solutions. Prob1 in Proteus.

2021Q1 |

Example solutions.

1920Q1 |

Example solutions.

1819Q2 |

Example solutions (Prob. 1 option B is here as the Circuit_Q).

1819Q1 |

1718Q2 |

Discussed solution. This is the Problem 1 truth table in Minilog format.

1718Q1 |

Proteus simulation to experiment the way it works, and a possible solution. The Gray_Bin_Converter (Chip1) in Minilog format.

16174Q2 |

PDF that contains many concepts develop since now through P1 .. P4. This is the Proteus file, the truth table in Minilog and the results when simplifying by PoS.

PDF (r). The truth table and the symbol in Proteus that can be simulated attaching this "jed" to the AM22V10 sPLD. This is a VHDL file using plan B (question 5), and this is the ispLEVER Classic report where you see the pin connections after synthesising the circuit.