UPC. EETAC. Bachelor's degree. 2A. Digital Circuits and Systems (<u>CSD</u>). **Exam 1.** Grades available by 7<sup>th</sup> November. Questions about exams and corrections: <u>office time.</u> **31**<sup>st</sup> October

(Problem 1) and (Problem 2) and [(Problem 3) or (Problem 4) or (Problem 5) or (Problem 6)]

### Problem 1

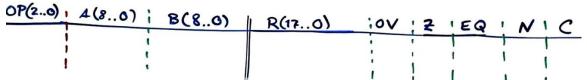

The *ALU\_9bit* shown in Fig. 1a was used in our LAB4\_2 as an example of prototyping and final implementation configuring a target FPGA and designing printed circuit boards (PCB).

Complete the eight operations in binary for the following operands indicating as well the flag values (check your results in decimal when possible):

A = "011111111"; B = "100000001"

- 2. The circuit, designed internally using plan C2 contains several chips and logic circuits; one of them is the chip Int\_Add\_Subt\_9bit, as shown in Fig. 1b, to perform additions and subtractions of 9-bit integer numbers in 2C. Draw a sketch plan for this component. How many VHDL files will include this component?

- **3.** Another component that we can find is the *Adder\_1bit*. Design it using plan C2 and the MoD.

- 4. Design again the Adder\_1bit using plan C2 and the MoM including a MUX\_8 and a MUX\_2.

Fig. 1. a) 9-bit arithmetic and logic unit; b) one of its internal chips used for performing arithmetic operations.

(4p)

## Problem 2

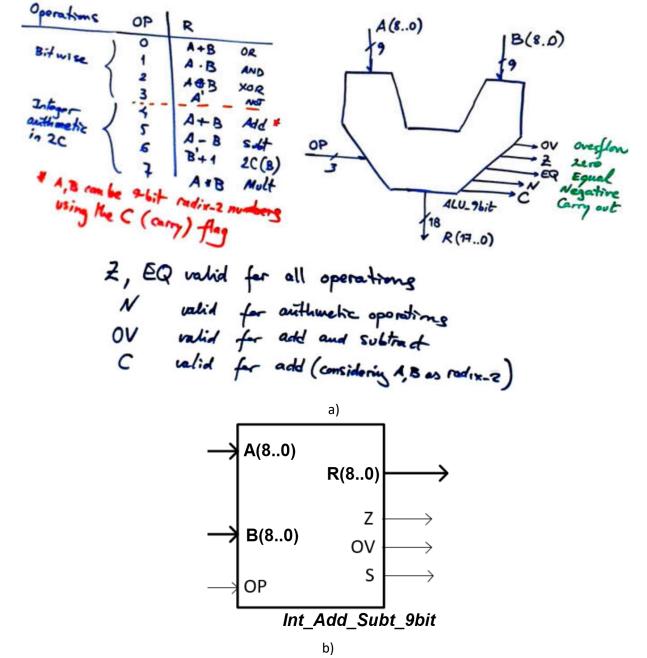

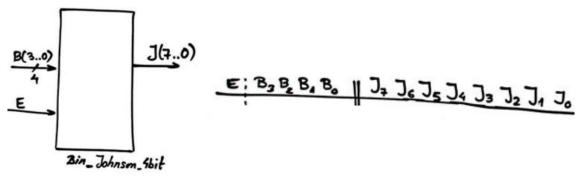

- 1. Analyse the circuit in Fig. 1 using method I to obtain its truth table Z = f(D1, D0, A, B). Firstly, explain your plan and the concepts and procedures involved in the deduction.

- 2. What is the circuit's power consumption running at the maximum speed if implemented using CMOS gates?

### Problem 3

(4p)

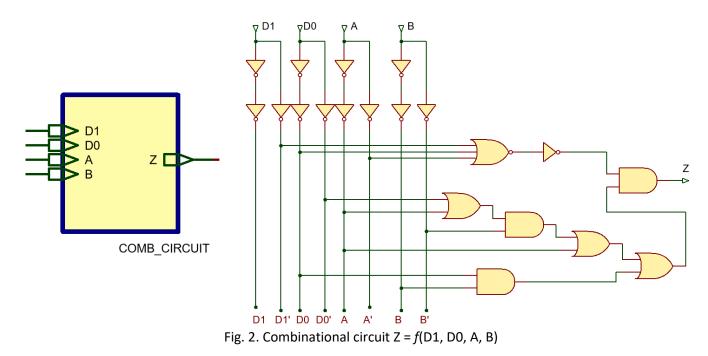

For the 4-bit binary radix-2 to Johnson code converter in Fig. 3 with enable input, answer the following questions:

- 1. Complete the truth table. Obtain the canonical equations for  $J_7$  and  $J_5$ .

- **2.** If the circuit is solved completely using plan A, CMOS gates and canonical equations, calculate its propagation delay and maximum speed of operation.

- **3.** Connect LED active-low at each circuit output ( $V_{AKQ}$  = 2.1 V). Calculate the limiting resistors to drive each LED with 700 µA in the worst-case scenario using CMOS logic.

- 4. Describe the schematic or flowchart to be able to translate the truth table into VHDL using plan B.

# Problem 4

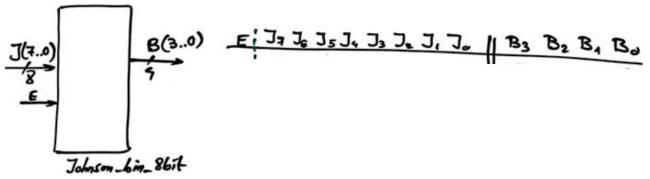

For the 8-bit Johnson to binary radix-2 converter with enable input represented in in Fig. 4, answer the following questions:

- 1. Complete the truth table. Obtain the canonical equations for B<sub>3</sub> and B<sub>1</sub> indicating the terms of no interest as don't care values.

- 2. If the circuit is solved completely using plan A, LS-TTL gates and simplified equations SoP or PoS from Minilog, calculate its propagation delay and maximum speed of operation.

- Connect LED active-high at each circuit output (V<sub>AKQ</sub> = 1.9 V). Calculate the limiting resistors to drive each LED with 3.9 mA in the worst-case scenario using LS-TTL logic.

- 4. Describe the schematic or flowchart to be able to translate the truth table into VHDL using plan B.

# Problem 5

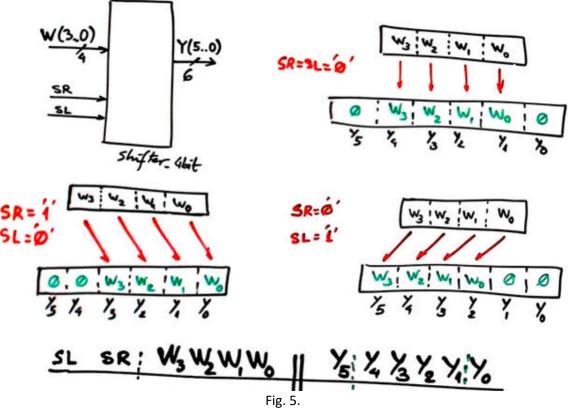

For the 4-bit (nibble) shifter operator circuit represented in Fig. 5, controlled by shift-right (SR) and shift-left (SL) signals, answer the following questions:

- **1.** Complete its truth table indicating its four sections. Write the list of minterms of Y<sub>3</sub> and Y<sub>2</sub> when in shift-right mode. What combinations generate incomplete functions because they are of no interest?

- 2. If the circuit is solved completely using plan A, CMOS gates and simplified equations SoP or PoS from Minilog, calculate its propagation delay and maximum speed of operation.

- **3.** Connect LED active-high at each circuit output ( $V_{AKQ}$  = 1.85 V). Calculate the limiting resistors to drive each LED with 350 µA in the worst-case scenario CMOS logic.

- 4. Describe the schematic or flowchart to be able to translate the truth table in VHDL using plan B.

(4p)

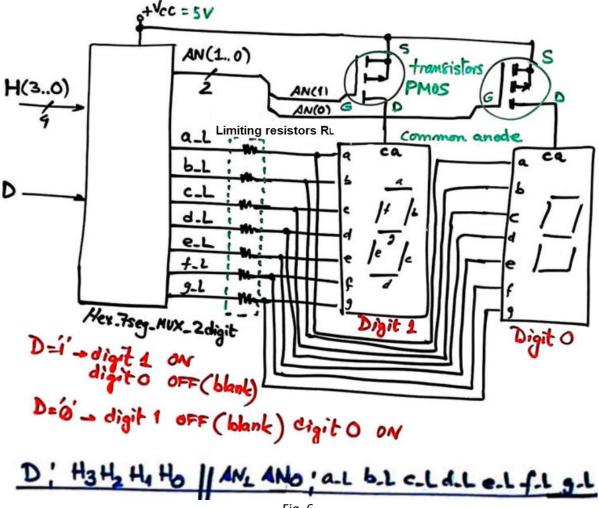

## Problem 6

For the 2-digit multiplexed 7-segment display shown in Fig. 6, answer the following questions:

- 1. Complete the truth table. Obtain the canonical equations  $AN_1$  and  $AN_0$ .

- **2.** If the circuit is solved completely using plan A, LS-TTL gates and canonical equations, calculate its propagation delay and maximum speed of operation.

- Calculate the limiting resistors to drive each LED (V<sub>AKQ</sub> = 2.23 V) segment with 2.5 mA in the worst-case scenario using LS-TTL logic.

- 4. Describe the schematic or flowchart to be able to translate the truth table in VHDL using plan B.

Fig. 6.

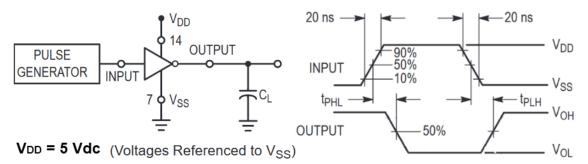

Fig. 7 shows the electrical characteristics of a single logic gate in classic CMOS and LS-TTL technologies.

| MC14069UB                                                                                                                        | Symbol          |                                        |                      |                 |      |      |

|----------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------------------------------|----------------------|-----------------|------|------|

|                                                                                                                                  |                 | -                                      | Min                  | Тур             | Мах  | Unit |

| Output Voltage V <sub>in</sub> = V <sub>DD</sub>                                                                                 | "0" Level       | V <sub>OL</sub>                        |                      | 0               | 0.05 | Vdc  |

| V <sub>in</sub> = 0                                                                                                              | "1" Level       | V <sub>OH</sub>                        | 4.95                 | 5.0             |      | Vdc  |

| Input Voltage<br>(V <sub>O</sub> = 4.5 Vdc)                                                                                      | "0" Level       | V <sub>IL</sub>                        | _                    | 2.25            | 1.0  | Vdc  |

| (V <sub>O</sub> = 0.5 Vdc)                                                                                                       | "1" Level       | V <sub>IH</sub>                        | 4.0                  | 2.75            | _    | Vdc  |

| Output Drive Current<br>(V <sub>OH</sub> = 2.5 Vdc)<br>(V <sub>OH</sub> = 4.6 Vdc)                                               | Source          | I <sub>OH</sub>                        | - 2.4<br>- 0.51      | - 4.2<br>- 0.88 | _    | mAdc |

| (V <sub>OL</sub> = 0.4 Vdc)                                                                                                      | Sink            | I <sub>OL</sub>                        | 0.51                 | 0.88            | _    | mAdc |

| Input Current                                                                                                                    | l <sub>in</sub> | —                                      | ±0.00001             | ± 0.1           | μAdc |      |

| Input Capacitance (V <sub>in</sub> = 0)                                                                                          |                 | C <sub>in</sub>                        | —                    | 5.0             | 7.5  | рF   |

| Quiescent Current (Pe                                                                                                            | r Gate)         | I <sub>DD</sub>                        | —                    | 0.084           | 42   | nAdc |

| Total Supply Current (C <sub>L</sub> = 50 pF)<br>(Dynamic plus Quiescent(Per Gate)                                               |                 | Ι <sub>Τ</sub>                         | I <sub>T</sub> = (0. | μAdc            |      |      |

| Propagation Delay Times<br>(C <sub>L</sub> = 50 pF)<br>t <sub>PLH</sub> , t <sub>PHL</sub> = (0.90 ns/pF) C <sub>L</sub> + 20 ns |                 | t <sub>PLH</sub> ,<br>t <sub>PHL</sub> | _                    | 65              | 125  | ns   |

$$P_S + P_{dyn} = I_{DDQ} \cdot V_{DD} + V_{DD}^2 \cdot C_L \cdot f$$

Fig. 7. Characteristics of a logic gate in CMOS technology

# Fig. 8 shows the characteristics of a single logic gate in LS-TTL technology.

| Symbo                                     | Parameter                        |                                                | Μ                                               | in    | Nom          | Мах     | (U   | nits  |        |     |

|-------------------------------------------|----------------------------------|------------------------------------------------|-------------------------------------------------|-------|--------------|---------|------|-------|--------|-----|

| V <sub>CC</sub> Supply Voltage            |                                  | 4.                                             | 75                                              | 5     | 5.25         | ;       | V    | 74L   | S04    |     |

| V <sub>IH</sub> HIGH Level Input Voltage  |                                  | 1                                              | 2                                               |       |              |         | V    |       |        |     |

| V <sub>IL</sub> LOW Level Input Voltage   |                                  |                                                |                                                 |       | 0.8          |         | V    |       | ≫—     |     |

| I <sub>OH</sub> HIGH Level Output Current |                                  |                                                |                                                 |       | -0.4         | - I     | mA   |       |        |     |

| I <sub>OL</sub> LOW Level Output Current  |                                  |                                                |                                                 |       | 8            |         | mA   |       |        |     |

| Symbol                                    | Parameter                        |                                                | Conditions                                      |       |              | Min     | Тур  | Мах   | Units  |     |

| VI                                        | Input Clamp Voltage              | $V_{\rm CC} = Min, I_{\rm I} = -18 \text{ mA}$ |                                                 |       |              |         |      | -1.5  | V      |     |

| V <sub>OH</sub>                           | HGH Level                        |                                                | $V_{CC} = Min, I_{OH} = Max,$<br>$V_{IL} = Max$ |       |              |         | 2.7  | 3.4   |        | V   |

|                                           | Output Voltage                   |                                                |                                                 |       |              |         |      |       | v      |     |

| V <sub>OL</sub>                           | LOW Level                        | $V_{CC} = Min, I_{OL} = Max,$                  |                                                 |       |              |         | 0.35 | 0.5   |        |     |

|                                           | Output ∀oltage                   |                                                | $V_{IH} = Min$                                  |       |              |         |      | 0.00  | 0.5    | V   |

|                                           |                                  |                                                | $I_{OL} = $                                     | 4 mA, | $V_{CC} = N$ | /lin    |      | 0.25  | 0.4    | •   |

| Ц                                         | Input Current @ Max              |                                                | $V_{CC} = Max, V_I = 7V$                        |       |              |         |      |       | 0.1    | mA  |

|                                           | Input Voltage                    |                                                |                                                 |       |              |         |      |       |        |     |

| IIН                                       | HIGH Level Input Current         | $V_{CC} = Max, V_I = 2.7V$                     |                                                 |       |              |         |      | 20    | μA     |     |

| Ι <sub>ΙL</sub>                           | LOW Level Input Current          | $V_{CC} = Max, V_I = 0.4V$                     |                                                 |       |              |         |      | -0.36 | mA     |     |

| los                                       | Short Circuit Output Current     | V <sub>CC</sub> = Max                          |                                                 |       |              | -20     |      | -100  | mA     |     |

| ICCH                                      | Supply Current with Outputs HI   | V <sub>CC</sub> = Max                          |                                                 |       |              |         | 1.2  | 2.4   | mA     |     |

| I <sub>CCL</sub>                          | Supply Current with Outputs LC   | V <sub>CC</sub> = Max                          |                                                 |       |              |         | 3.6  | 6.6   | mA     |     |

| Symbol                                    | Parameter C <sub>L</sub> = 50 pF | Min                                            | Мах                                             | Units | 5            |         |      |       | Vcc    |     |

|                                           | Propagation Delay Time           |                                                | 15                                              |       |              | PULSE   |      |       |        | TUT |

|                                           | LOW-to-HIGH Level Output         | 4                                              | 15                                              | ns    |              | NERATOR | IN   | IPUT  | $\sim$ |     |

|                                           | Propagation Delay Time           | 4                                              | 4-                                              | ns    | -            |         |      | 7     | GND    | Ť٩  |

|                                           | HIGH-to-LOW Level Output         |                                                | 15                                              |       |              |         |      | -     | ÷      | ÷   |

Fig. 8. Characteristics of a logic gate in LS-TTL technology

**NOTE** for all problems and questions: draw circuits, sketches or diagrams, explain as clear as possible what you do and how you are inventing circuits or processing calculations. Justify your results.