|

|

|||||

Chapter 1 problems |

- D1.9 - |

4-bit (nibble) shifter operator |

|||

|

|

|||||

1.- Specifications

In digital systems it is often necessary to have circuits that can shift the bits of a vector by one or more bit positions to the left or right.

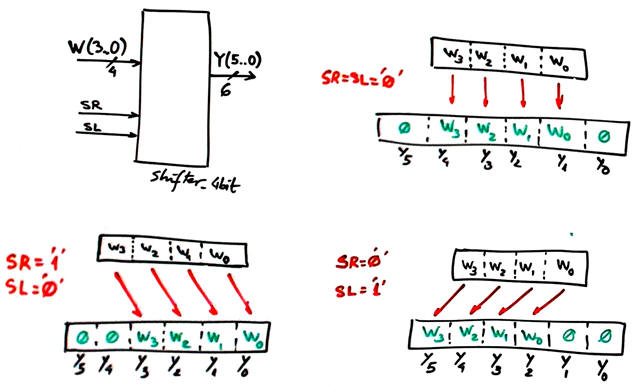

Design a circuit that can shift a 4-bit vector W(3..0), also called nibble, one bit position to the right when a control signal SR = '1', and one bit position to the left when SL = '1'. When the control signals are not active SR = '0', SL = '0', the output is a copy of the vector W. We dont'care about the output values if by any chance both control signals are activated SR = '1', SL = '1'; assuming that this condition will nevel occur. The simbol and operations of this device are represented in Fig. 1.

|

Fig.1. Symbol of the Shifter_4bit. |

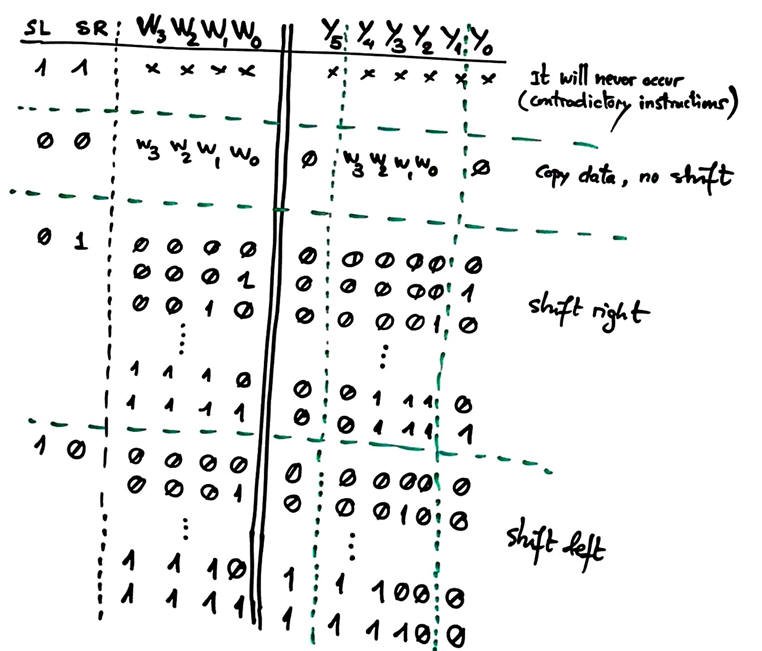

Complete the circuit's truth table sketched in Fig. 2.

|

Fig.1. Truth table idea. |

Draw an example of timing diagram to be used later as stimulus in the VHDL testbench when verifying the synthesised circuit. Consider Min_Pulse = 2.45 ms.

The same project B3.9 is proposed in Chapter 3 for learning the basics of μC software organisation and basic digital I/O.

CPLD or FPGA target chip options:

Target option #1.: MAX II

Target option #2.: MAX 10

Target option #3.: Cyclone IV

2. Planning

Plan A structural circuit based on logic gates and equations in a single VHDL file. We have many strategies, for instance:

option #1: use minilog to obtain PoS.

Project location:

C:\CSD\P2\Shifter_4bit_PoS\(files)

How many FPGA resources (logic cells, logic elements, etc.) are used? What is the percentage of the target chip used in this design?

option #2: use minilog to obtain SoP.

Project location:

C:\CSD\P2\Shifter_4bit_SoP\(files)

How many FPGA resources (logic cells, logic elements, etc.) are used? What is the percentage of the target chip used in this design?

Plan B behavioural approach writing the truth table or the high-level description or algorithm in VHDL in a single file (flat).

Project location:

C:\CSD\P2\Shifter_4bit_B\(files)

How many FPGA resources (logic cells, logic elements, etc.) are used? What is the percentage of the target chip used in this design?

After having studied P4 tutorials, additional questions can be added to our report. For instance:

-

Perform a gate-level simulation to measure propagation delays in a given signal transition.

-

Deduce the worst-case propagation delay running the timing analiser tool and calculate the circuit's maximum frequency of operation for the target chip used in the design.