|

Laboratory |

Laboratory 3: Multiple-file (plan C2) structural VHDL designs: Adder_1bit, Adder_8bit This highlighted Ones_counter_8bit [P3] is the reference plan C2 structural hierarchical design |

[10/10] |

|

This is the post lab assignment PLA3 to be submitted at Atenea before the due date. Study in detail and execute in your computer this lab tutorial and the reference design before attempting to solve the PLA. |

1.5.2.4. Plan C2: hierarchical design multiple-file (components and signals)

Learning how to use components is the key point of the CSD course because it will allow you to invent large circuits hierarchically, as you see in Proteus schematics, where you can go "Cntl+C" to the child sheet of each subcircuit. Thus, from now on, subcircuits will become components and wires and cables signals.

1.5.2.4.3. The method of multiplexers (L3.3)

1.9. Binary (radix-2) arithmetic circuits

1.9.1. Addition

1.9.1.1. 1-bit full adder block: Adder_1bit plan C2 MoM

| 1. Specifications | Planning | Developing | Testing | Report |

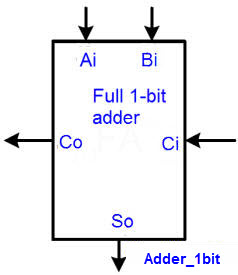

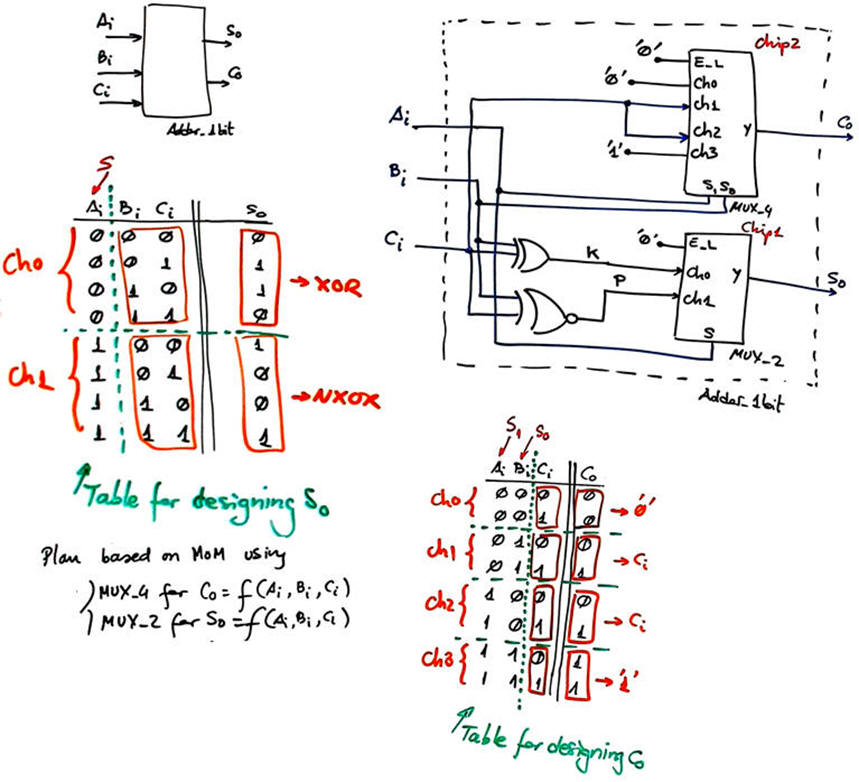

Design a 1-bit adder using plan C2 and the method of multiplexers MoM using a MUX_2 for So and a MUX_4 for Co.

|

|

Fig. 1. Symbol and truth table of 1-bit adder circuit (full adder). |

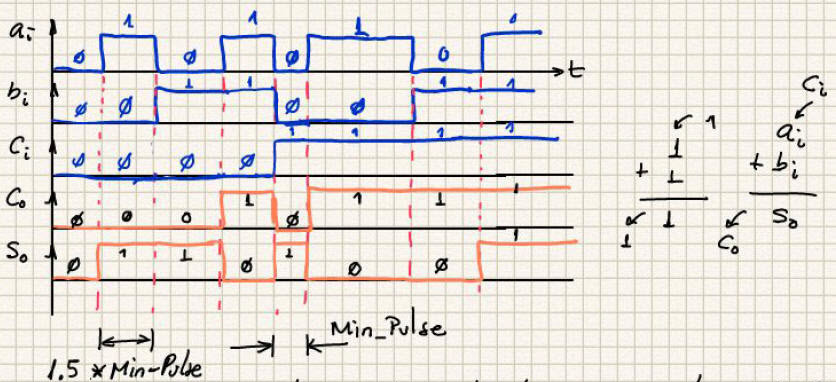

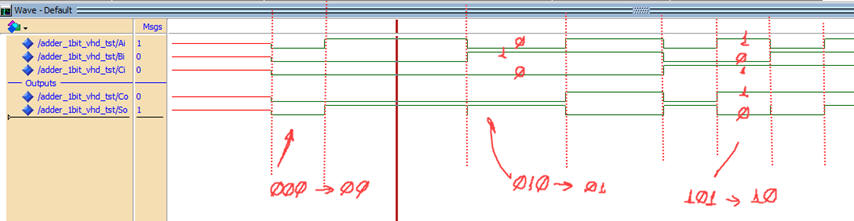

Fig. 2 is a sketch that represents the truth table in time. The idea of applying input vectors that can be any binary combination.

|

| Fig. 2. Timing diagram where all the inputs are applied sequentially and hence, the output is predicted accordingly to the truth table. |

| Specifications | 2. Planning | Developing | Testing | Report |

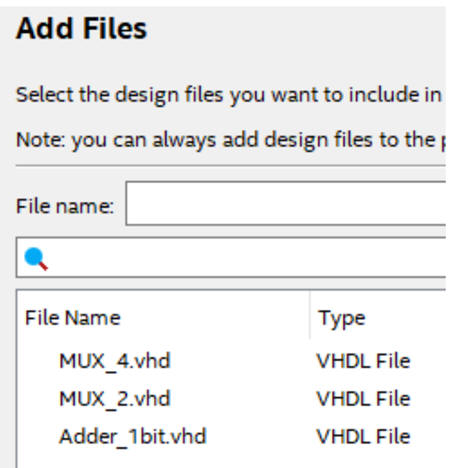

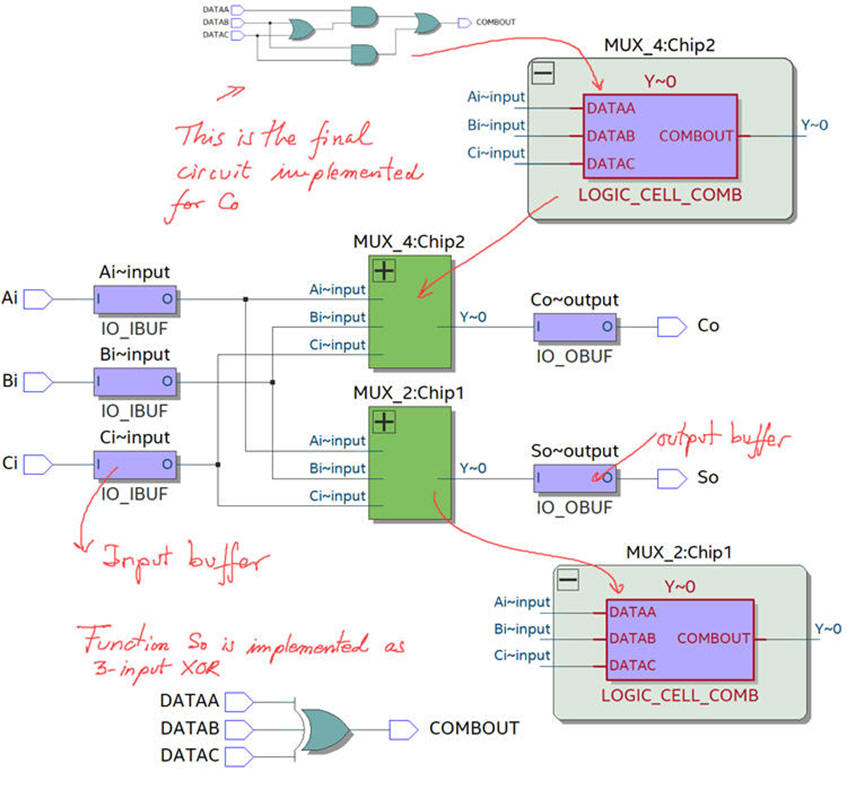

We will conceive all our circuits using VHDL EDA tools and following the design flow. Fig. 3 shows the internal architecture of the Adder_1bit based on the MoM and using specifically a MUX_4 for Co and a MUX_2 for So.

|

| Fig. 3. Plan proposed in this project. |

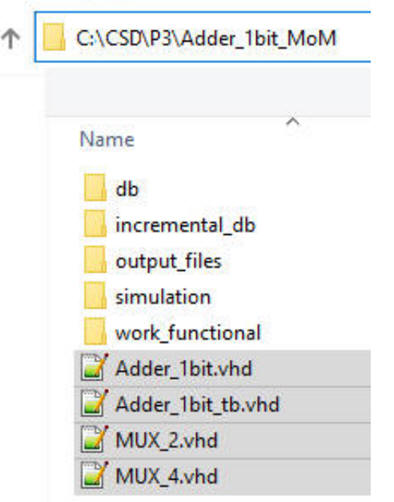

Project location:

C:\CSD\P3\Adder_1bit_MoM\(files)

Alternatively, we can propose a plan using MUX_2 for both outputs. Or another plan using MUX_4 for both outputs. Or yet another way: how can you design the circuit using MUX_8?

| Specifications | Planning | 3. Developing | Testing | Report |

This Adder_1bit.vhd is the translation of the circuit in Fig. 3 above.

The components have their own translation to VHDL, for instance: MUX_4.vhd (using plan A adapted from this MUX_8 tutorial in Lab2), MUX_2.vhd (using plan B adapted from this tutorial in Lab2).

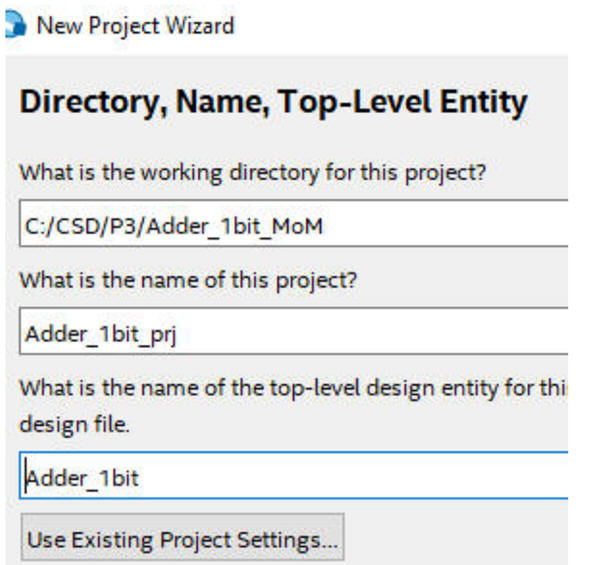

Implement a new synthesis project uisng Quartus Prime for a given Intel target chip: FPGA Cyclone IV EP4CE115F29C7.

|

| Fig. 4. New project. |

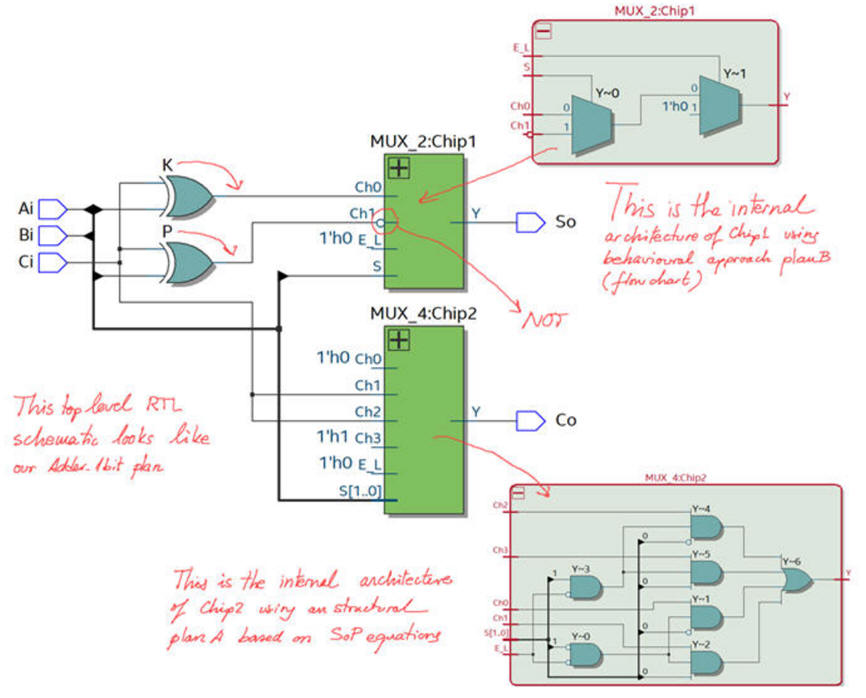

Add all the VHDL files that define the plan C2 architecture before synthesising the project.

|

| Fig. 5. Adding files. |

Print and discuss RTL and technology circuits.

|

| Fig. 6. RTL circuit. |

How many chip resources (logic cells) are used? Why technology circuit (the real circuit implemented into the target chip differs from the ideal RTL circuit written in VHDL?

|

| Fig. 7. Technology circuit. |

| Specifications | Planning | Developing | 4. Testing | Report |

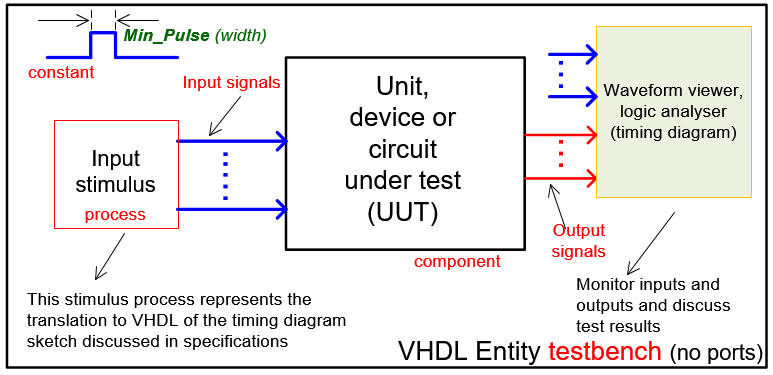

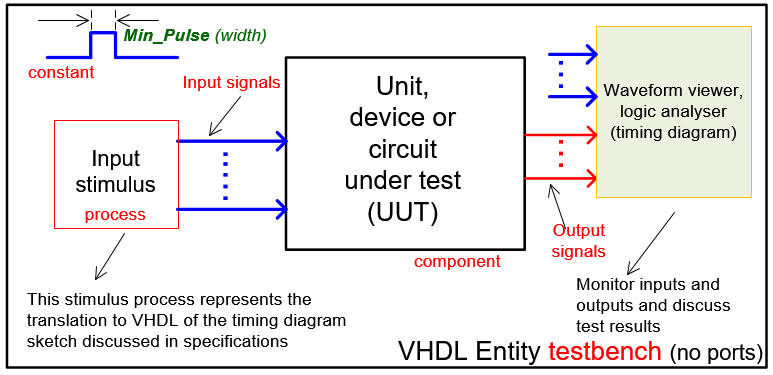

Draw a testbench fixture. We will simulate in ModelSim a VHDL testbench for the unit-under-test.

|

| Fig. 8. Testbench VHDL fixture schematic for performing functional and gate-level tests. |

Generate the VHDL skeleton in Quartus Prime. Translate it to a testbench file. This is an example of testbench file Adder_1bit_tb.vhd from which you can copy only the stimulus process and the constant Min_Pulse. For instance Min_Pulse = 3.55 ms for referencing time. Remember that from testing point of view, even if you have designed the Adder_1bit using several plans, you can use all the time the same testbench.

Generate a new functional simulation project in ModelSim considering all the structural VHDL files and the top testbench.

|

| Fig. 9. VHDL structural files. |

Run enough time (for example, run 710 ms = 200* Min_Pulse) and interpret simulation results printing and commenting waveforms.

|

| Fig. 10. Results. |

| Specifications | Planning | Developing | Testing | 5. Report |

Follow this rubric for writing reports.

|

Laboratory |

Laboratory 3: Multiple-file (plan C2) structural VHDL designs: Adder_1bit, Adder_8bit This highlighted Ones_counter_8bit [P3] is the reference plan C2 structural hierarchical design |

[10/10] |

1.5.2.4. Plan C2: hierarchical design multiple-file (components and signals)

1.5.2.4.1. Circuit expansion using components of the same kind

1.9.1. Addition

1.9.1.2. n-bit adders

1.9.1.2.1. Ripple-carry adder: {Adder_4bit}, {Adder_8bit}

| 1. Specifications | Planning | Developing | Testing | Report | Prototype |

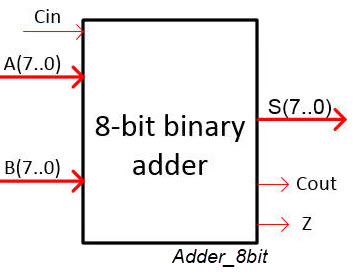

Using VHDL design plan C2, invent an 8-bit binary adder (Adder_8bit) based on simpler chips of the same kind like 4-bit (Adder_4bit) and 1-bit (Adder_1bit) adders. Synthesise it for a target CPLD/FPGA device and test it using VHDL EDA tools.

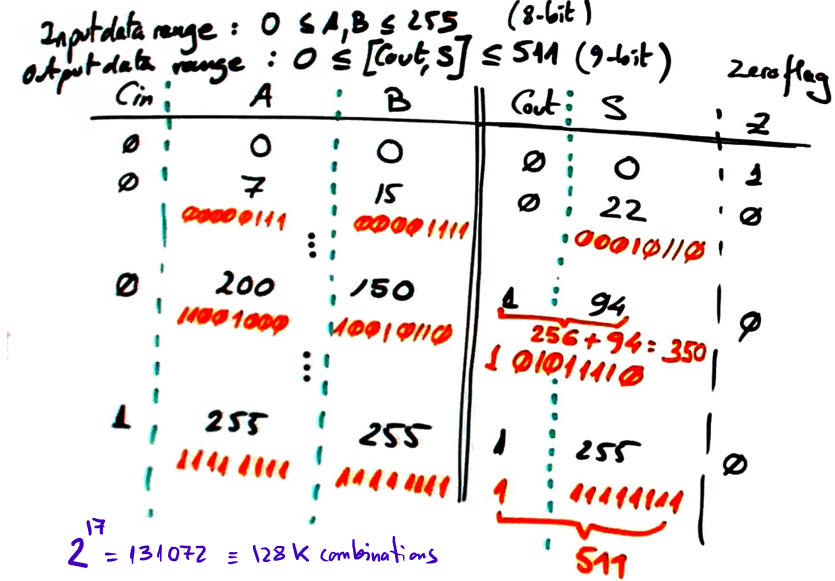

Circuit symbol is represented in Fig. 1 along with its truth table and a sketch of timing diagram.

| |

Fig. 1. a) Symbol of an 8-bit binary adder Adder_8bit (Visio). This is a project Adder_8bit in Proteus. Run it for several input vectors and visualise output results. Examine the commercial chip 74HCT283. |

|

|

| b) Adder_8bit truth table example values. |

|

|

|

|

c) Timing diagram sketch showing how

the Adder_8bit performs several

8-bit additions. It is ready for translation as a VHDL

testbench stimulus process. |

|

| Specifications | 2. Planning | Developing | Testing | Report | Prototype |

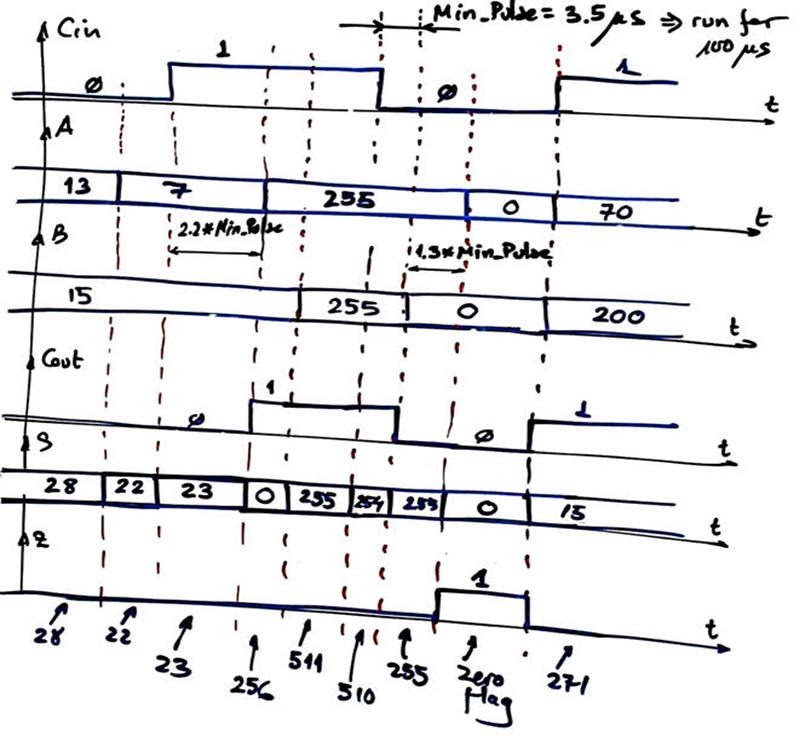

Plan C2 design flow.

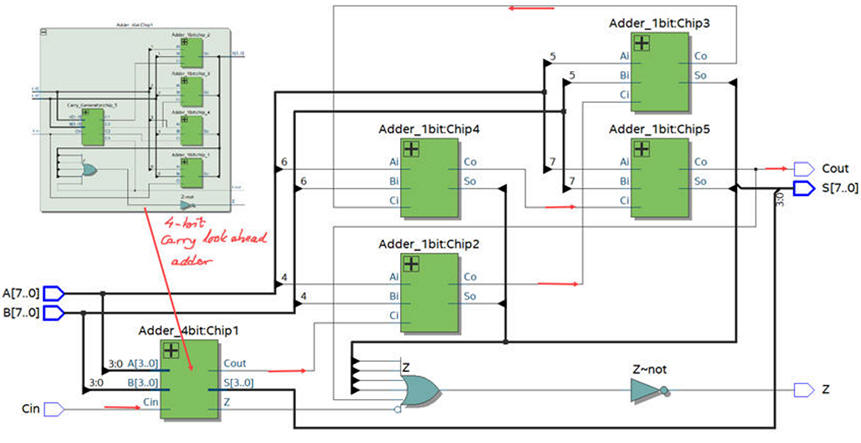

Fig 2 shows the proposed architecture for the Adder_8bit, where several components are interconnected rippling carry signals. Logic gates are also used to implement Z output.

|

| Fig. 2. Planning the circuit using several components of the same kind. |

Project location:

C:\CSD\P3\Adder_8bit\(files)

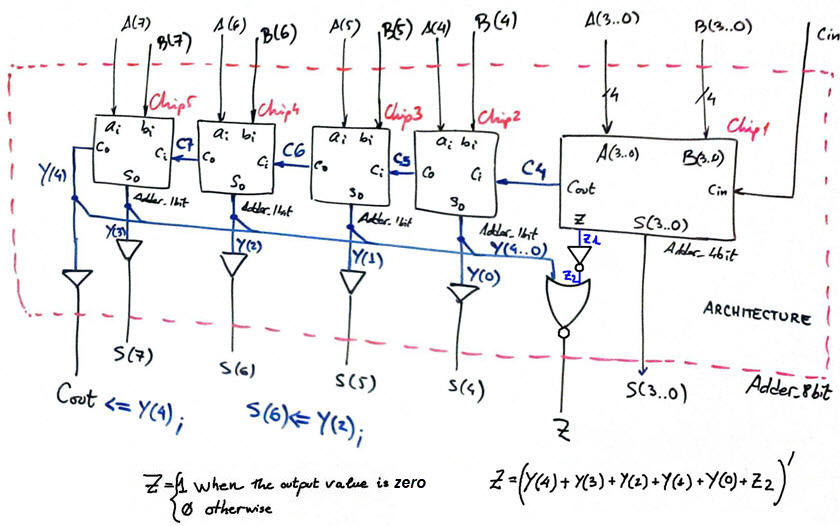

| Specifications | Planning | 3. Developing | Testing | Report | Prototype |

We can complete the project Adder_8bit translating the plan C2 schematic in Fig. 2 in this way: Adder_8bit.vhd.

Before developing this plan, we must copy component VHDL files from other tutorials (see annex below) and paste them in the project's folder.

Run the EDA tool to synthesise the circuit for a given CPLD or FPGA chip. Remember that all the component files have to be also included in the same hierarchical project.

|

| Fig. 3. Files included in this structure. |

Print and comment the RTL schematic.

|

| Fig. 4. Example of RTL diagram schematic interpreted by the EDA synthesis tool. |

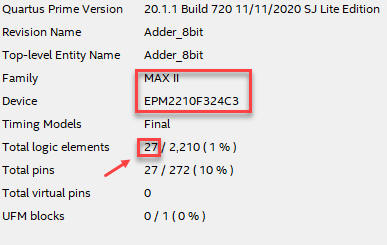

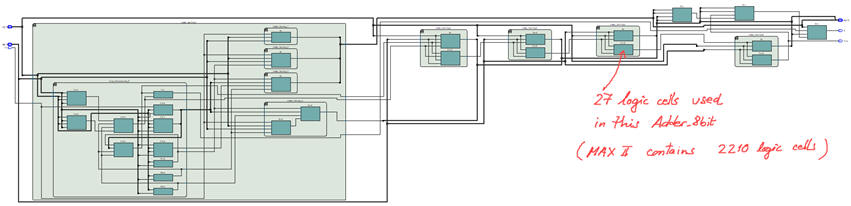

Print and comment the technology schematic. How many resources (logic cells) are used?

|

| Fig. 5. Example of technology implementation in MAXII CPLD. 27 logic elements are required. |

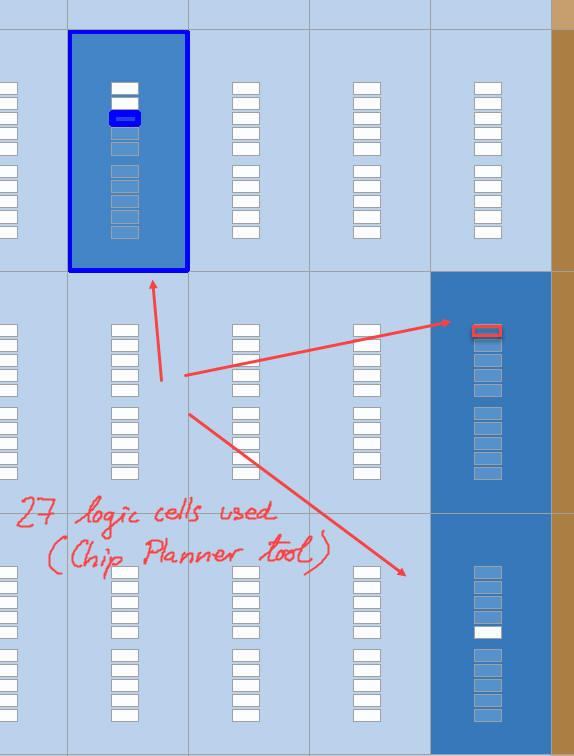

Chip planner tool can be used to pinpoint exactly where the synthesised circuit is placed in the chip fabric.

|

|

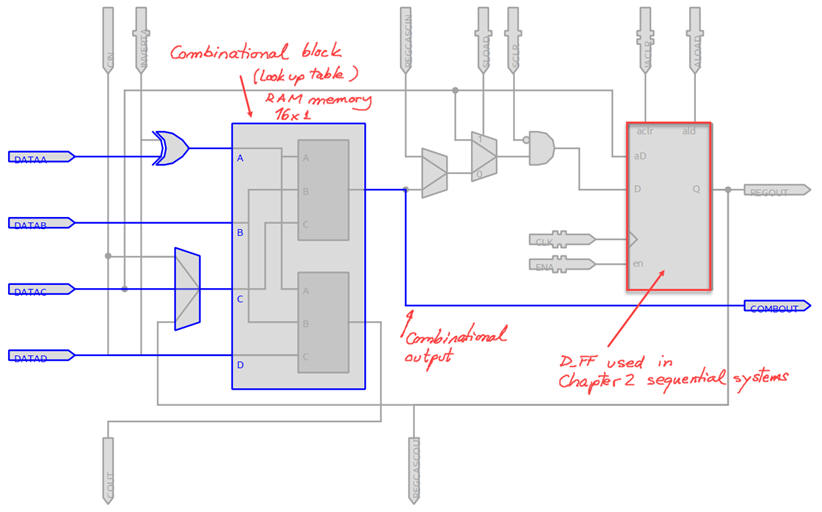

Fig. 6. Chip planner allows to observe the exact location in the chip where the logic is implemented. Detail of a logic cell where only the combinational LUT is used for implementing the truth table. |

| Specifications | Planning | Developing | 4. Testing | Report | Prototype |

Draw the testbench fixture containing the main ideas and concepts involved in this schematic as shown in Fig. 7.

|

| Fig. 7. Testbench VHDL fixture schematic for performing functional and gate-level tests. |

Generate the template of the testbench in Quartus Prime. This is translating into VHDL the schematic in Fig. 7. Rename it and move it to the project folder. Delete the empty process.

Translate the stimulus signals into a process and set the constant Min_Pulse in Fig. 1c. This is a VHDL testbench example file Adder_8bit_tb.vhd from which you can copy only the stimulus process and Min_Pulse constant.

Start an EDA VHDL functional simulation project to verify the device-under-test (DUT) using the test bench.

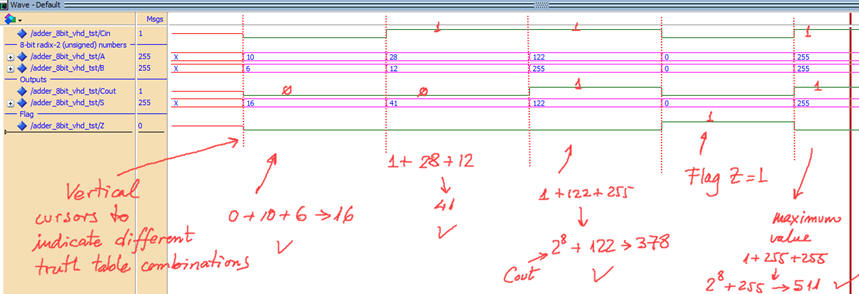

Run simulations and demonstrate how the circuit works adding handwritten comments to the printed sheet of paper containing the waveforms. Vertical cursors are required to separate the different truth table combinations under test.

|

| Fig. 8. Analysing results from functional simulation of the Adder_8bit. |

| Specifications | Planning | Developing | Testing | 5. Report | Prototype |

It is required a handwritten original project report containing sections 1 - 2 - 3 - 4, scanned figures with annotations, file listings, diagrams, sketches or any other resources. Theory and other materials to comprehend how the circuit works may be included in section 1 on specifications. Annexes be included to describe the components used in the planning.

Follow this rubric for writing reports.

Components used in this Adder_8bit, can be reported as annexes.

The idea of technical report at this level has to be clear for you now: a document that demonstrates the way you have designed a given product. Furthermore, it allows you to prepare an oral presentation because it includes everything to generate slides. Simple class notes and conventional exercises may be right for passing exams, but using your project reports you'll be able to teach your peers as if you had become a class instructor.

| Specifications | Planning | Developing | Testing | Report | 6. Prototype |

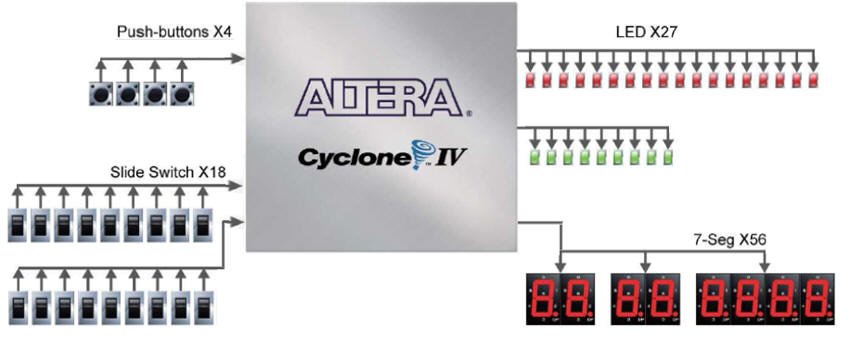

Use training boards and perform laboratory measurements to verify how the circuit being designed works for real.

Example 1. Prototyping Adder_8bit circuit using a Terasic DE2-115 FPGA platform.

|

|

Fig. 8. DE0-115 board representing only simple digital inputs (buttons and switches) and outputs (LED and 7-segments). |

Annexes: Adder_8bit components

Because this design is complex, better if we go step by step bottom-up starting from the most simple component: 1-bit full adder (Adder_1bit) at the same time that we practice plan C2.

Therefore, below is the proposed general organisation to complete our chip Adder_8bit:

Adder_1bit (projects 1 or 2 or 3 or 4) ----> Adder_4bit (projects 5 or 6) ----> Adder_8bit

Annex 1: Adder_1bit projects

To solve this component we present up to four architectures:

Project 1: Let us design the Adder_1bit using plan C2 and the MoM that is explained in L3.3. This is the first project in this lab tutorial.

C:\CSD\P3\Adder_1bit_MoM\(files)

Project 2: Let us design the Adder_1bit using plan C2 and the method of decoders MoD that is explained in L3.3.

C:\CSD\P3\Adder_1bit_MoD\(files)

Project 3: Let us design the Adder_1bit using plan A.

C:\CSD\P3\Adder_1bitA\(files)

Project 4: Let us design the Adder_1bit using plan B.

C:\CSD\P3\Adder_1bitB\(files)

Annex 2: Adder_4bit projects

To solve this component we present two architectures that will have different performance when implemented in a given CPLD chip.

Project 5: Let us design a ripple carry Adder_4bit.

C:\CSD\P3\Adder_4bit_RC\(files)

Project 6: Let us design a carry-lookahead Adder_4bit. This design is similar to the standard chip type 74HCT283.

C:\CSD\P3\Adder_4bit_CLA\(files)

Note: This CLA 4-bit adder version includes two extra outputs (P, G) that may be left unconnected modifying the top schematic in this way: Adder_8bit.vhd.

Optional, additional content beyond CSD. This is another version of Adder_8bit using plan B.