|

Laboratory |

Lab 4.1: propagation delay and speed: Adder_1bit, Adder_16bit (RC), Adder_16bit (CLA) This is the highlighted Int_add_subt_8bit [P4] reference design to study propagation delay using timing analyser and VHDL gate-level simulations |

[17/10] |

|

This is the post lab assignment PLA4.1 to be submitted the next Lab 4.2 session. Study in detail and execute in your computer this lab tutorial and the reference design before attempting to solve the PLA. |

1.5.5.1. Gate-level simulation: propagation delay measurement

How to measure circuit's propagation time for a given target chip: post-synthesis model in VHDL (VHO file and its associated SDO/SDF delay file) and gate-level VHDL simulation.

1.5.5.2. Timing analyser spreadsheet tool

Measuring the worst-case scenario: longest propagation delay (tP).

1.5.5.3. Calculating circuit's maximum speed (fMAX).

In the lab we have some commercial CPLD and FPGA target chips where to synthesise our circuits. For instance:

| CPLD | FPGA | |

| Xilinx | XC2C256-TQ144 - 7 | Spartan-3E XC3S500E-FG320 |

| Intel | MAX II EPM2210F324C3 (option #1) | Cyclone IV EP4CE115F29C7 (option #2) |

| Lattice | ispMach4128V TQFP100 | MachXO |

NOTE: Quartus Prime does not generate delay files (sdo) for Intel MAX 10 devices, and thus we cannot practise gate-level simulations in ModelSim for this family.

| 1. Specifications | Planning | Developing | Functional test | Gate-level test | Report | Prototype |

Let us continue Adder_1bit based on MoM from Lab3 measuring propagation time of signals in a given transition and maximum speed of computing.

Two new tools will be presented:

-

(1) ModelSim gate-level simulations for measuring propagation delays in a given signal transition.

-

(2) Quartus Prime timing analyser for calculating the worst-case scenario (longest propagation delay).

The objective is to find what target chip is faster when implementing the same project Adder_1bit:

-

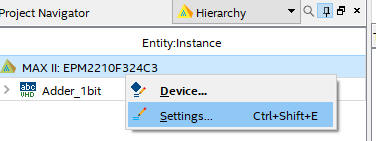

Option #1: MAXII device EPM2210F324C3

-

option #2: Cyclone IV EP4CE115F29C7

Firstly, we will solve the project for chip option #1 and annotate results. Secondly, keeping the same project, we will change the target chip to option #2 and annotate results. We will discuss solutions.

| Specifications | 2. Planning |

| 3. Developing |

| 4. Functional test | Gate-level test | Report | Prototype |

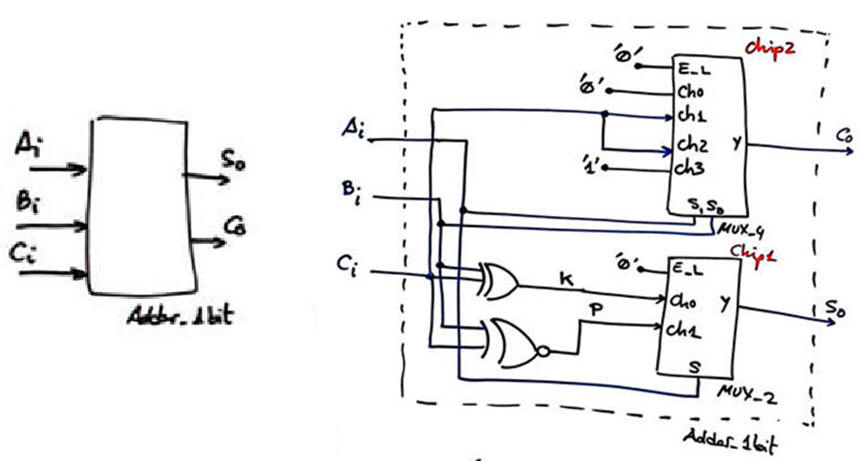

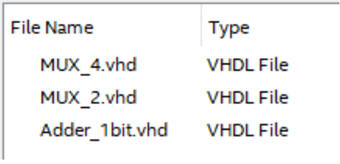

The Adder_1bit specifications and also the three next sections #2 -#3 -#4 are already implemented in the previous Lab3. Our circuit is running correctly and we can visualise functional simulations. This, we can start a new Quartus Prime project copying the source VHDL files (Adder_bit.vhd, MUX_2.vhd, MUX_4.vhd) and the testbench files (Adder_1bit_tb.vhd, wave.do) from Lab3 to this new location:

C:\CSD\P4\Adder_1bit_MoM\(files)

|

| Fig. 1. The plan for inventing the Adder_1bit is the same from LAB3. |

Select the option #1 MAX II target device and synthesise the circuit.

|

Fig. 2. Plan C2 source files from Lab3. |

Be sure that you check the RTL and technology view as you did in Lab3 Fig. 6 and Fig. 7.

Check that you've got the same functional test results as in Lab3 and Fig. 10 when using the same VHDL testbench fixture Adder_1bit_tb.vhd. Use the same wave.do for setting up the signals of interest in the wave diagram.

| Specifications | Planning | Developing | Functional test | 5. Gate-level test | Report | Prototype |

Gate-level VHDL simulation of the technology schematic

Let us use the new tools that will allow us to characterise better the real circuit implemented in the FPGA. This is our tutorial on gate-level simulation and the timing analyser tool in case you needed it even before running this tutorial.

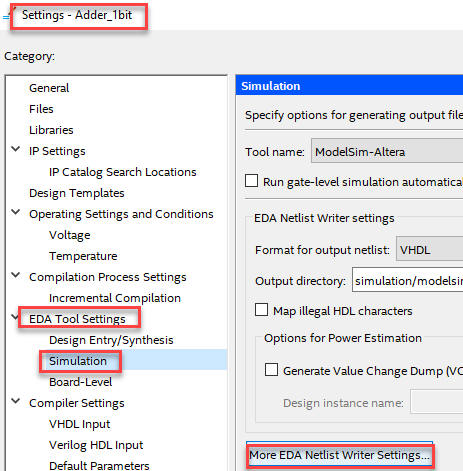

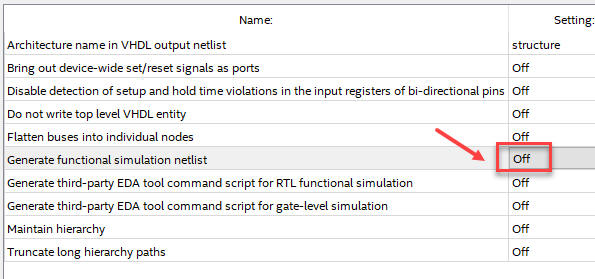

Set the following project parameters before re-synthesising your project and be able to generate the necessary VHO and SDO files for the target chip:

|

| Fig. 4. Parameters for letting Quartus Prime generate delay files. |

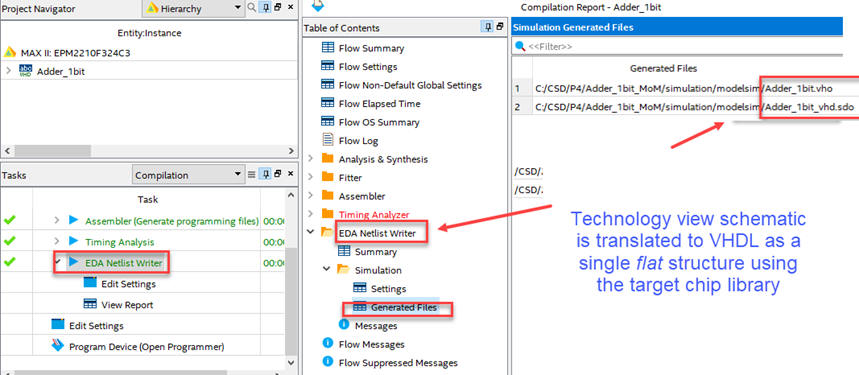

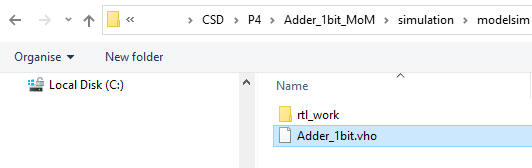

And now re-synthesise your project to generate in Quartus Prime the VHDL translation of the technology circuit (Adder_1bit.vho) and its delay file (Adder_1bit_vhd.sdo).

|

| Fig. 5. Indications for generating the VHDL technology circuit translation (vho) along with its delay file (sdo). |

Now you are ready for starting a ModelSim gate-level simulation for this flat circuit.

|

| Fig. 6. Create a new ModelSim project. |

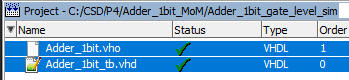

Add the same testbench that you also have copied from Lab3 to the new location:

|

| Fig. 7. Add the same testbench and flat structure |

Compile all and check the project's integrity. Therefore, hierarchical structures formed by multiple VHDL files are replaced by a single flat VHO file to be tested using the same testbench.

|

| Fig. 8. Check the project integrity. |

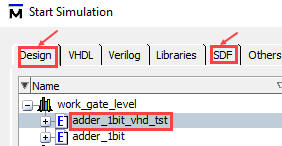

Start a new simulation paying attention this time to both "Design" and "SDF" tabs:

|

| Fig. 9. |

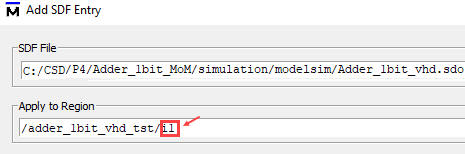

Attach the standard delay file to the region of interest:

|

| Fig. 10. The region where to apply the SDO file is the instance i1 (the unit-under-test). |

Run and check that the full wave is the same as it was in functional simulations.

|

| Fig. 11. Full view of the simulation results. |

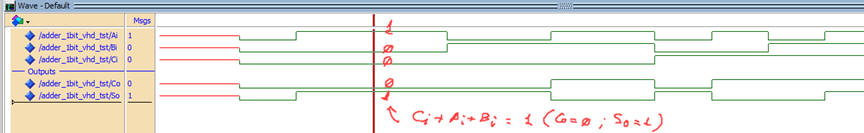

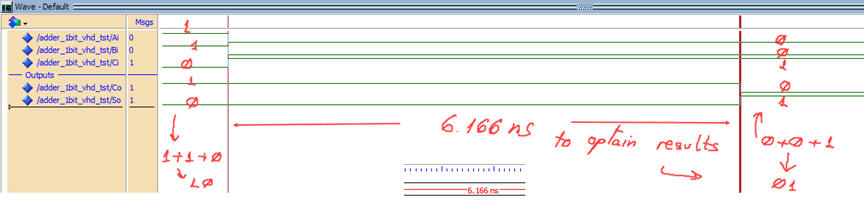

Zoom at a given signal transition to measure propagation delays using two cursors. For instance, zoom the transition from "110" to "001" that implies switching the two outputs.

|

| Fig. 12. In this example transition, both outputs changes from "10" to "01" after 6.17 ns. |

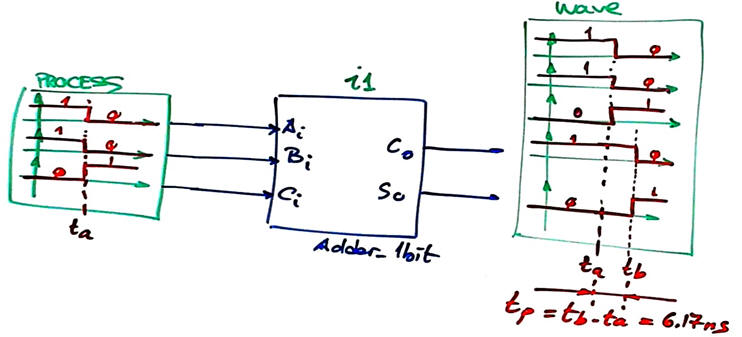

Therefore, paying attention to Fig.12, this is the experiment that we are simulating.

|

| Fig. 13. Schematic representation of the experiment observed in the transition from input combination "110" to "001" where both outputs switch values. |

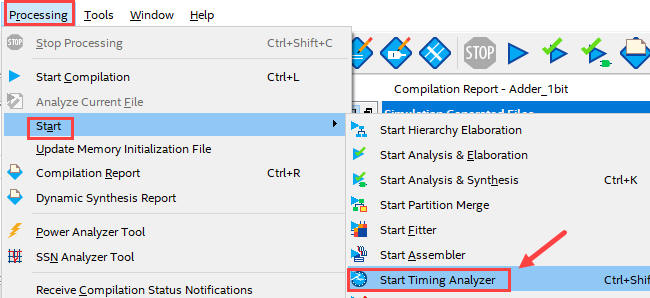

Timing anayser tool: longest propagation time and maximum speed of operation

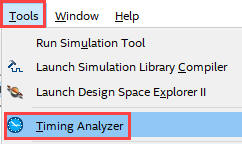

Go back to Quartus Prime to find the largest propagation delay using the timing analyser spreadsheet tool.

|

| Fig. 14. Starting processing the timing analyser tool. |

View results in the spreadsheet.

|

| Fig. 15. View results using the timing analyser tool. |

|

| Fig. 16. Spreadsheet from datasheet report. |

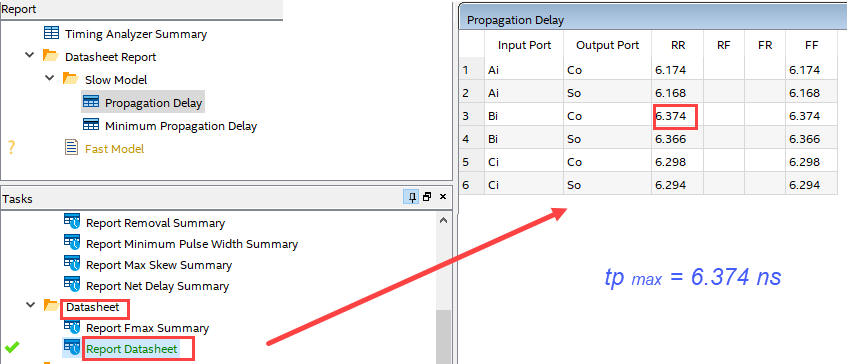

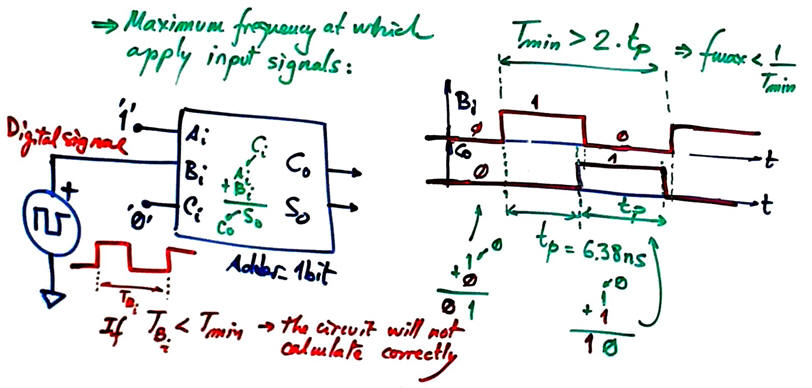

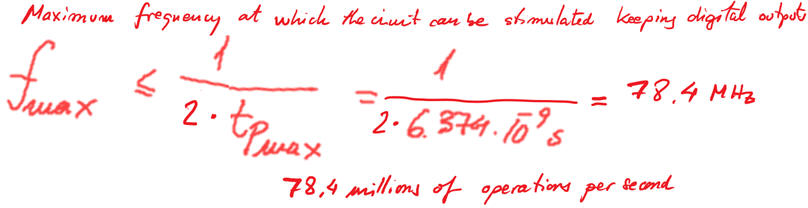

And so, calculate the maximum frequency of operation for this specific target chip MAX II (L4.3):

|

| Fig. 17. Maximum frequency at which this Adder_1bit can perform. |

And now, you can redo the project (at the same location), changing the target chip and compare how this Addder_1bit is performing for an option #2 Cyclone IV target chip.

|

| Fig. 18. Select a Cyclone IV device FPGA (Field Programmable Gate Array). |

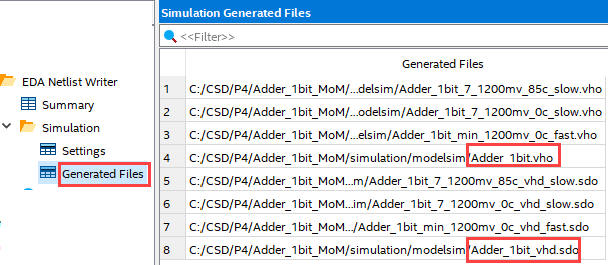

Check that the files of interest are correctly generated for this new target chip. Indeed here you can find several simulation models (fast, slow, etc.):

|

| Fig. 19. For this chip several delay models are generated. |

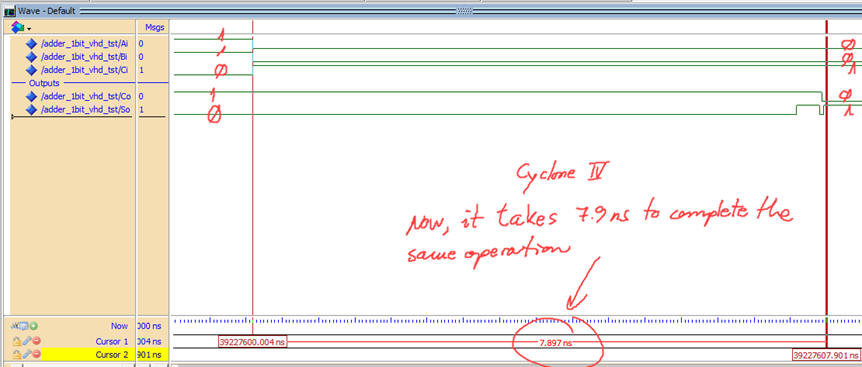

Recompile your ModelSim project and write down results:

|

| Fig. 20. Cyclone IV measurements are slightly different at the same transition. |

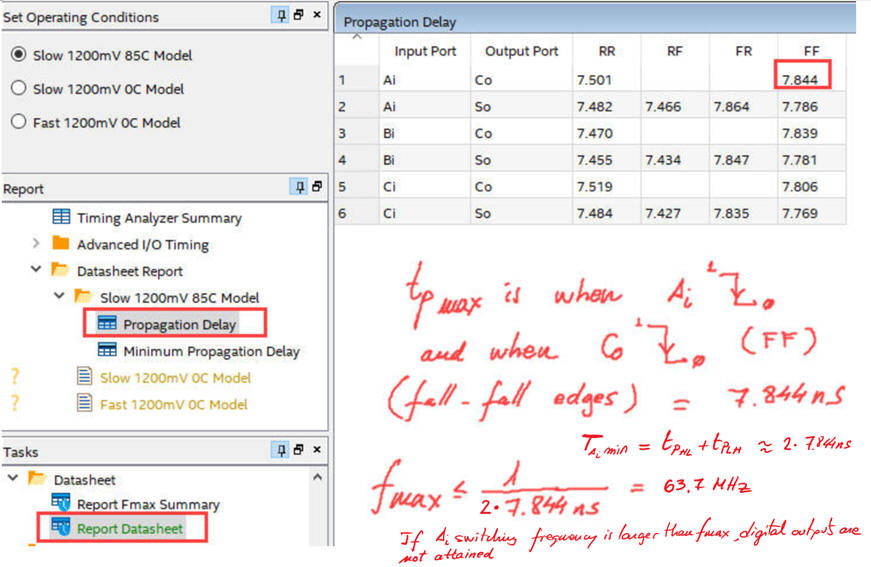

And, using the timing analyser, we can observe a longer propagation delay than in MAX II.

|

| Fig. 21. Cyclone IV measurements are slightly different at the same transition. |

And thus, the maximum frequency of operation for this Cyclone IV is slower that MAXII.

| Specifications | Planning | Developing | Functional test | Gate-level test | 6. Report | Prototype |

Follow this rubric for writing reports.

|

Laboratory |

Lab 4.1.Propagation delay and speed. Adder_1bit - Adder_16bit (RC) - Adder_16bit (CLA) Comparing circuit speed and resources in ripple-carry (RC) and carry-lookahead (CLA) architectures |

[17/10] |

1.9.1.2. n-bit adders [L3.2]

1.9.1.2.1. Ripple-carry adder: Adder_4bit, Adder_8bit [Lab 3], Adder_16bit [Lab 4],(option #1)

1.9.1.2.2. Carry-lookahead adder: Adder_4bit, Adder_16bit [Lab 4], (option #2)

In the project above, you have seen how is implemented the same design in two target chips. Now we have in mind solving the same project Adder_16bit using two different architectures synthesised for the same target chip. Thus, learning basic concepts on circuit optimisation. You will observe what is the difference between ripple carry and carry-lookahead adders, which one is faster and why?

| 1. Specifications | Planning | Developing | Functional test | Gate-level test | Report | Prototype |

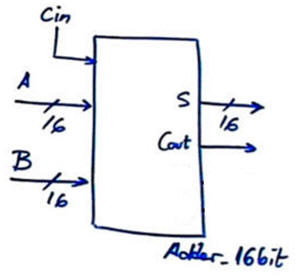

Option #1: Design an Adder_16bit using ripple-carry technique (RC).

|

|

| Fig. 1. Symbol and example waveforms. |

|

Here we rely on the work done when designing the tutorial Adder_4bit ripple-carry (RC). Zero (Z) flag will not be implemented, it simply adds another level of gates and is not necessary for the purpose of comparing with the Adder_16bit CLA presented below as the third project in this lab session.

| Specifications | 2. Planning | Developing | Functional test | Gate-level test | Report | Prototype |

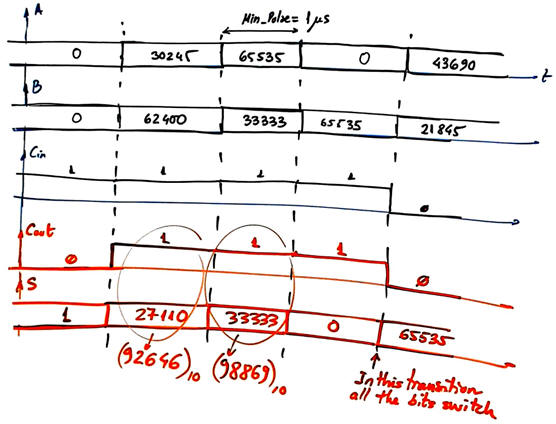

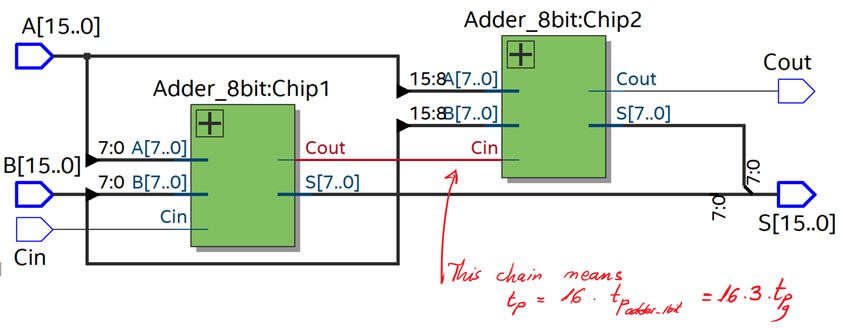

Fig. 2 shows the ripple-carry architecture. Remember that we already have designed Adder_8bit component in Lab3 using the same carry chain strategy.

|

| Fig. 2. Adder_16bit architecture. |

Project location:

C:\CSD\P4\Adder_16bit_RC\(files)

| Specifications | Planning | 3. Developing | Functional test | Gate-level test | Report | Prototype |

Let us pick up a MAX II EPM2210F324C3 target chip.

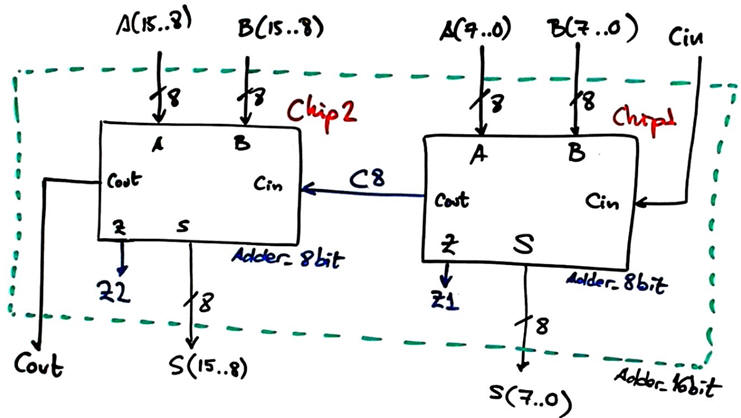

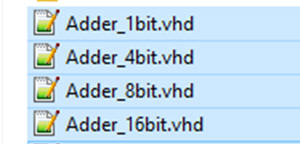

VHDL file translation of the architecture in Fig. 2: Adder_16bit.vhd.

Components files: Adder_8bit.vhd , Adder_4bit.vhd and Adder_1bit.vhd (plan A or plan B) can be found in Lab3.

|

| Fig. 3. RTL view and all the files requires in this design. |

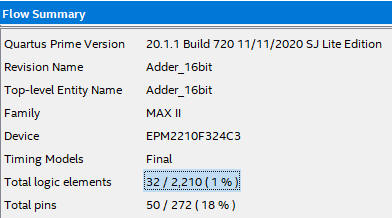

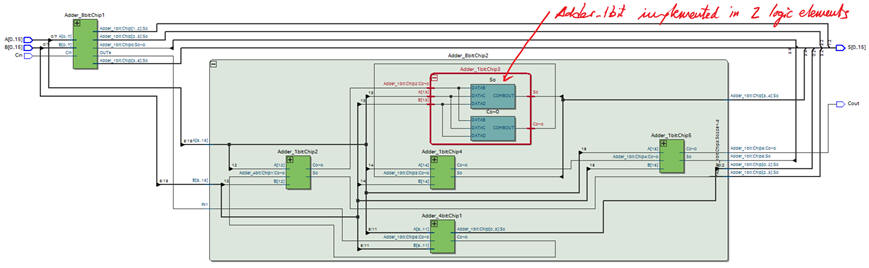

Technology view and project summary shows that only 32 logic elements are used for synthesising this project, saving much hardware with respect the CLA implementation below proposed in the next project.

|

| Fig. 4.Technology view. Each Adder_1bit is implemented in two logic elements. To make it simple and comparable to classic technologies, we can imagine that the Adder_1bit is solved using 3 levels of gates. |

| Specifications | Planning | Developing | 4. Functional test | Gate-level test | Report | Prototype |

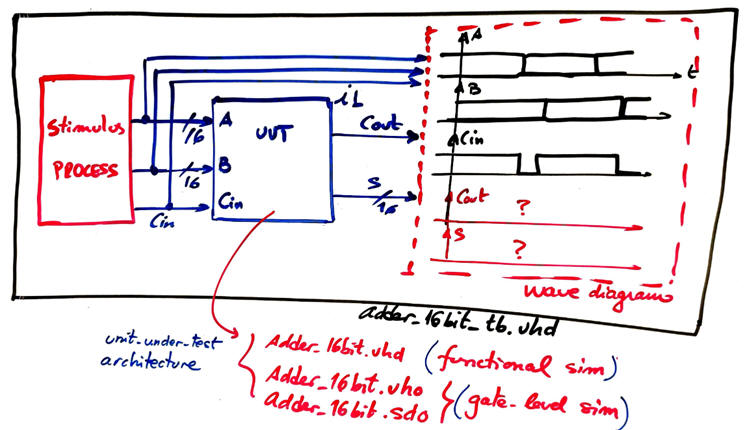

This is the translation of the testbench fixture and some signal activity proposed in Fig. 1: Adder_16bit_tb.vhd. It can be used for both, functional and gate-level simulations.

|

| Fig. 5. VHDL testbench fixture. The UUT is described as a hierarchical VHDL project when performing a functional simulation, and as a flat technology circuit when solving the gate-level simulation. |

The ideal functional results in this design step #4 must be identical for both projects of the same entity: ripple-carry and carry-lookahead Adder_16bit.

|

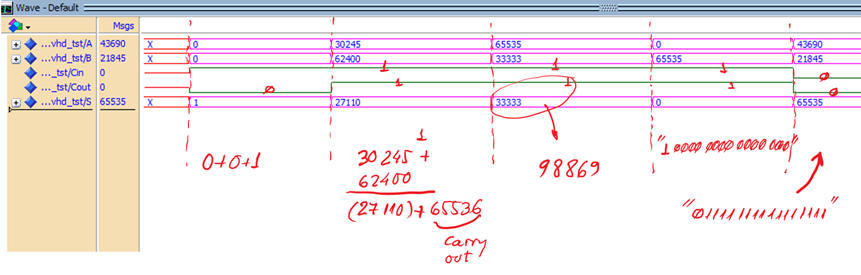

| Fig. 6. Functional simulation results. |

| Specifications | Planning | Developing | Functional test | 5. Gate-level test | Report | Prototype |

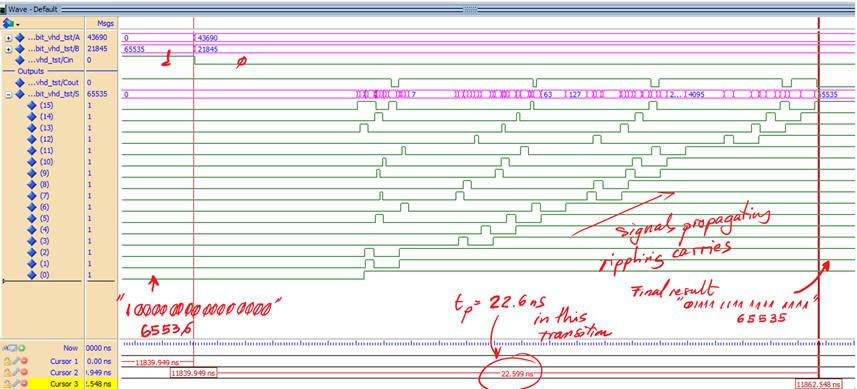

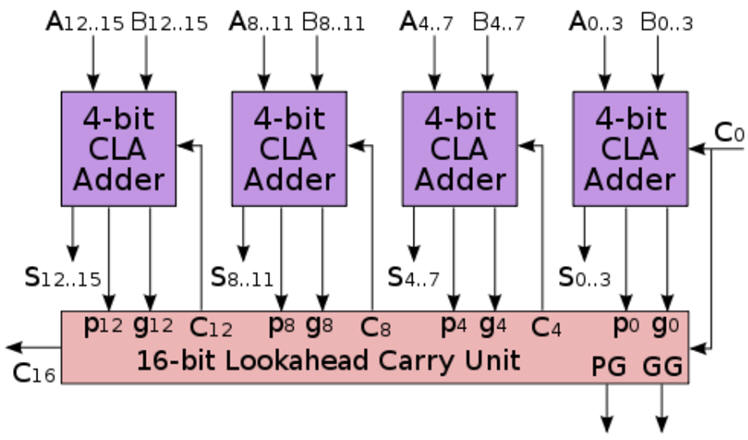

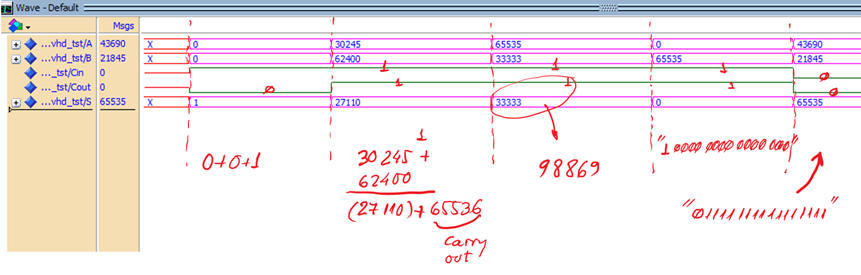

Running a gate-level simulation for this ripple-carry Adder_16bit, for instance, at the transition highlighted in Fig.1 where all bits have to change, we obtain an accumulated propagation delay of tP = 22.6 ns, practically doubling the one produced by the CLA adder in the project below.

|

| Fig. 7. Gate-level simulation results at a particular transition. |

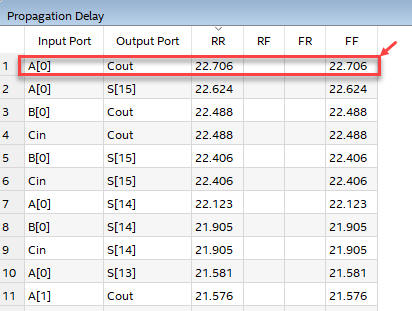

When running the timing analyser, the maximum delay occurs when driving A(0) and waiting results at Cout. This is tP= 22.7 ns, allowing a maximum frequency of operations of 22 Mops. (unsigned radix-2 16-bit millions operations per second).

|

| Fig. 8. Timing analyser spreadsheet. |

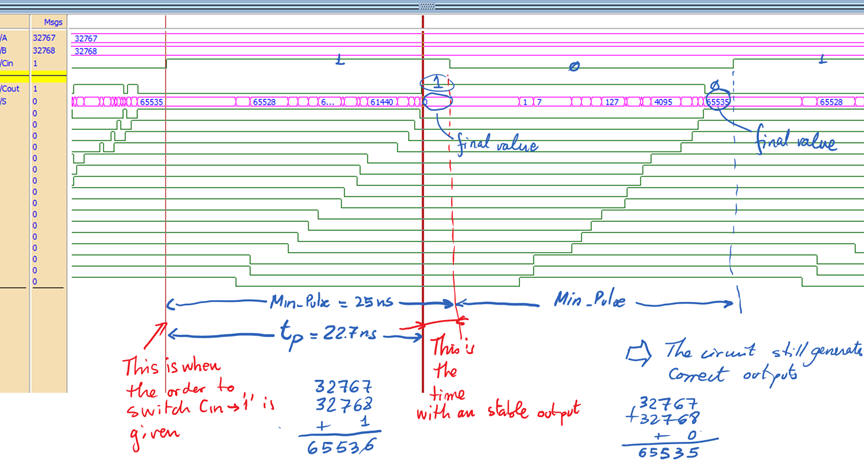

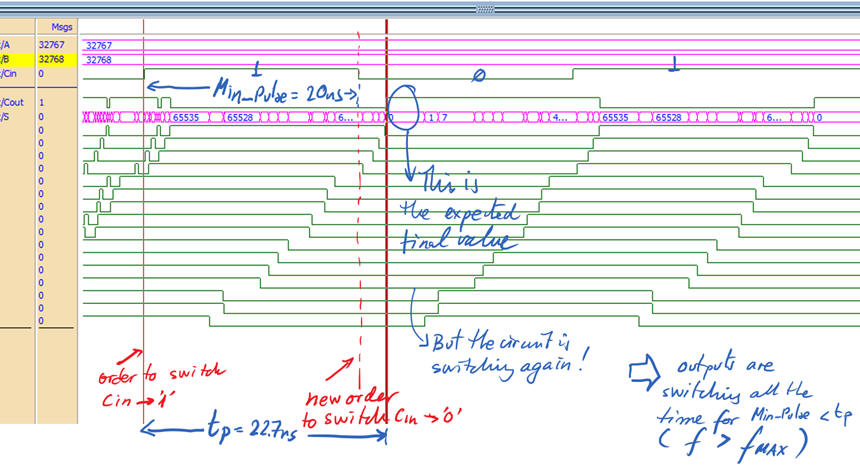

Furthermore, at this point the answer to the question: which is the minimum value for Min_Pulse for experimentation in the laboratory becomes straightforward: Min_Pulse > tP. Min_Pulse smaller that the propagation delay of the circuit will imply that the circuit is going to be switching continuously, never being able to reach stable output values. We can verify that using this set of vectors Adder_16bit_tb.vhd as represented in Fig. 9 (Min_Pulse = 25 ns) and Fig. 10 (Min_Pulse = 20 ns).

|

| Fig. 9. Min_Pulse is 25 ns, practically on the limit. |

|

| Fig. 10. Min_Pulse is 20 ns < tP. Thus, the outputs never settles to a valid result. |

It is time to compare results with the new carry-lookahead design proposed in the next project.

| Specifications | Planning | Developing | Functional test | Gate-level test | 6. Report | Prototype |

Follow this rubric for writing reports.

|

Laboratory |

Lab 4.1 Propagation delay and speed. Adder_1bit - Adder_16bit (RC) - Adder_16bit (CLA) Comparing circuit speed and resources in ripple-carry (RC) and carry-lookahead (CLA) architectures |

[17/10] |

1.9.1.2. n-bit adders

1.9.1.2.1. Ripple-carry adder: Adder_4bit, Adder_8bit [Lab 3], Adder_16bit [Lab 4], (option #1)

1.9.1.2.2. Carry-lookahead adder: Adder_4bit, Adder_16bit [Lab 4],(option #2)

Let us complete this lab tutorial considering the enhanced architecture based on carry-lookahead adders. You will observe what is the difference between ripple carry and carry-lookahead adders, which one is faster and why?

| 1. Specifications | Planning | Developing | Functional test | Gate-level test | Report | Prototype |

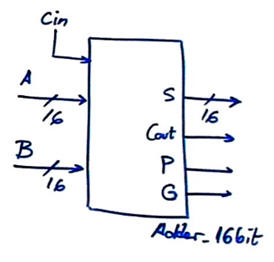

Option #2: Design an Adder_16bit using the carry-lookahead (CLA) technique. The additional signals in this symbol P (propagator) and G (generator) are outputs required for chaining larger adders using the same CLA architecture.

The truth table and timing diagram are the same stated in Adder_4bit CLA considering now radix-2 numbers ranging up to 65535 = "1111111111111111".

|

|

| Fig. 1. Symbol and waveforms. |

|

Here we rely on the work done when designing the tutorial Adder_4bit CLA. For instance, read in Wikipedia how an Adder_16bit works and how it is possible to calculate all carries beforehand. This reference also explains how to chain carry generators: Ercegovac, M., Lang, T., Moreno, J. H., "Introduction to Digital Systems", John Wiley & Sons, 1999). It includes slides: Chapter 10 is on arithmetic circuits.

| Specifications | 2. Planning | Developing | Functional test | Gate-level test | Report | Prototype |

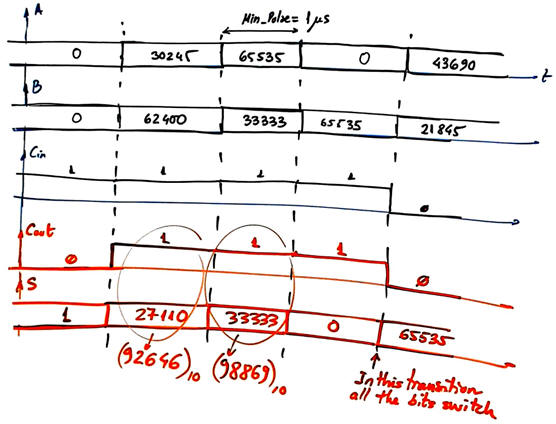

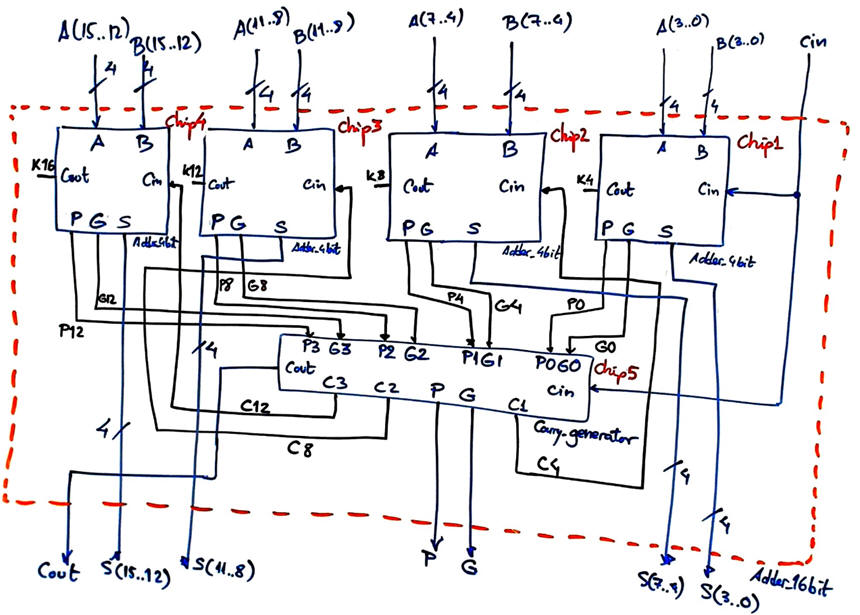

Fig. 2 shows the picture from Wikipedia that is adapted in CSD as Fig 3.

|

| Fig. 2. Adder_16bit architecture proposed in Wikipedia to be written in CSD as VHDL file. |

The Adder_16bit has the same structure than the circuit designed in Adder_4bit, as shown in Fig. 3.

|

| Fig. 3. Planning the Adder_16bit. How many gate-levels are expected in this circuit? |

Project location:

C:\CSD\P4\Adder_16bit_CLA\(files)

| Specifications | Planning | 3. Developing | Functional test | Gate-level test | Report | Prototype |

We will pick up the same Intel MAX II EPM2210F324C3 target chip. Thus, the same chip will implement the same entity but with two alternative architectures.

VHDL file translation of the architecture in Fig. 3: Adder_16bit.vhd.

Components Carry_generator.vhd and Adder_4bit.vhd can be found in tutorial Adder_4bit.

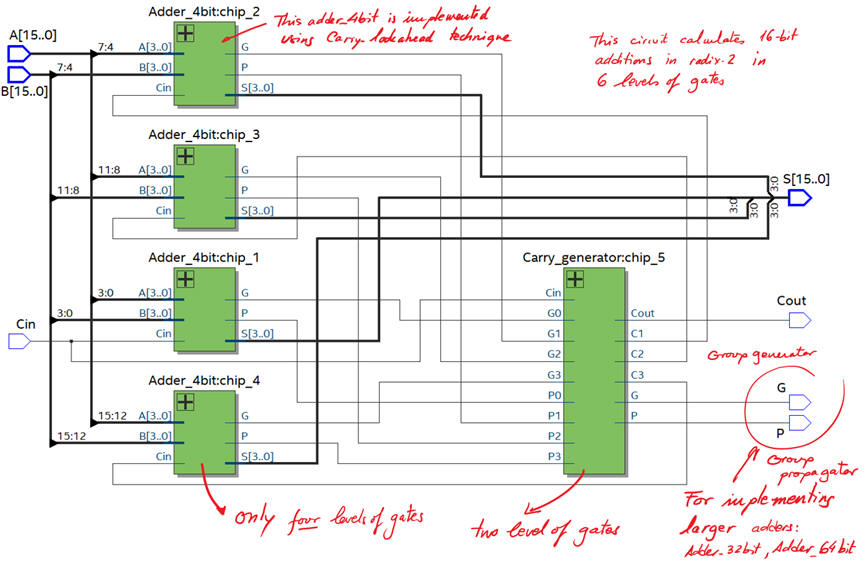

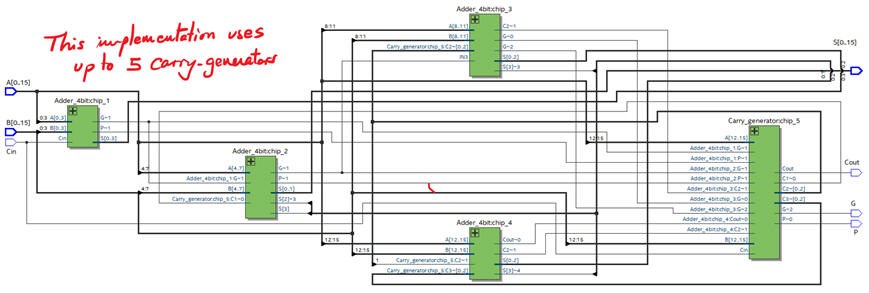

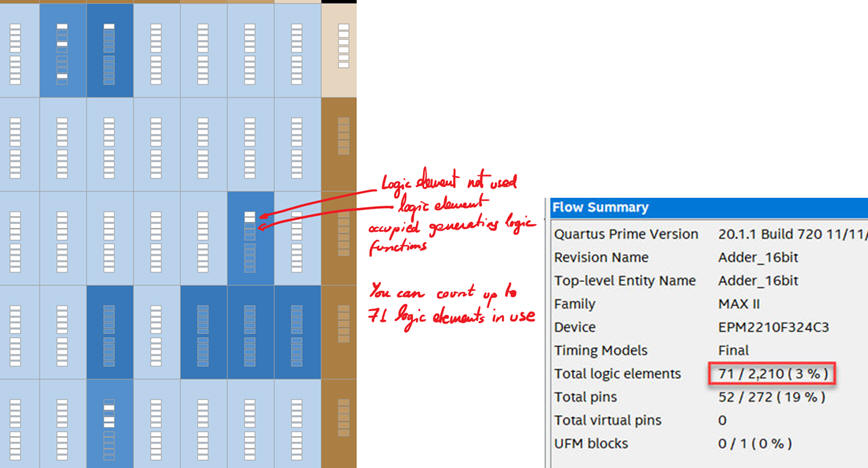

Start a VHDL synthesis project and observe the schematics. This time the architecture is far more complex, compromising up to 71 logic elements; more chip logic resources with the aim of obtaining a faster circuit.

|

| Fig. 4. RTL view. |

The architecture uses up to five Carry_generator circuits organised in two levels (one carry_generator in each Adder_4bit module, and another one in the top entity). However, the largest number of logic gates levels is only six.

|

| Fig. 5. Technology view. |

Chip planner tool allows us to map exactly where all the resources in use are located.

|

| Fig. 6. MAX II chip occupation from chip planner tool. |

| Specifications | Planning | Developing | 4. Functional test | Gate-level test | Report | Prototype |

Now, it is time to test the synthesised circuit above. Thus, we can use the same VHDL fixture represented in the Fig. 5 of the previous project Adder_16bit RC.

Example of testbench Adder_16bit_tb.vhd from which to copy the stimulus signals. We are expecting the same ideal functional results represented in Fig. 7 when applying the same input vectors.

|

| Fig. 7. Functional results. |

| Specifications | Planning | Developing | Functional test | 5. Gate-level test | Report | Prototype |

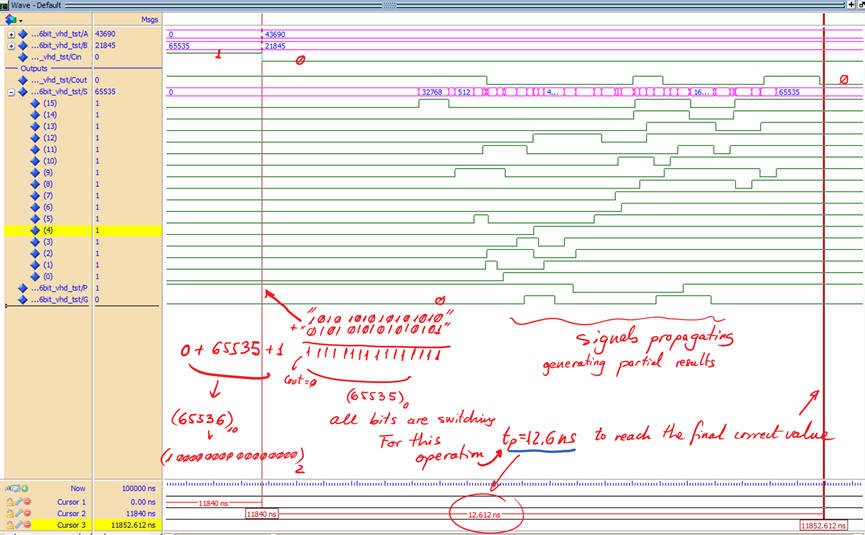

Now, when running a gate-level simulation at the same transition, a shorter propagation delay is obtained. Only 12.6 ns (saving 10 ns from the same design above based on ripple-carry).

|

| Fig. 8. Gate-level simulation. |

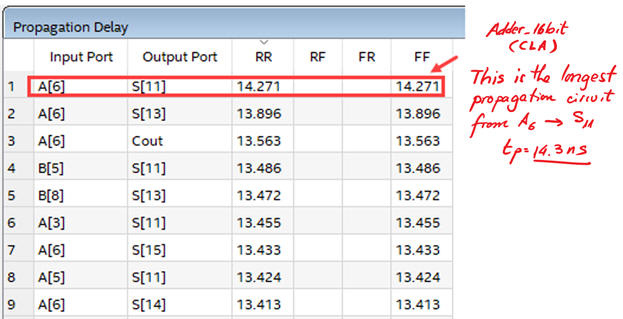

And, finally, measuring the longest propagation delay using the timer analyser tool, we can deduce the maximum circuit's speed. The longest signal path is established between input A(6) and output S(11), tP = 14.3 ns. This circuit is capable of performing 35 Mops. Thus, an improved architecture using more hardware (logic elements) generates a faster circuit.

The drawback is that the dynamic power consumption will be higher than the same circuit based on the RC technique. At this CSD introductory level, and from the perspective of classic technologies, we can say that the static power consumption will be larger because there are more gates connected to the power supply, and the dynamic power consumption will also be larger because there are many more logic gates switching.

|

| Fig. 9. Timing analyser spreadsheet showing CLA adder results. |

| Specifications | Planning | Developing | Functional test | Gate-level test | 6. Report | Prototype |

Follow this rubric for writing reports.

| Specifications | Planning | Developing | Functional test | Gate-level test | Report | 7. Prototype |

A prototype on arithmetic circuits, an ALU_9bit design, is presented in the next LAB4.2.

Conclusions

These three projects have been used for learning new tools: gate-level simulation in ModelSim and Quartus Prime timing analyser, and for demonstrating how digital technologies, gate switching (operating speed) and logic resources (logic elements) are linked. We can imagine that when more resources are used the circuit is more power demanding. You can balance speed and power consumption choosing alternative designs.

-

The synthesis of a given architecture in a newer PLD chip will compute the same logic functions faster, because of shorter propagation delays.

-

Carry-lookahead architecture is much faster than ripple-carry, but it requires more circuits for generating and propagating carry signals in fewer gate-levels.

-

Ripple-carry circuits will be less power demanding that carry-lookahead circuits, because they are designed with less circuitry (logic gates, logic elements).