|

Laboratory |

|

[24/10] |

|

This is the post lab assignment PLA4.2 to be submitted next Lab 6 session. The idea is to report and discuss measurements. |

7. Designing an FPGA prototype

Laboratory prototyping is the next phase in the circuit design flowchart (number 7). We have to go advancing from computer simulations to real hardware that can be industrialised in factories and sold as a product. As you have seen, all our introductory designs fit in a single chip. And we take advantage of the versatile FPGA (field programmable logic arrays) containing thousands of configurable logic elements. Hence, the idea is to choose an FPGA prototyping platform, design an extension PCB board to place when necessary more inputs and outputs, assign pins, configure the chip (program the FPGA RAM LUT or FLASH memories), run the application and perform measurements to check the design features.

This experiment requires that cooperative groups fill in this control sheet to be handed in to your instructor at the end of the session.

| Prototype specifications | Planning | Development | Test & measurements |

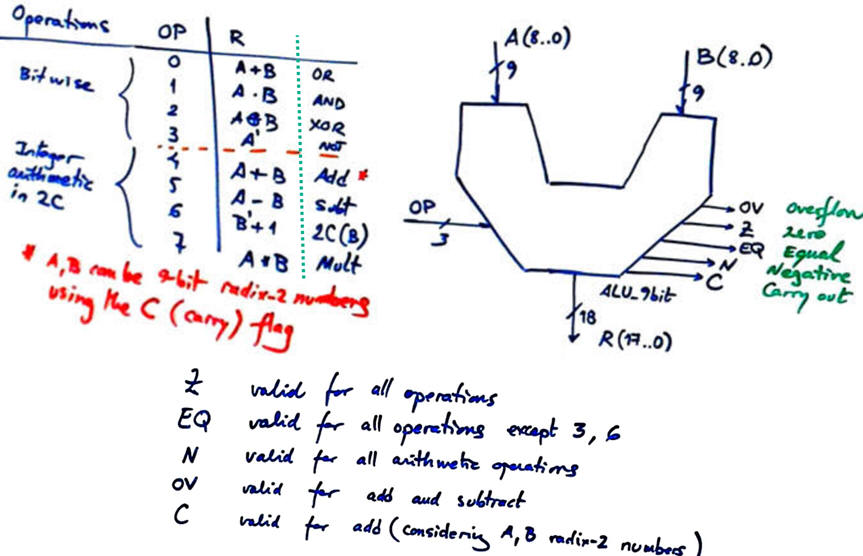

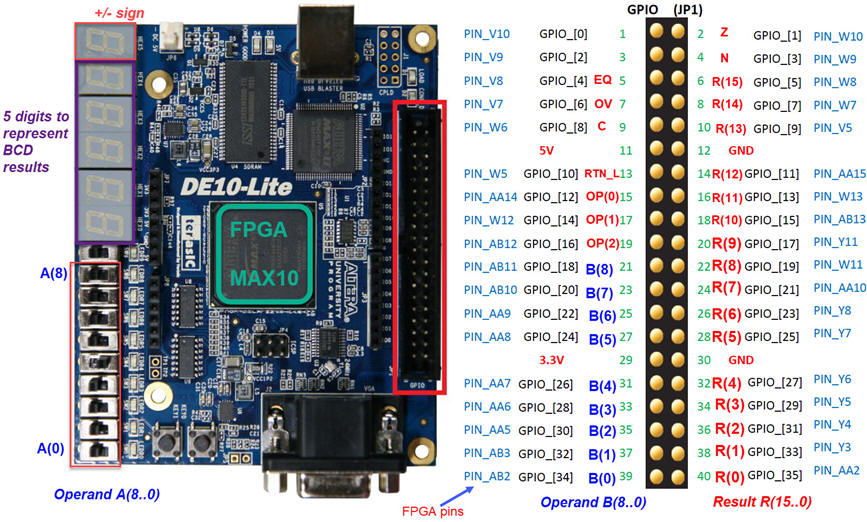

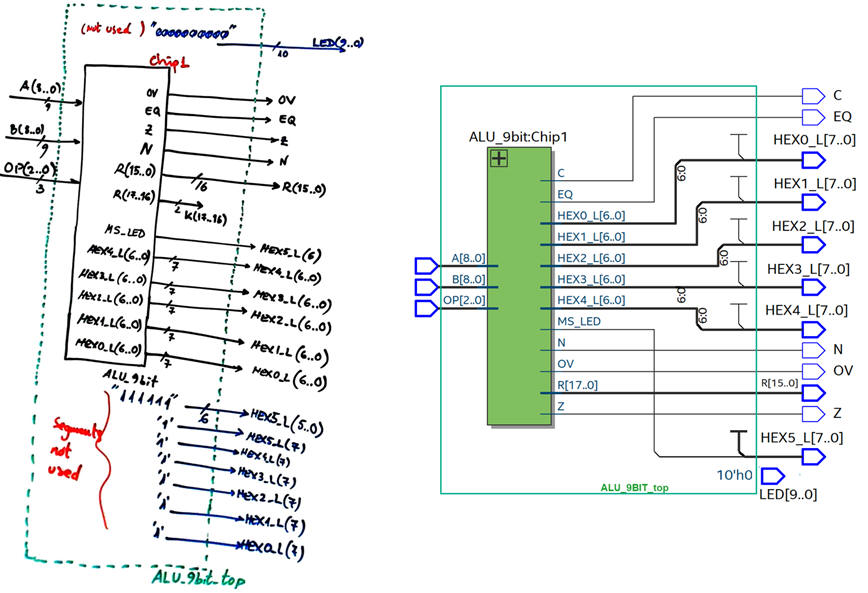

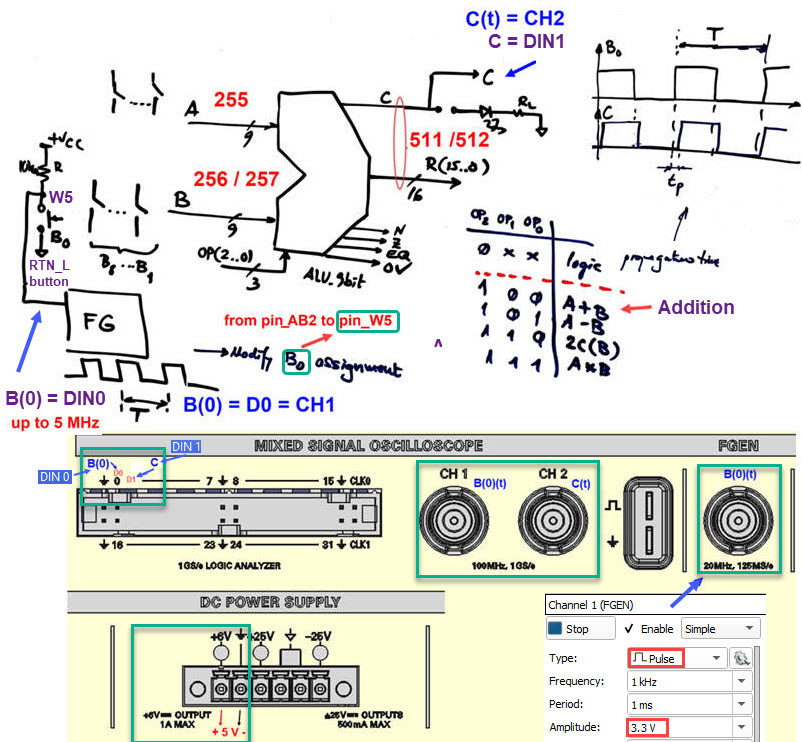

To practise with arithmetic and logic circuits we conceive the arithmetic and logic unit (ALU) sketched in Fig. 1, an ALU_9bit capable of performing eight logic and arithmetic operations, in a DE10-Lite board populated with an Intel MAX10 FPGA chip. The entity has 21 inputs and 23 outputs.

|

|

Fig. 1. ALU_9bit symbol and projected operations. |

Pre-lab activities #1:

Write a draft of the truth table considering arithmetic and logic operations and expected results. Deduce the operands and result ranges for arithmetic operations. Complete (at least) the 8 lines of the truth table using the given values A = "011111111" and B = "100000001". Do the arithmetic operations in binary 2C and check your results in decimal. Do the bitwise operations.

Draw an sketch of timing diagram. Which can be the operation to take longer to process (longest propagation time)?

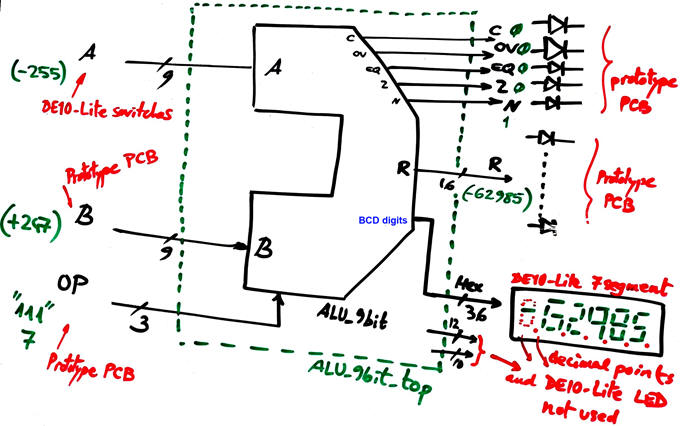

When thinking about the real implementation of such circuit, the DE10-Lite board switches can be used for inputting operand A. The six 7-segment displays can be used for representing results as BCD numbers for arithmetic operations. In this way, we can populate a PCB connected through the 40-pin general purpose input-output (GPIO) connector for capturing the operand B, selecting operations OP, representing the full binary result R(16..0) in a LED array and lighting the status flag indicators as well.

|

|

Fig. 2a. DE10-Lite and PCB prototype for accommodating all inputs and outputs. The board contains many more resources that are not used in this laboratory experiment. |

Hence, the laboratory implementation of the ALU_9bit will require a top view including switches for operands and operations, 7-segment displays and LED for results and flags. We are using only a few resources from the DE10-Lite training board.

|

|

Fig. 2b. The ALU_9bit_top project implemented using the FPGA, the DE10-Lite board and the prototype resources. |

NOTE: A similar prototype can be conceived for the next Chapter II. We can run the same ALU application replacing the switches by a 16-key matrix keypad designed as a FSM in P6 to input operands and operations sequentially, as it is usual in calculators.

| Prototype specifications | Planning | Development | Test & measurements |

Planning steps are necessary for both, the ALU_9bit architecture and the auxiliary PCB.

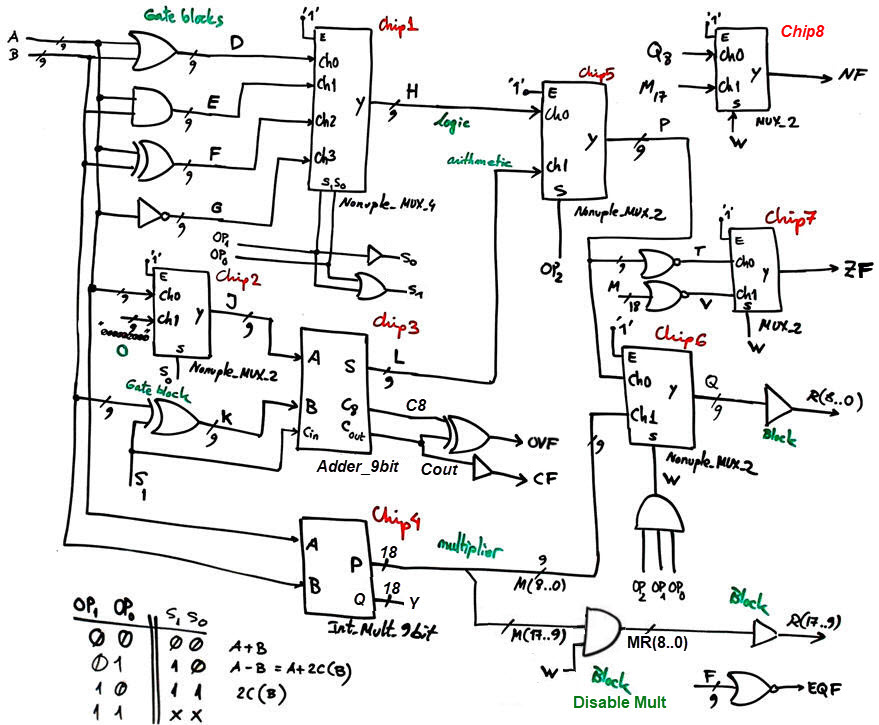

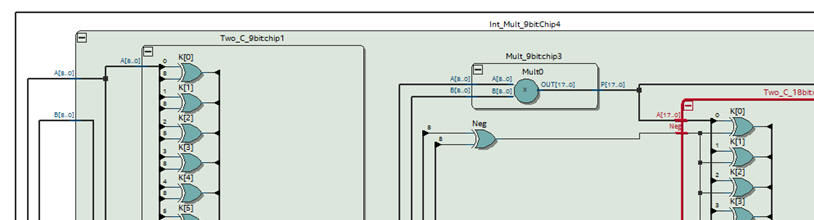

Plan C2 is required here to get an idea on the components involved and how they will be connected as a hierarchical structure. To review the theory and how components work, we can get inspiration studying similar circuits proposed in D1.18 and previous labs and tutorials. Fig. 3 shows the proposed hierarchical schematic.

Logic operations are solved by gate blocks. The Adder_9bit used for both, adding and subtracting , is proposed in the final Annex A1. The integer multiplier is designed in this tutorial Int_Mult_9bit. Several multiplexers select the operands and additional logic circuits generate and enable status flags.

|

|

Fig. 3a. Proposed ALU internal design. |

|

|

Fig. 3b. Additional circuits for using the 7-segment displays and for enabling the flags. |

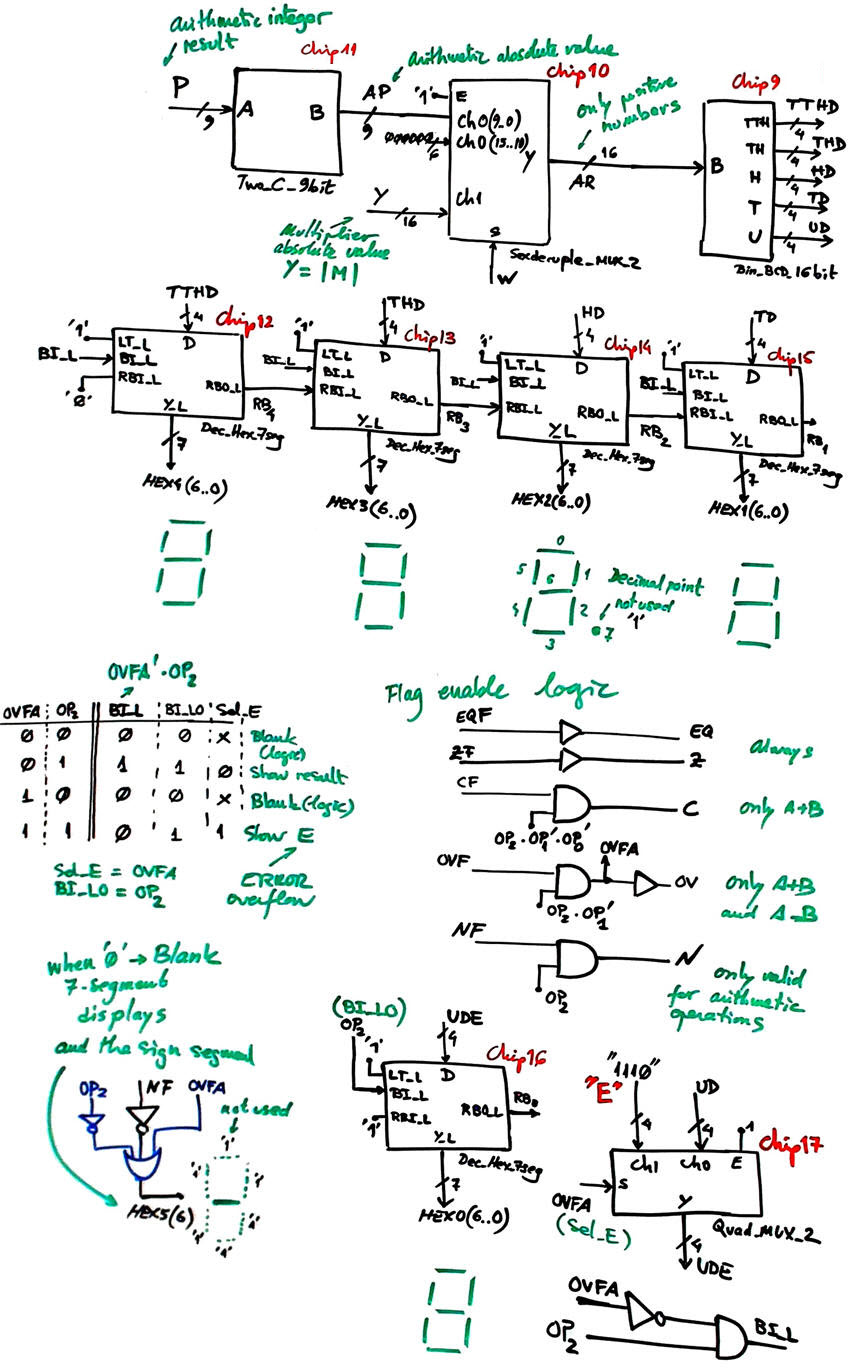

The Chip11 Bin_BCD_16bit converter for representing results in BCD will be connected to the signal Y(15..0) when performing multiplications (OP = 7), or to the signal L(8..0) when OP = 4, 5, 6. The display will be kept blank for logic bitwise operations (OP = 0, 1, 2, 3).

The full list of FPGA input and output connections is represented in Fig. 4. It is time to read the board's datasheet DE10-Lite in detail to assign FPGA pins to inputs and outputs.

|

|

Fig. 4. FPGA connections to be used in the pin assignment tool. Board LED and other unused segments will be blanked. |

Project location:

C:\CSD\P4\ALU_9bit_top\(files)

| Prototype specifications | Planning | Development | Test & measurements |

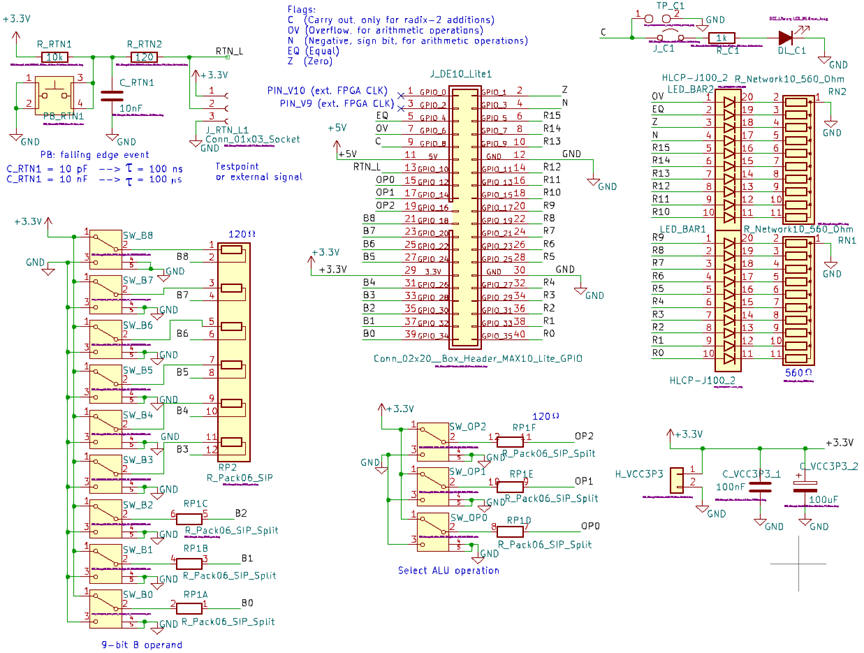

Printed circuit board (PCB)

As indicated above, in this experiment we can use the board's switches to input A(8..0). The other operant B(8..0), the operation selector OP(2..0) and the 5 status flags (N, OV, C, Z, EQ) will be placed in an auxiliary PCB connected through the 40-pin GPIO as shown in Fig.4.

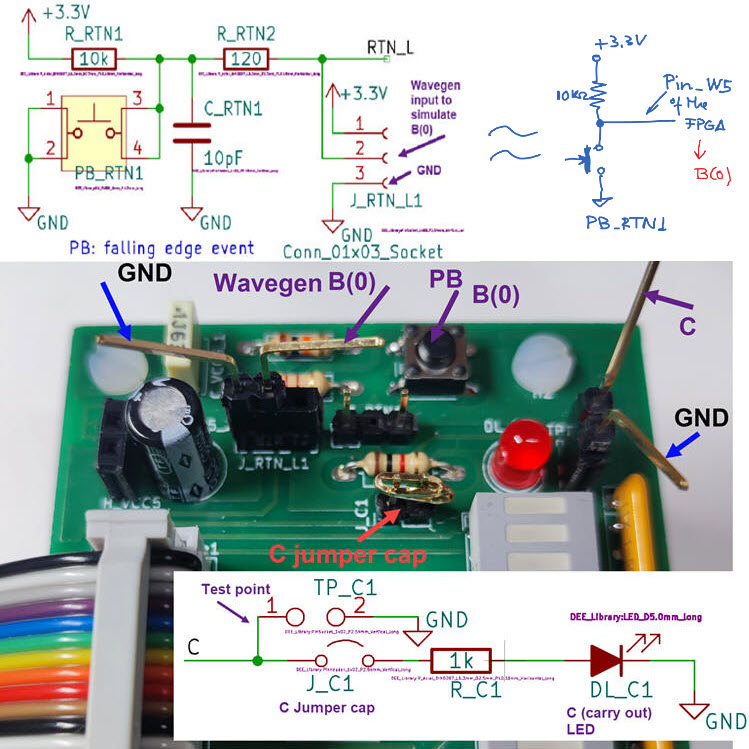

The PCB design starts capturing the schematic in KiCad as shown in Fig. 5. LED bars and resistors packs can be used to save board space. A test point TP_C1 is added at carry out (C) flag to attachan oscilloscope or multimeter probe. Another jumper where to attach an external function generator is placed at the push-button J_RTN_L. In this manner, we can stimulate RTN_L (assigning it for example as A(0) and observe waveforms at output C.

|

|

Fig. 5. Schematic captured in KiCad. |

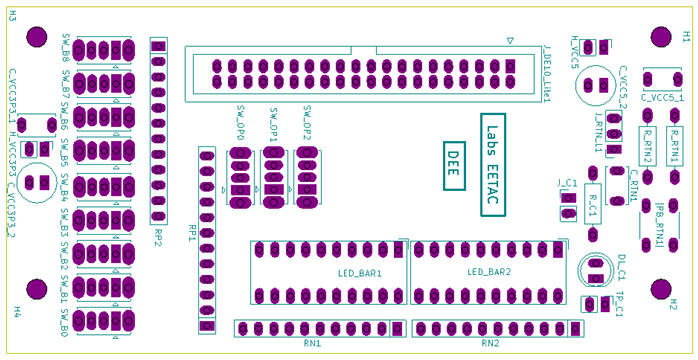

The PCB component placement is shown in Fig 6.

|

|

Fig. 6. PCB layout silkscreen that shows component placement and references. |

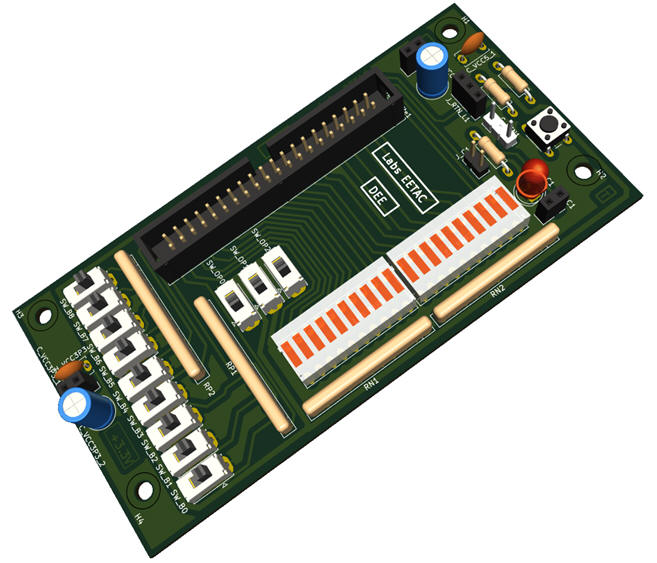

Finally, a 3D view shows the real dimensions and how the PCB will look like once soldered.

|

|

Fig. 7. PCB 3D representation. |

Hence, once the hardware circuit for the PCB is conceived, we organise a KiCad project CSD_LAB4_PCB_v2.zip to be able to manufacture the board. Each component contains the symbol, the footprint, and a link to the datasheet to prepare the bill of materials (BOM) spreadsheet.

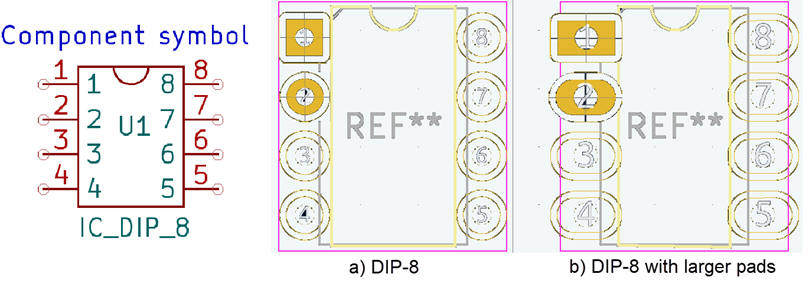

NOTE: Current CSD and DEE KiCad symbols, footprints and 3D tuned components are available in these three libraries: symbols.zip, footprints.zip and 3dmodels.zip, to be unzipped and placed in the corresponding KiCad 3rdparty user directory. Basically, in this introductory PCB design level, the idea behind tuning components is to enlarge their pads for easy soldering as shown in Fig. 8.

|

| Fig. 8. Example of a tuned footprint DIP-8 for easy soldering. |

Additionally, we can set several parameters for easy routing, manufacturing and soldering, such clearance between components and tracks (0.3 mm), signal (0.5 mm) and power (1 mm) track widths.

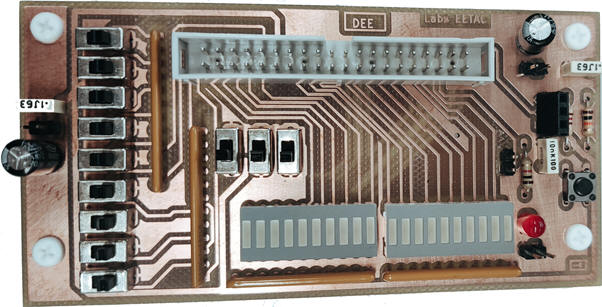

Fig. 9 shows the process of placing and soldering components on the board's prototype once manufactured using our lab machines. At this stage, we have to verify that the board works as expected or, if it is the case, make the necessary adjustments.

|

| Fig. 9. The idea of placing and soldering components on the PCB. |

Once this final revision step is completed, the PCB is ready for manufacturing as shown in Fig. 10.

|

| Fig. 10. The final manufactured board with the silkscreen layer labels printed. |

Board's picture in Fig. 11 shows the current prototype board with all the soldered components.

|

| Fig. 11. The idea of placing and soldering components on the PCB. The final manufactured board with the silkscreen layer labels printed. |

FPGA circuit

We can translate into VHDL the schematic ALU_9bit.vhd in Fig. 3a and Fig. 3b, synthesise and test the FPGA using Quartus Prime and ModelSim respectively as we have been doing hitherto. We need to take care of all the components involved in the design and include them in this plan C2 project.

These are the multiplexers used to select operands and operations: Nonuple_MUX_4.vhd, Nonuple_MUX_2.vhd, MUX_2.vhd , Quad_MUX_2.vhd, Sexdecuple_MUX_2.vhd. All of them are implemented in a single file adapting the typical plan B Dual_MUX_4.

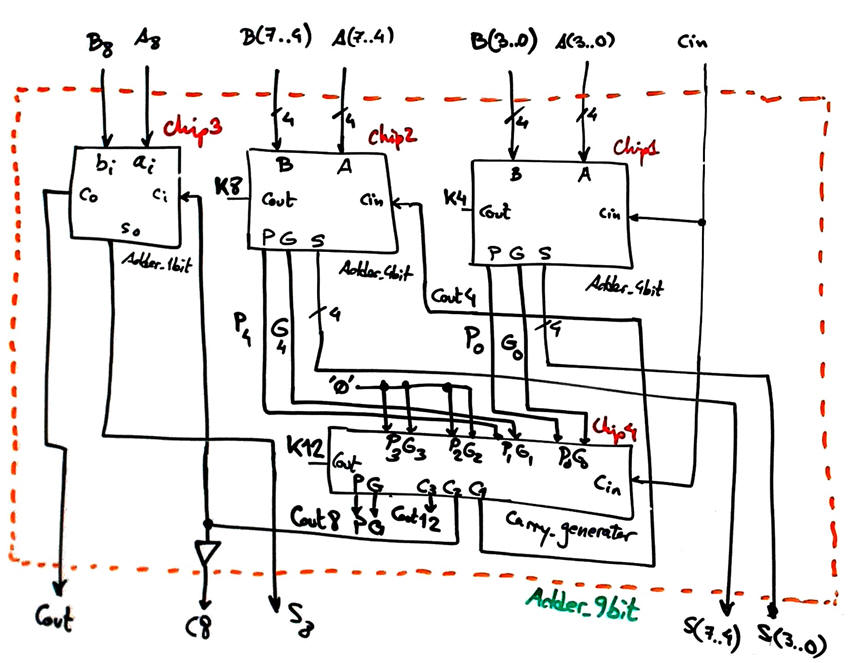

Annex A1 shows how to design a carry-lookahead (CLA) version of the Chip3 Adder_9bit.

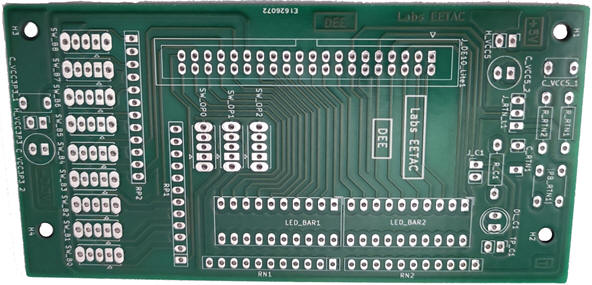

Int_Mult_9bit tutorial shows how to implement a 9-bit multiplier for integer numbers as required in Chip4.

|

|

Fig. 12. Detail on the Int_Mult_9bit RTL (Chip4). |

Bin_BCD_16bit shows how to design the converter from radix-2 to BCD for vector size of 16-bit. You will find its top entity and its component block DM74185.

Chip9 on implementing a two's complement Two_C_9bit can be found in Int_Mult_9bit tutorial.

We can continue adding the code converters to represent the result in the six 7-segment displays. The idea is that the sign is represented as a hyphen '-' when the result is negative in the display number 5 (HEX5_L(6)). This is the decoder hexadecimal to 7-segments Dec_Hex_7seg and its block Hex_7seg_decoder that can be either plan A or plan B.

The top schematic ALU_9bit_top.vhd in Fig. 13 will be used to leave unconnected R16 and R17 outputs, to disable (low '0') all the DE10-Lite active-high LED and to disable ( high '1') all the decimal point segments that are not in use in this application.

|

| Fig. 13. Top design ready for pin assignment and for prototyping. This top design allows us to add to the ALU other chip components for future experiments, such as FSM, CLK generator, data registers, etc. |

In summary, this zipped file ALU_9bit_top.zip contains all the VHDL files required in this hierarchical modular prototype.

Pre-lab activity #2: Start a Quartus Prime project in the planned location to synthesise the ALU_9bit application using all VHDL the files in the zip. Review the RTL and the technology schematics.

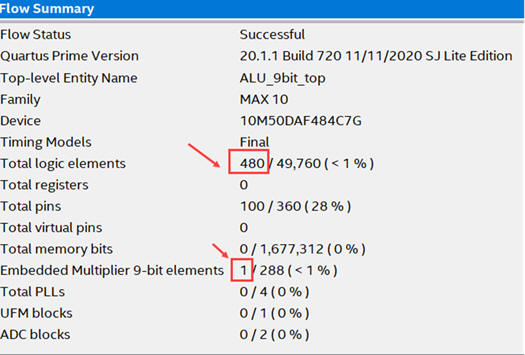

We observe how the project summary shows the use of a dedicated multiplier (one of the 288 available) and also 480 logic elements to prforms logic functions. This summary gives you an initial idea of the size and complexity of the circuits that can be engineered to fit in this target chip. This ALU_9bit_top is still using less that 1% of the FPGA resources available.

|

|

Fig. 14. Project summary. The circuit uses 480 logic elements and 1 embedded multiplier. |

| Prototype specifications | Planning | Development | Test & measurements |

ALU_9bit functional simulation

Pre-lab activity #3: Functional simulation.

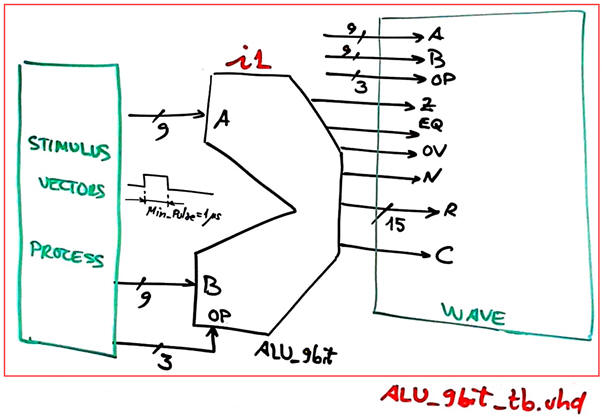

It is convenient to perform a functional simulation to check that the circuit operates correctly before configuring the target chip with the programmer application. Fig. 14 shows a testbench to stimulate the circuit with operands and operations.

|

| Fig. 14. Testbench fixture. |

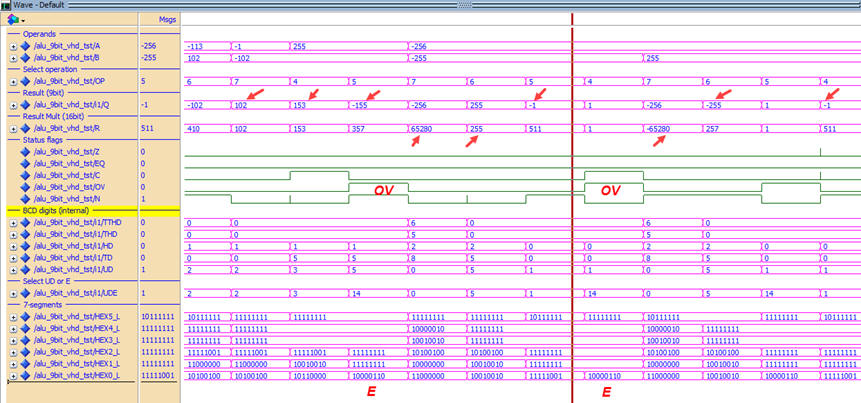

This is a testbench ALU_9bit_tb.vhd adapted from P4 where you can adapt the stimulus process and the time constant Min_Pulse. This is the wave.do setup as shown in Fig. 15.

|

| Fig. 15. ModelSim simulations. Be aware that for arithmetic operations 4, 5, and 6, the result of interest is Q(8..0) or R((8..0). |

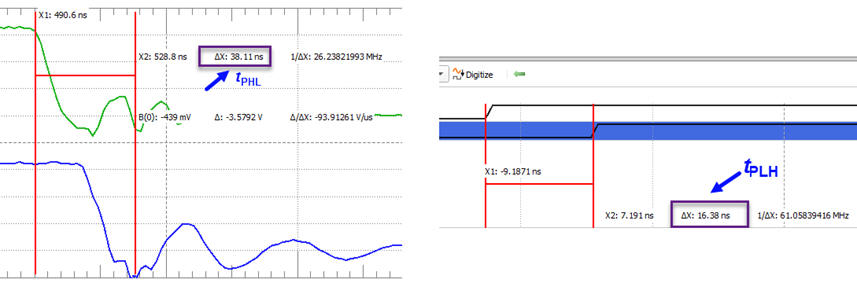

Timing analyser: longest propagation delay

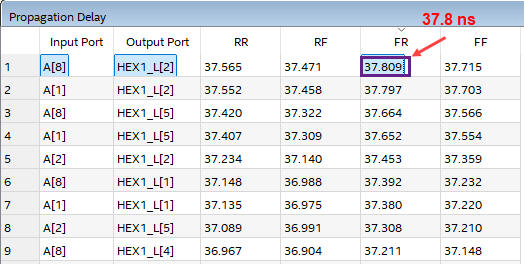

Pre-lab activity #4: Run the timing analyser to measure propagation delays as shown in Fig. 16.

Switching A(8) from high to low (F), and waiting for the HEX1_L(2) output port to go from low to high (R) takes the longest signal path, a worst-case scenario propagation delay of tP = 37.8 ns. If we attach A(8) to a signal generator, the maximum signal frequency for stimulating the circuit has to be fmax < 13.22 MHz, meaning more than thirteen million operations per second.

|

|

Fig. 16a. Propagation delay from input ports to output ports. |

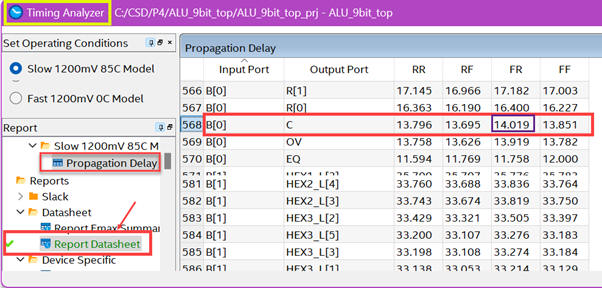

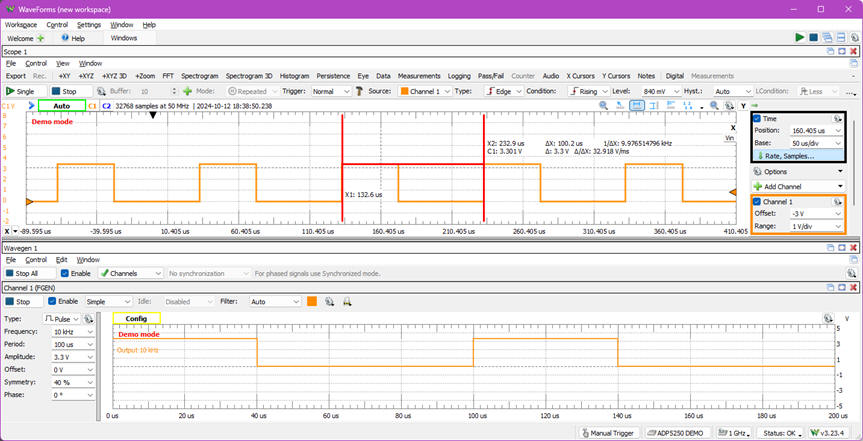

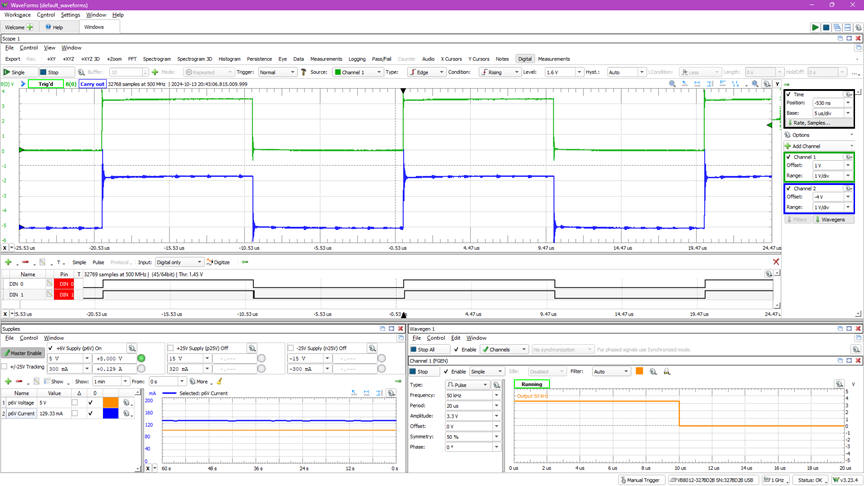

Fig. 16b shown the measurement of the propagation delay obtained attaching B(0) to the signal generator (Wavegen) and the logic analyser at the output flag C (carry out). We can visualise analogue waveforms using the oscilloscope channels and also their digitalised equivalents, as we propose to do in section F of this experiment.

|

|

Fig. 16b. Propagation delay from input ports to output ports. |

Instrument VB8012 driver installation

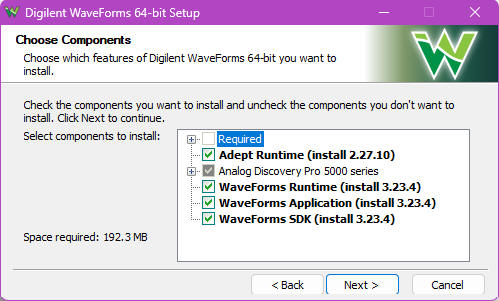

Pre-lab activity #5: Follow the indications to install the WaveForms software from Digilent for driving the VB8012 compact instrument in your computer.

The aim is that at least one student of your lab cooperative group will have this instrument driver installed in their PC.

|

| Fig. 17. Instrument driver installation. |

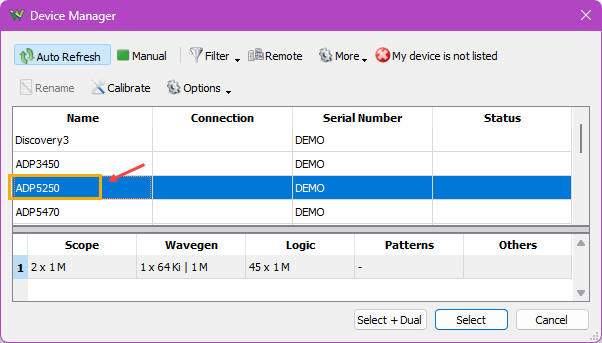

The advantage is that you can practise with the instrument in demo mode at home, ahead of this lab session. Select the ADP5250 instrument to play with the oscilloscope, function generator, multimeter, power supplies, etc.

|

| Fig. 18. Instrument demo selection when the real instrument is not connected. |

For instance, choose from the waveform generator a 40% duty cycle 3.3 V digital pulse waveform. Acquire and visualise it in the oscilloscope CH1, as shown in Fig. 19.

|

| Fig. 19. WaveForms windows environment. Be aware to select a light (default) background so that you can easy copy measurement pictures for your report. |

Lab session activities

A) FPGA pin assignment

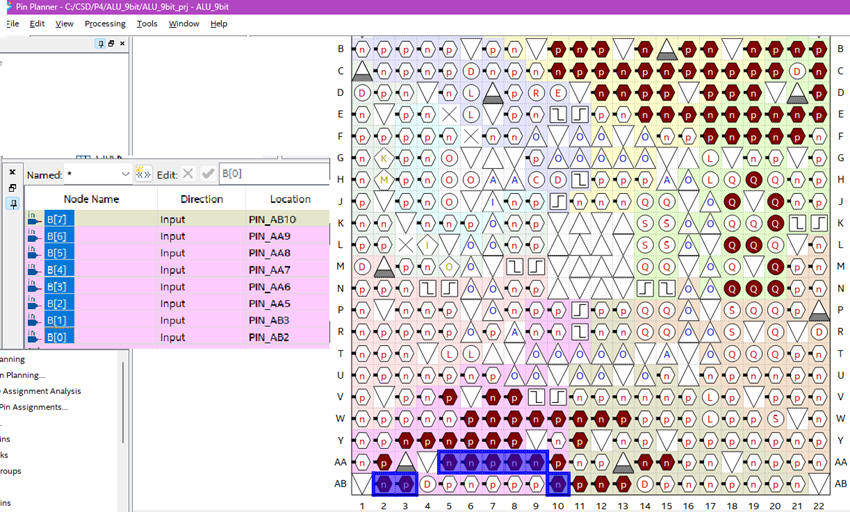

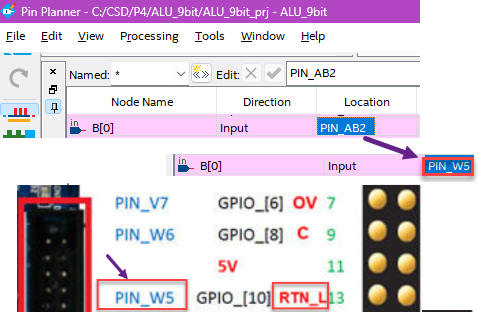

Fig. 20 shows how FPGA pins can be assigned using the "Pin Planner" tool or the "Assignment editor" accordingly to Fig. 4. The information on the FPGA pins is available at the DE10-Lite user manual. The complete spreadsheet file ALU_9bit_top_prj.csv including all the assignments can be imported directly to Quartus before the final synthesis.

|

|

Fig. 20. Pin Planner tool. |

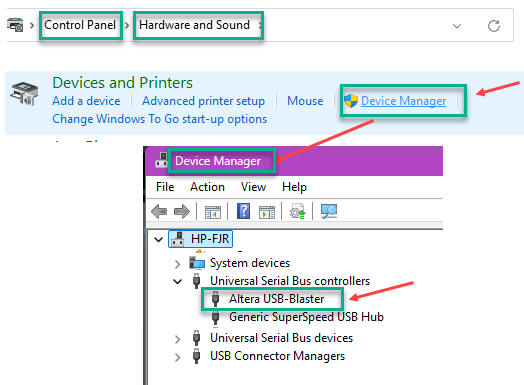

B) DE10-Lite programmer USB-blaster driver

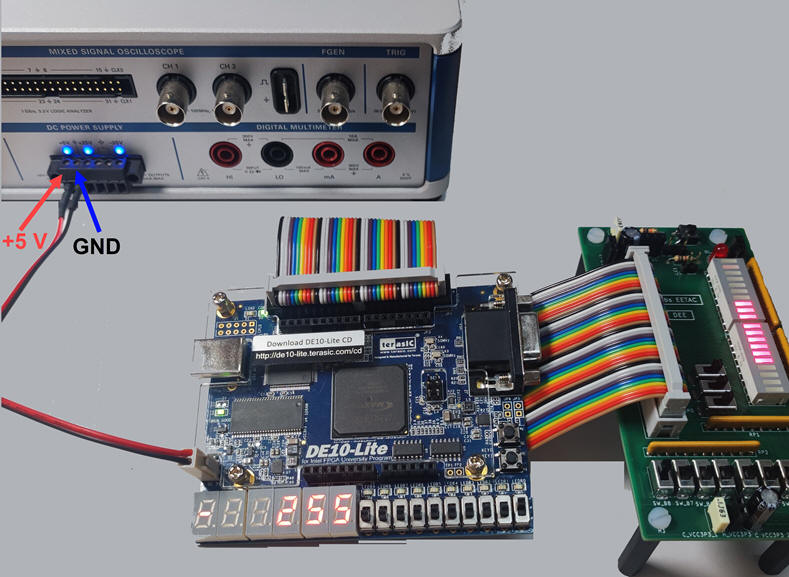

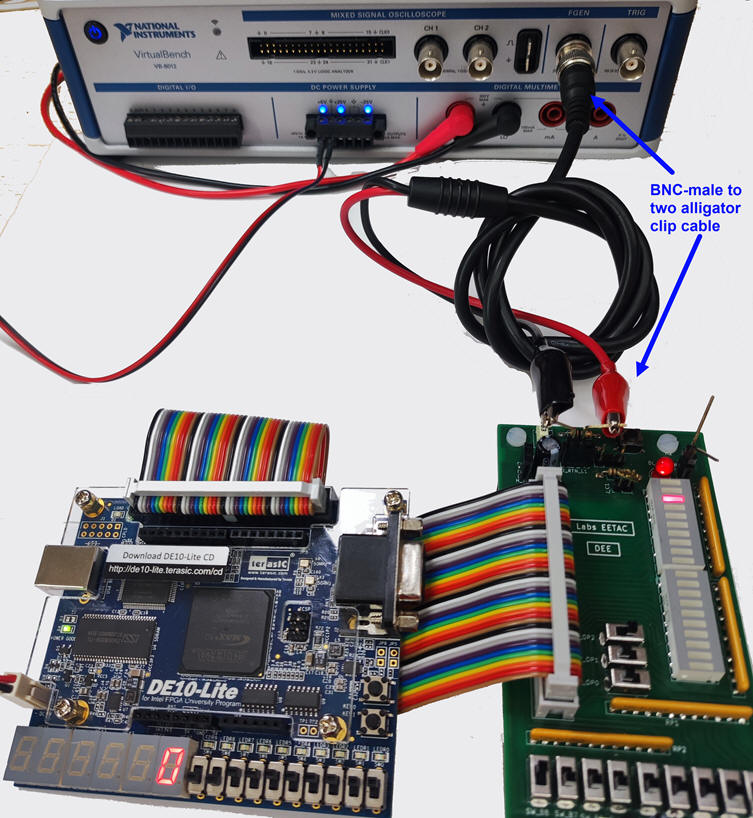

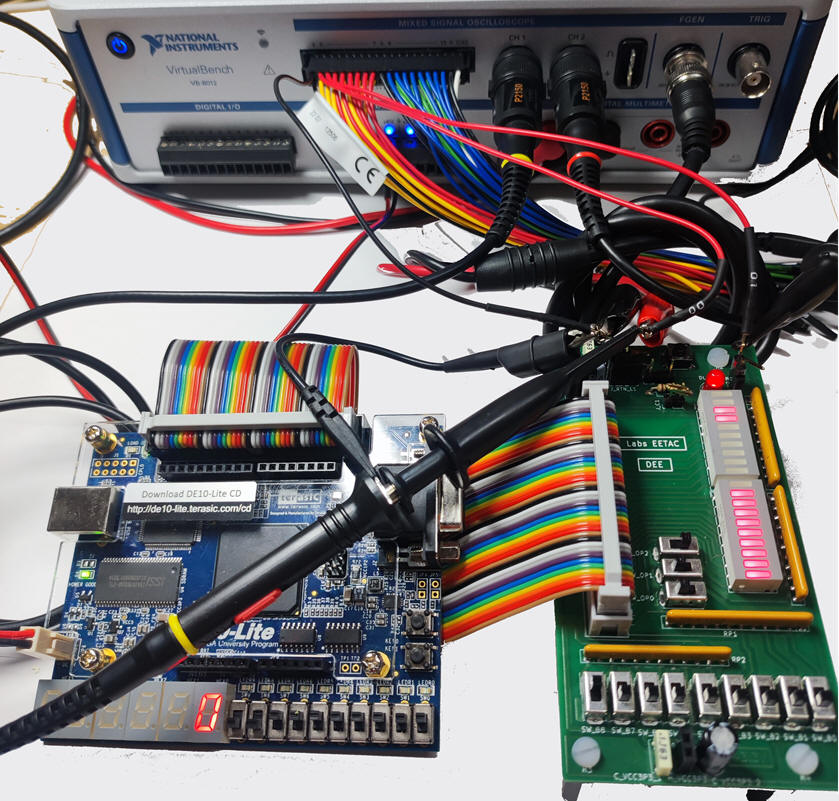

Attach using the 40-pin flat cable the prototype board to the DE10-Lite.

Connect the DE10-Lite to the computer USB.

Follow the indications to install the DE10-Lite USB blaster driver in your computer if it is the first time you ae using the FPGA. The aim is to allow your PC to recognise the DE10-Lite board hardware when connected as a valid USB controller as shown in Fig. 21.

|

|

Fig. 21. Your board is correctly identified by the computer hardware device manager accessible from the control panel. |

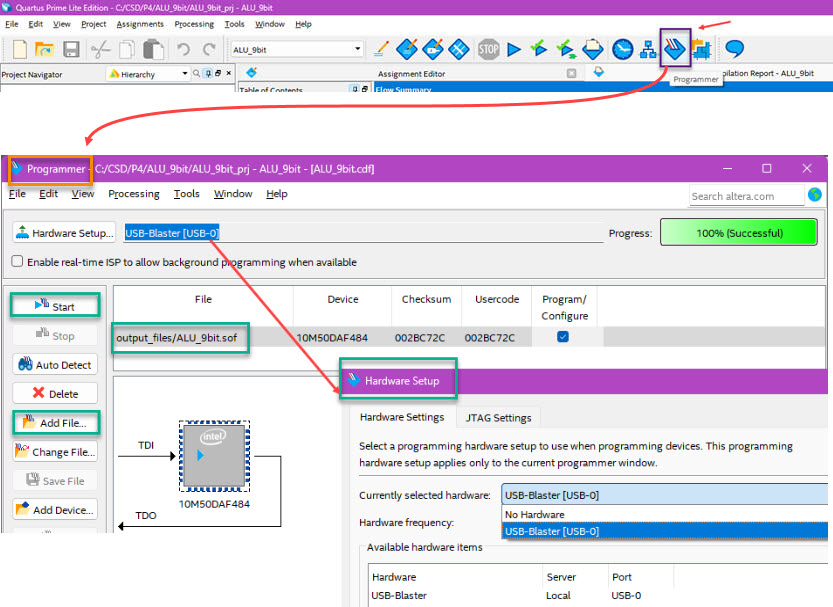

C) Upload the FPGA configuration (programmer tool)

Use the programmer tool to locate the target chip where to upload the configuration file. This is the final FPGA ALU_9bit_top.sof configuration file to be used directly by the Quartus Prime programmer (Fig. 22). The extension .sof stands for SRAM Object File.

![]()

Note: This FPGA configuration step can be executed directly from the programmer as an standardalone application even if Quartus Prime is not open.

NOTE: In case we like to write the configuration flash memory (CFM) of the FPGA and make the circuit permanent (not erased when unplugging the board), the programmer object file (.pof) is required instead: ALU_9bit_top.pof.

|

|

Fig. 22. Programmer application. It can work as an standard alone application. |

D) Run the circuit and test operations

The final board prototype performing an operation is pictured in Fig. 23 connected to the DE10-Lite. Apply several input vectors and annotate outputs when performing several logic and arithmetic operations, as a way to verify your pre-lab activity #1.

|

|

Fig. 23. Prototype connecting the inputs and outputs board to the DE10-Lite training board ready for running the truth table. An example of signed multiplication is visualised. |

And from now, when our prototype is verified and operating correctly, we are ready to perform laboratory measurements using the compact VB8012 instrument to observe additional circuit features. We can characterise the circuit's performance as if we had to write a kind of a datasheet or technical report for accompanying the product.

In this experiment we will measure static power consumption, propagation delay for a given input/output propagation path (from B(0) to flag C) and dynamic power when working at high speed.

E) Static power consumption

Static power

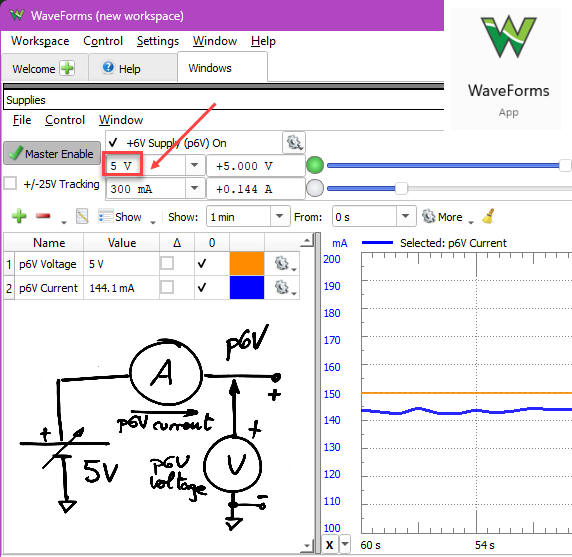

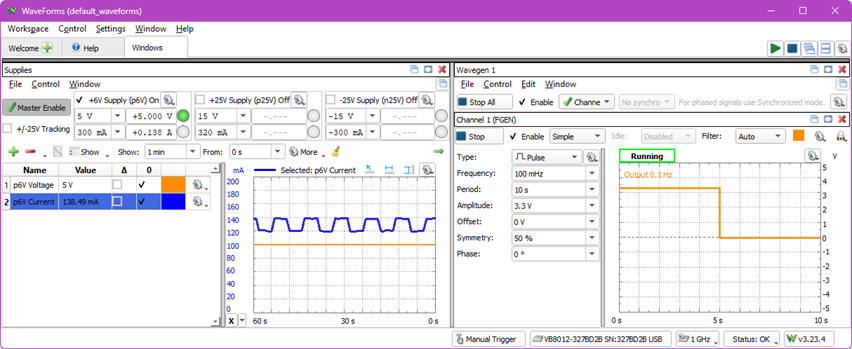

Connect the instrument VB8012 to the PC USB, run WaveForms app and screw the power supply cable as shown in Fig. 24. The DE10-Lite board will be powered from the instrument and its USB used only for uploading the FPGA configuration.

|

|

Fig. 24. The VB8012 p6V power supply adjusted to +5 V to drive the boards. Voltage and current readings wil be available. |

Calculate the static power consumption PS (mW) for several operations of the DE10-Lite. The measurement will include the power of all chips and and the power required to light the LED.

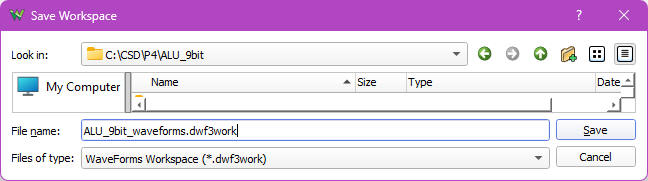

You can save the WaveForms setup workspace (file extension: *.dwf3work) as another file in your project folder, to speed up the instrumentation windows system, as shown in Fig. 25.

|

|

Fig. 25. Saving the WaveForms Workspace in the project folder. |

F) Propagation delay measurement

Let us characterise the internal Adder_9bit that has available the C (carry out) output connected to a test point pin (TP_C1).

Exceptionally, and only for this particular case, to carry out this OP = "100" experiment let us suppose that the operands are radix-2 numbers insteead of 9-bit integers as they are in normal arithmetic operations. The board's push-button RTN_L will replace the B(0) switch to be able to drive signals using a function generator.

|

|

Fig. 26. We will use male pins for both: drive B(0) externally connecting the instrument function generator Wavegen and for monitoring the Carry out (C) LED value. Place the J_C1 jumper cap on the male pins to connect the LED DL_C1 to visualise the C signal. |

The idea is to use two numbers A and B that will flip all result LED when adding OP = "100". Prepare two convenient values for A and B operands, for instance:

A(8..0) = 255 = "011111111"

B(8..0) = 256 / 257 = "100000000" / "100000001"

These values will switch all the result outputs when B(0) toggles from '0' (R = 511; C = '0' , R(8..0) = "111111111") to '1' (R = 512; C = '1' , R(8..0) = "000000000").

In this way we can visualise the Adder_9bit propagation path from B(0) to C in the logic analyser and oscilloscope.

|

|

Fig. 27. Driving B(0) with a square wave (pulse) from the function generator. Other output signals can be reassigned in the same way to measure for example the multiplier propagation delay. |

To carry out this measurement, the only hardware modification required is to reassign the pin B(0) from the switch at pin_AB2 to the push-button RTN_L at pin_W5. Re-synthesise the circuit in Quartus Prime importing this new assignment file ALU_9bit_prj.csv. These are the modified FPGA ALU_9bit_top.sof and ALU_9bit_top.pof configuration files where the B(0) signal is wired to RTN_L input pushbutton (pin_W5).

|

|

Fig. 28. Using the Pin Planner app to reasign the B(0) from the switch to the RTN_L push-button. |

Program the FPGA and check that B(0) is asserted when clicking the push-button RTN_L.

Let us use the test point header (TP_C1) in output C flag to visualise the signal. In this way we can measure the propagation delay using cursors, two oscilloscope channels and also two channels of the logic analyser.

Let us connect the Wavegen with a 1 Hz, 50% symmetry, 3.3 V pulse signal using the BNC-male to two alligator clip cable. Check that C LED toggles as previosly when using the push-button.

|

|

Fig. 29. Connecting the Wavegen to drive B(0) using a BNC-male to two alligator clip cable. |

From now, we can play modifying the signal frequency. Hence, let us visualise waveforms in the oscilloscope (CH1 --> B(0), CH2 --> C) and also in the logic analyser (DIN0 --> B(0), DIN1 -- > C).

|

|

Fig. 30. Two digital channels (DIN 0 and DIN 1) and two probes for the analogue channels CH1 and CH2. Adjust probe attenuation to 10 X. |

Compare and discuss your lab results with measurements from Quartus Prime timing analyser in Fig. 16.

The next picture Fig. 31 shows example printed waveforms with time cursor measurements. Discuss their validity or try diferent frequencies and configurations to see in which way the measurements makes more sense.

|

|

Fig. 30. Propagation delay tPHL and tPLH measurements examples using both analogue and digital signal acquisitions. |

Overshoot, sinusoidal ringing or damping and noise is appreciated at the oscilloscope signals at higher frequencies. Thus, the digital acquisition at 1 GS/s (1 ns resolution) captures this noise as extra digital pulses (signal bouncing). It is clear that long flat cables and standard probes do not allow much higher frequencies.

How to get rid of signal bouncing can be studied in another experiment. We can use specialised digital filters (debouncing filter).

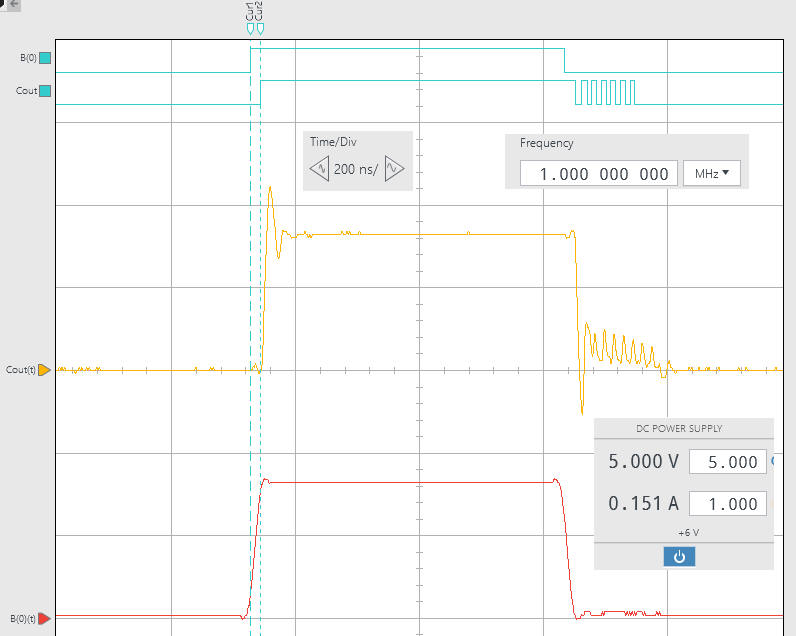

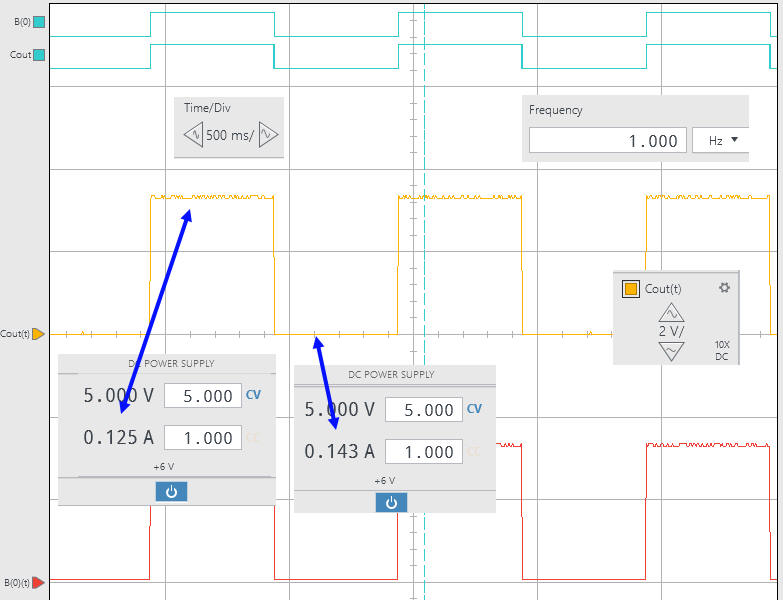

G) Dynamic power consumption

Dynamic power at 1MHz or 5 MHz

Measuring the total power consumption firstly at 1 Hz and secondly at 1 MHz (PS + PD = 755 mW), we can deduce the dynamic power of the FPGA chip at such frequency of operation PD = 85 mW.

|

|

Fig. 31. Power consumption. |

Note: Before finishing the lab session, using the Programmer, you can restore the configuration flash memory (CFM) of the DE10-Lite board to its original defaul application saved in this unit DE10-Lite.

Optional (out of the CSD scope). At this level, many more questions may be asked regarding results and waveforms from these experiments. For example:

- What is the effect of the long flat cable? What kind of circuit are required to drive digital signals over long wires?

- How to drive the same B(0) repeating the same experiments using an internal CLK signal that probably will generate clearer digital waves?

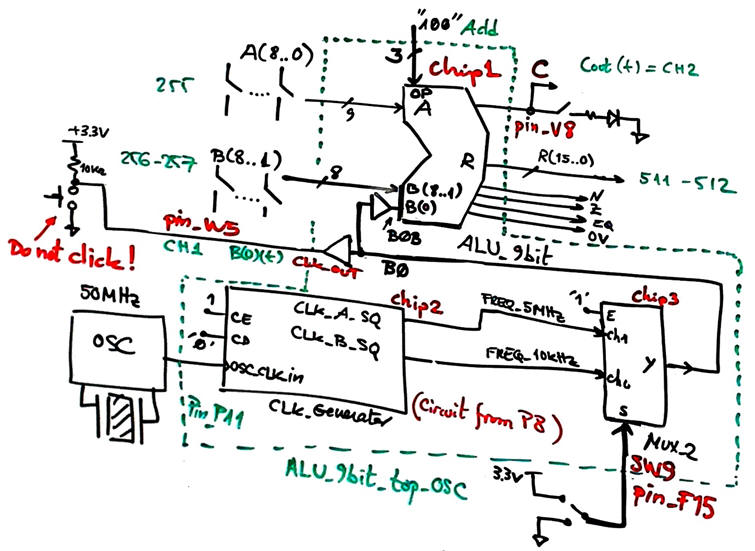

Fig. 32 shows the experient when using an internal CLK_Generator (from lecture L8.2). This is the full experiment in case you like to try it in the lab: ALU_9bit_top_CLK.zip.

|

| Fig. 32. Let us measure the circuit performance when using an internal CLK signal instead of the external VB8012 function generator. Let us see whether we can obtain clearer waveforms. B(0) used as output is available at the same pin W5 to be monitored at the oscilloscope CH1. |

And, after this initial question, many more advanced ones appear. For instance:

- How to design the PCB and the instrument probe setup so that signal bouncing, noise and ringing can be reduced or even eliminated to maintain signal integrity?

NOTE : A prototyping PCB board like this one expanding the DE10-Lite resources with many more input and outputs, once manufactured, can be used for other laboratory projects such counters, shift registers, etc. We just need to rename the wires in the KiCad schematic and reassign FPGA pins.

Annexes

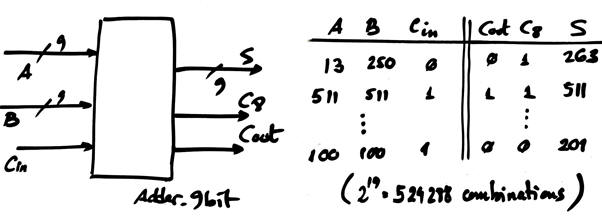

A1. Example of planning the Adder_9bit required in this project. We use the carry lookahead architecture already presented in LAB4_1 example: Adder_16bit.

|

|

Fig. 1. Adder_9bit symbol and truth table. |

We can invent and translate it as with other similar circuits: using plan C2 annotating all the signals and chips.

|

|

Fig. 2. Proposed Adder_9bit. |

This is the VHDL translation of the Fig. 2 schematic: Adder_9bit.vhd. This is the component Adder_4bit CLA that also includes the Chip2 Carry_Generator. This is the Chip3 Adder_1bit based for instance in plan A equations.