Chapter 3 problems |

- D3.9 - |

Water tank controller (µC - C) |

1. Specifications

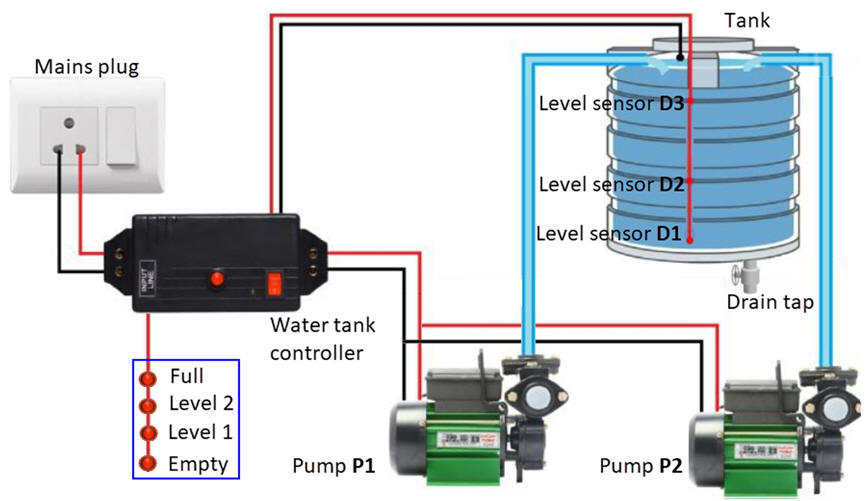

We want to design a water tank controller (Tank_cntl) as an application of FSM adaptation to µC that can drive two pumps independently, as represented in Fig. 1. Our target microcontroller is the PIC18F4520.

The tank has level sensors D1, D2, and D3 attached to the wall, so that a '1' is generated when the sensor is sunk into water. The controller works as follows: when the tank is empty, below D1, both pumps work simultaneously; when the water level is above D2 pump P1 stops; when the water is above D3, meaning that the tank is full, pump P2 stops; and finally, the pumps do not switch on until the water level is again below D1.

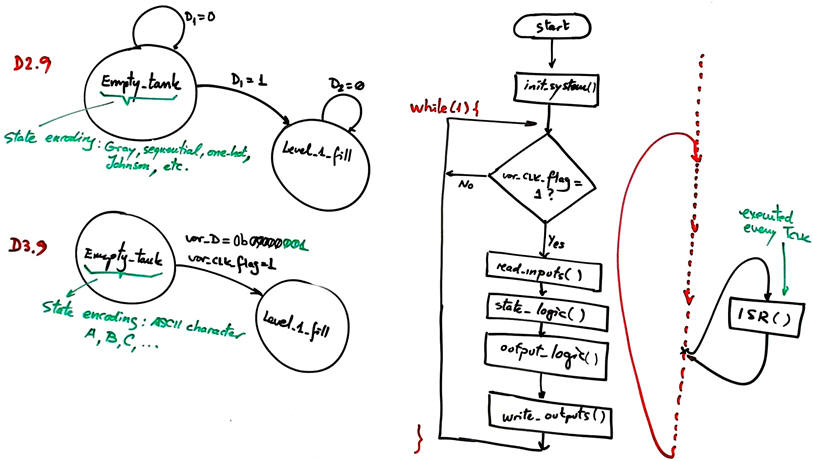

The same project designed using hardware is stated in D2.9.

|

|

Fig. 1. Diagram of the water tank installation. |

In addition to controlling the water level in the tank, we also want to indicate in a LED column and using a 7-segment digit the current level of the water in the tank. We can even add a tap valve to stop water drain when certain low level is reached.

In a new design phase we will include a real-time clock to measure how long does it take to empty the tank once full and the tap turns on.

Represent the Tank_cntl symbol and details. We well use a 1 kHz CLK signal to run the FSM, meaning that sensor inputs will be acquired and outputs will be written every 1 ms. Let us try to make the application synchronous to the external CLK as it was in Chapter 2.

|

|

Fig. 2. Tank sketch and symbol. |

Adapt the state diagram from D2.9 to this problem. Deduce which signals will be read and which will generate interrupts.

Draw an example of timing diagram.

|

|

Fig. 3. Timing diagram example. |

2. Planning

Design phase #1: basic features. FSM architecture, asynchronous reset (CD_L or MCLR_L), µC quartz crystal oscillator (OSC, 8 MHz), timing diagram, reading sensor inputs, writing outputs, RAM variables, state diagram, CLK interrupts. Solve the circuit for the design step #1. This means covering P9 and P10 circuits, concepts and ideas. Study, copy and adapt from examples in LAB10.

Project location:

C:\CSD\P10\Tank_cntl\(files)

- Design step #1. Consider an initial circuit only with the tank sensors, the pump outputs and the 4-LED column.

Thus, as shown in Fig 4, the initial develop & test will be simply for checking in a watch window that the FSM functions are executed only when the external CLK interrupt is detected. This is a way of implementing with a µC the concept of synchronisation.

|

|

Fig. 4. State diagram and main program adaptation. In this way the FSM functions are is executed only after having detected a CLK rising edge. In Chapter 2 version, we sample the detector values and encode state labels using several binary codes as an option. In Chapter 3 version, the FSM depends on RAM variables and we encode state labels all the time in the same way: using a char type RAM variable var_current_state defining state labels as ASCII characters A, B, C, etc. |

List the required RAM variables and their type. Some of these variables are used as control signals and outputs in the state diagram in Fig. 3.

|

|

Fig. 5. RAM variables list. |

Draw the hardware/software diagram explaining how the FSM is solved in software.

|

|

Fig. 6. Hardware-software diagram. |

A) Planning hardware

Draw the hardware schematic. Switches and resistors to represent sensors. LED to represent pumps and also the water level. You can also use power drivers and DC motors to model water pumps. Reset circuit MCLR_L and an 8 MHz quartz crystal oscillator. External CLK oscillator block. Which pins will interrupt? Which will be read? Assign inputs and outputs to µC port pins.

|

|

Fig. 7. Hardware used in this application. |

B) Planning software

Draw the software flowchart organised as a FSM (compllete and explain the ideas presented in Fig. 4)

|

|

Fig. 8. Software organisation and the idea of FSM adaptation. |

Draw the main ideas of init_system(). Configure input and output pins. Consider as well interrupt configuration bits to enable external interrupts.

|

|

Fig. 9. TRIS configuration bits. |

Draw the flowchart, memory diagrams and C instructions of read_inputs() function to poll input voltages as in P9.

|

|

Fig. 10. How to read inputs. |

Draw the flowchart, memory diagrams and C instructions of write_outputs() function to write pin voltages as in P9.

|

|

Fig. 11. How to write outputs. |

Infer how to organise the interrupt service routine ISR() to handle CLK's falling edge detections.

|

|

Fig. 12. Interrupt service routine flowchart. |

And now, it is necessary to discuss how to transfer all the state transitions into a truth table.

Draw state_logic() truth table and its equivalent flowchart.

|

Fig. 13. Truth table for state_logic() function and its equivalent behavioural plan B flowchart. |

Draw output_logic() truth table and its equivalent flowchart.

|

Fig. 14. Truth table for output_logic() function and its equivalent behavioural plan B flowchart. |

3. Development & 4. Test

Develop and test (debugging) the project capturing the hardware circuit in Proteus and writing the C source code. Do not start your hardware circuit and software source file from scratch, but copy and adapt from examples in LAB10 or P10.

- Design step #2. Add a 7-segment display level indicator. Add a tap valve.

Go ahead with the step #2 only when step #1 is fully tested working correctly.

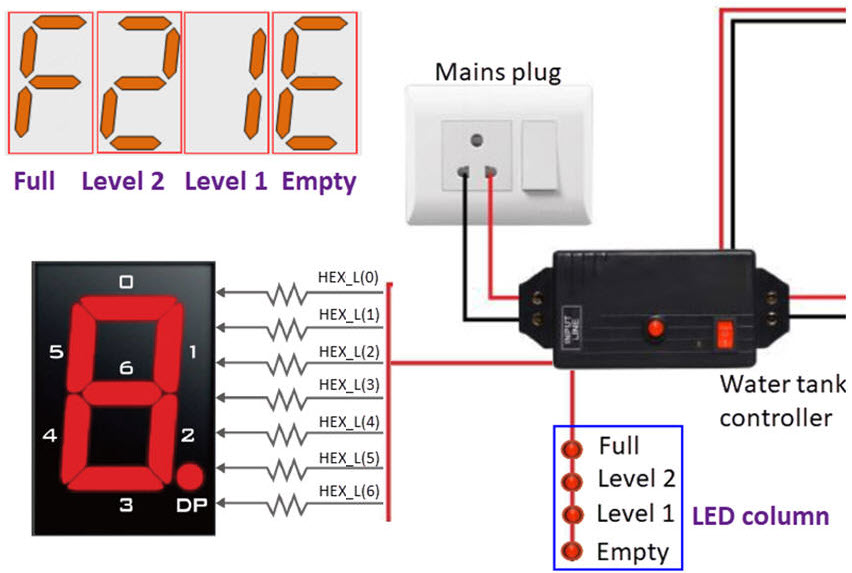

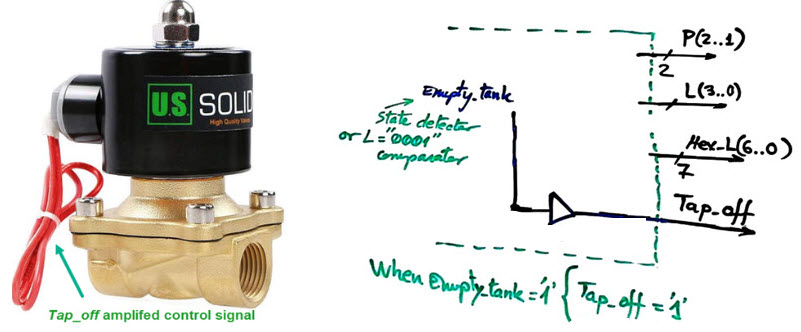

The user wanted to add an extra circuit to translate the LED column code into a 7-segment display. Thus, an additional combinational circuit is required to meet this new specification. The wiring in Fig. 15 shows the naming conventions for the vector HEX_L(6..0) common anode.

|

Fig. 15. Enhancement with a 7-segment display to display the symbols "F", "1", "2", and "E". |

Add a tap electric solenoid valve to switch off the water flow when the tank is below Level 1.

|

Fig. 14. Example of a commercial electric solenoid valve 220 V / 50 Hz and new output signal for controlling it. |

Design phase #2: advanced features to interface an LCD display.

Only when design phase #1 is fully tested working correctly and reported, solve the design phase #2 as advancing to cover P11 materials.

Project location:

C:\CSD\P11\Tank_cntl_LCD\(files)

Let us add an LCD display to this application. The idea is represent the water level and pump activity using ASCII characters and symbols.

Enhance the schematic from design phase #1 to include an LCD attached to port D as studied in tutorials.

Enhance the software and the source file to drive the LCD.

In this phase there is also the possibility of two design steps, such step #1: print ASCII text messages; step #2: print as well numbers from 1 to 4 to indicate tank level from empty to full.

Design phase #3: On the use of internal peripherals to reduce components and board size.

Only when design phase #2 is fully tested working correctly and reported, solve the design phase #3 as advancing to cover P12 materials.

Project location:

C:\CSD\P12\Tank_cntl_LCD_TRM2\(files)

The external CLK is replaced by the internal 8-bit TMR2 peripheral to generate interrupts (TMR2IF). In this way, we will save power consumption, reduce board footprint, and also free an external INT for other future applications.

Calculate TMR2 parameters required to generate a CLK of 1 kHz (var_CLK_flag period = 1 ms) to run the machine.

You can add other features, for instance, a 2 kHz sound wave for a buzzer to indicate an alarm on empty tank.