|

|

||

|

|

BCD counter modulo 60 (seconds or minutes counter) |

|

|

|

||

| 1. Specifications | Planning | Developing | Test functional | Test gate-level | Report | Prototype |

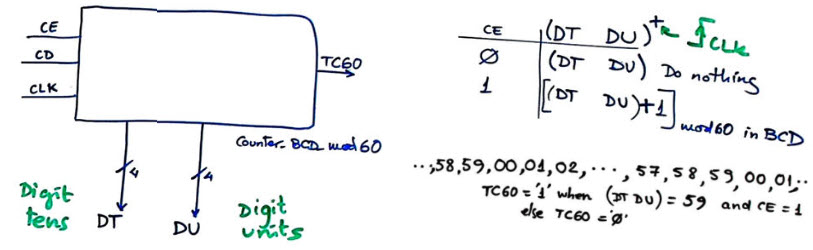

Our goal is to design a minutes or seconds counter to be used in real-time clock devices. Fig. 1 represents the symbol and its function table. It is intended to count cyclically in BCD code from 00 up to 59. This is way we name it modulo 60.

Firstly, we can imagine the circuit for counting only up. And, in a second step we can add the reversibility for counting up and down.

|

Fig 1. Initial symbol and idea of operation for the proposed 2-digit BCD counter up to modulo 60 |

|

|

Fig. 2. Timing diagram example. |

| Specifications | 2. Planning | Developing | Test functional | Test gate-level | Report | Prototype |

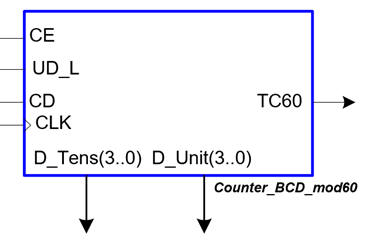

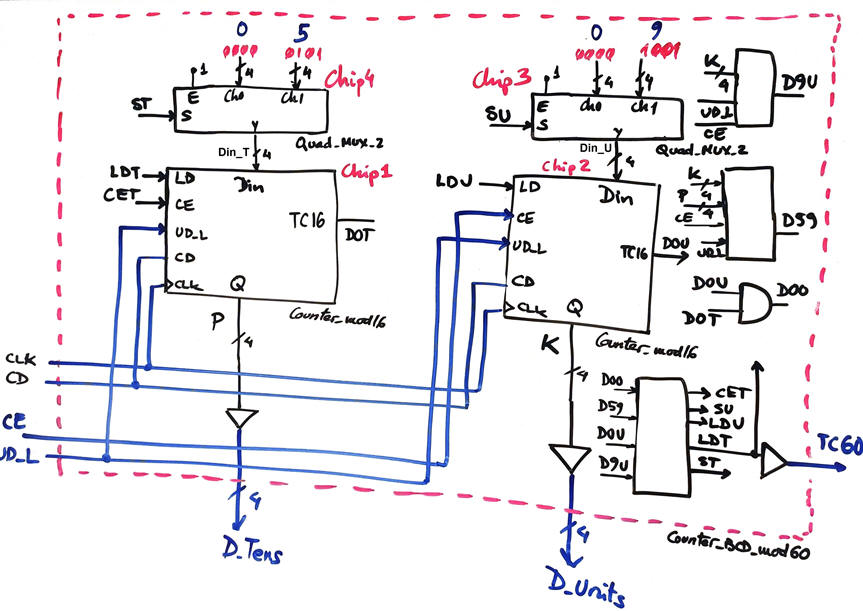

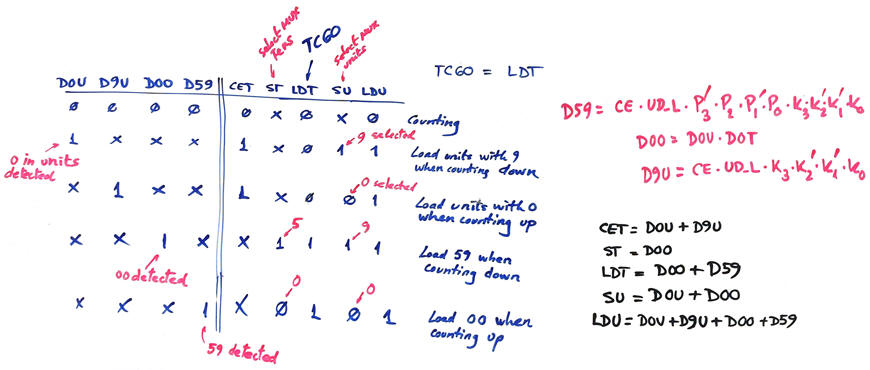

Let us use plan C2. Inventing the Counter_BCD_mod60 requires chaining Counter_mod16 components using truncation techniques in the way discussed in lecture L7.3. We can adapt the counter BCD modulo 24 proposed in our highlighted project P7. Thus, the new symbol will include reversibility for counting up and down.

|

|

| Fig 3. Proposed internal architecture for Counter_BCD_mod60. |

Project location:

C:\CSD\P7\Counter_BCD_mod60\(files)

| Specifications | Planning | 3. Developing | Test functional | Test gate-level | Report | Prototype |

Example file translation of schematics above in Fig. 3: Counter_BCD_mod60.vhd, Quad_MUX_2.vhd, and copy the Counter_mod16.vhd from its plan Y tutorial Counter_mod16.

You can use Quartus Prime and any convenient Intel FPGA, for instance a Cycplone IV, as target chip to synthesise this project.

|

|

Fig. 4. RTL |

|

|

Fig. 5. Technology view and resources used in the design. |

| Specifications | Planning | Developing | 4. Test functional | Test gate-level | Report | Prototype |

The testbench fixture.

|

|

Fig. 6. Testbench fixture for connecting stimulus process to the unit under test. |

|

|

Fig. 7. ModelSim wave diagram. |

| Specifications | Planning | Developing | Test functional | 5. Test gate-level | Report | Prototype |

In this section we can repeat measurements simulating propagation delays

|

|

Fig. 8. ModelSim wave diagram zooming a transition for measururing the parameter propagation time from CLK to output tCO. |

| Specifications | Planning | Developing | Test functional | Test gate-level | 6. Report | Prototype |

Follow this rubric for writing reports.

| Specifications | Planning | Developing | Test functional | Test gate-level | Report | 7. Prototype |

We built and use this module in several training and demonstration designs:

A) Timer_MMSS, P8 highlighted project as one of the components of the Counter_BCD_MMSS.

B) Prototype in a legacy NIOS board. Target chip: APEX EP20K200EFC484-2X.

C) Prototype in a legacy UP2 board. Target chips: EPM7128SLC84-7 and FLEX EPF10K70RC240-4.