Legacy hardware: Altera UP2 board |

| Prototype specifications | Planning | Development and Test & Measurements |

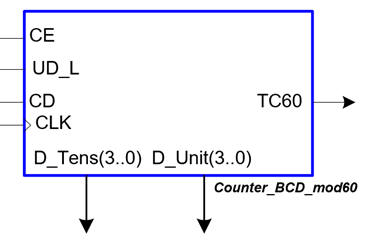

Let us adapt the Counter_BCD_mod60 represented in Fig. 1 for the Altera UP2 board populated with two obsolete target chips: a CPLD MAX128S and an FPGA FLEX10K. This board has been a staple for decades in teaching and learning digital systems around the world. It comprises two independent sections: the CPLD and the FPGA.

|

|

Fig. 1. Symbol of the basic counter. |

We will add some additional features to the top design, such:

- Switch for selecting two CLK frequencies for fast (20 Hz) and slow (1 Hz) counting (Sel_CLK_freq)

- Count enable switch (CE)

- Switch for counting up or down (UpD_L)

- Switch for selecting manual or internal oscillator CLK signal (Sel_pulse)

- Switch for selecting raw CLK input from the push-button (CBL_L) or debounced and filtered pulse (Sel_filter)

- TC60 LED indicator, terminal count, one pulse every 60 rising CLK edges.

- Tens and units 7-segment displays to show the current counter count.

- LED ticking at 1 Hz (LED_CLK_1Hz_SQ)

- LED for indicating manual CLK (LED_CLK_pulse)

This is the time for reviewing the UP2 board hardware. Unfortunately, Intel - Altera has long ago discontinued such product, thus we will use software and documentation from the board's CD and DVD. Review:

-Basics of CPLD and FPGA.

- CPLD MAX7000 architecture. Number of logic elements available for experimetation.

- FPGA FLEX10K architecture. Number of logic elements available for experimetation. Is there a comfiguration ROM where to save the *.pof file?

- How to configure the CPLD or the FLEX device using a JTAG configuration (*.sof RAM file).

- Electronic schematic. Which board resources are easy to use for an introductory level project? User switches, LED, push-buttons, 7-segment displays, etc.

| Prototype specifications | Planning | Development and Test & Measurements |

We will follow the steps:

1. Develop and test functionally the application in Quartus Prime. Project folder:

C:\CSD\LEGACY\UP2\Counter_BCD_mod60_top\(files)

2. Copy the project's VHDL source files in the Window 7 VM for resynthesising using Quartus II 9.0, an edition in which we still can use MAX7128S and FLEX10K as target chip families. Assign pins and generate the configuration files: *.sof,*.pof. Project folders in Windows 7:

C:\CSD\UP2_FLEX\Counter_BCD_mod60_top\(files)

C:\CSD\UP2_MAX\Counter_BCD_mod60_top\(files)

3A. MAX7128S. Use the JTAG interface to configure the CPLD with the *.pof file. This configuration is non-volatile, when powering off and on the board the CPLD keeps its configuration.

3B. FLEX10K. Use the JTAG interface to configure the FPGA with the *.sof file. This configuration is volatile, when powering off and on the board the FPGA do not keep its configuration.

The following fully annotated plan C2 schematic is proposed for this adaptation to the FPGA board.

|

|

Fig. 2. Counter_BCD_mod60_top adaptation. We can select the way to input CLK pulses. |

| Prototype specifications | Planning | Development and Test & Measurements |

Developing will be integrated with testing for each of the planned steps. We can only go ahead when the current steps works correctly.

1. Quartus Prime project

To complete the synthesis and functional testing of our application, we can develop the project using our current Quartus Prime EDA. At this stage we can select any target FPGA.

The only circuit to which pay some attention is the CLK_Generator, to be adapted to the 25.175 MHz quartz crystal available in the UP2 board. The first frequency divider is N1 = 125875.

This is the list of VHDL files included in the design: Counter_BCD_mod60_top.zip.

|

| Fig. 3. No complications are expected in this RTL view because the main project is our standard Counter_BCD_mod60 used in many other CSD applications for counting minutes or seconds. We are expecting 42 D_FF. |

The UP2 user manual indicates how to configure programmable devices and assign pins. Fig. 4 is elaborated from datasheet information.

|

|

Fig. 4. UP2 board layout indicating pin connections to LED, switches and 7-segment displays. |

2. MAX7128S Quartus II project. Pin assignment, configuration files

In this next stage, we can switch computers and tools to be able to target the obsolete MAX7128S and FLEX10K devices. Let us use the VM running Windows 7 and Quartus II version 9.0. Use the shared drive to copy the VHDL source files.

|

|

Fig. 5. Shared folder C:\CSD\VM_W7 between Windows 1 and the Window 7 VM. |

Let us start a new VHDL project for the MAX7120S FPGA including all the imported VHDL files. If we have to use the same environment for different legacy chips, it is convenient to organise the projects in separated folders. For instance:

C:\CSD\UP2_MAX\Counter_BCD_mod60_top\(files)

This is the top project to be opened in Quartus II Counter_BCD_mod60_top_MAX.zip.

Once the project synthesised with no errors, we can use the pin planner tool to assign pins as shown in Fig. 6 and re-synthesise the project to obtain the output configuration file. In this way, the Counter_BCD_mod60_top_MAX.pof will be ready for programming the CPLD in the next step.

|

|

Fig. 6. Pin assignments can be saved in a file Counter_BCD_mod60_top_MAX.csv ready to be imported to the Quartus II project. |

3. JTAG, *.pof

Let us use the MAX-II micro kit as an USB Blaster cable connecting it as indicated in Fig. 6.

|

|

Fig. 6. Using the MAX-II micro kit as a USB blaster cable for configuring the MAX7128S CPLD. |

Be aware of connecting the JTAG interface for detecting MAX7128S.

When ready, use the programmer tool installed in your Windows 11 computer to locate the target chip where to upload the configuration file. This is the sof file

|

|

|

Fig. 7. Programmer application. It also works as an standard alone application. |

This CPLD configuration step can be executed directly from the Programmer as an standard-alone app. Let us use the *.pof file for the CPLD produced above in Quartus II. The MAX7128S will be detected in the JTAG chain as shown in Fig. 8.

|

|

Fig. 8. The MAX7128S is the only programmable device attached to the JTAG chain. |

Check that the UP2 board works as expected running the Counter_BCD_mod60_top configuration.

Check how the Debouncing_filter FSM is required (Sel_filter switch) when clicking the push-button for applying CLK pulses to the counter.

2. FLEX10K Quartus II project. Pin assignment, configuration files

Target FLEX10K. In this stage we can repeat this experiment for the FLEX10K FPGA.

C:\CSD\UP2_FLEX\Counter_BCD_mod60_top\(files)

This is the full project Counter_BCD_mod60_top_FLEX.zip ready for Quartus II.

Once the project synthesised with no errors, we can use the Pin Planner tool to assign pins as shown in Fig. 9 and re-synthesise the project again for obtaining the output files Counter_BCD_mod60_top_FLEX.sof and Counter_BCD_mod60_top_FLEX.pof.

|

|

Fig. 9. Pin assignments can be saved in file Counter_BCD_mod60_top_FLEX.csv ready to be imported to the Quartus II project. |

Let us use the Programmer app in standard-alone mode to download the configuration file to the FLEX device detected in the JTAG chain.

|

|

Fig. 10. Programmer detecting the FLEX10K and ready for configuring it. |

Board running the application in the FLEX10K section of the board.

|

|

Fig. 11. Board UP2 running the application in the FLEX10K section. |

With SRAM-based FPGA, configuration data is volatile; it must be reloaded each time the system initializes, or whenever new configuration data is needed. A serial EPROM EPC1 (1 Mb memory addressing, 1-bit data: 1,046,496 x 1) stores configuration data for SRAM-based FLEX devices. However, in this application we are not going to use the pof file because the board contains only the socket for such EPROM. Besides, this chip is one-time-programmable (OTP) not compatible with JTAG, requiring obsolete equipment such the master programming unit (MPU) and adapters from third companies. Current boards such the DE10-Lite allows the user to program the EPROM by means of the JTAG interface.

|

Fig. 12. Datasheet schematic showing how the EPC1 EEPROM is connected to the FPGA FLEX10K. |