|

|

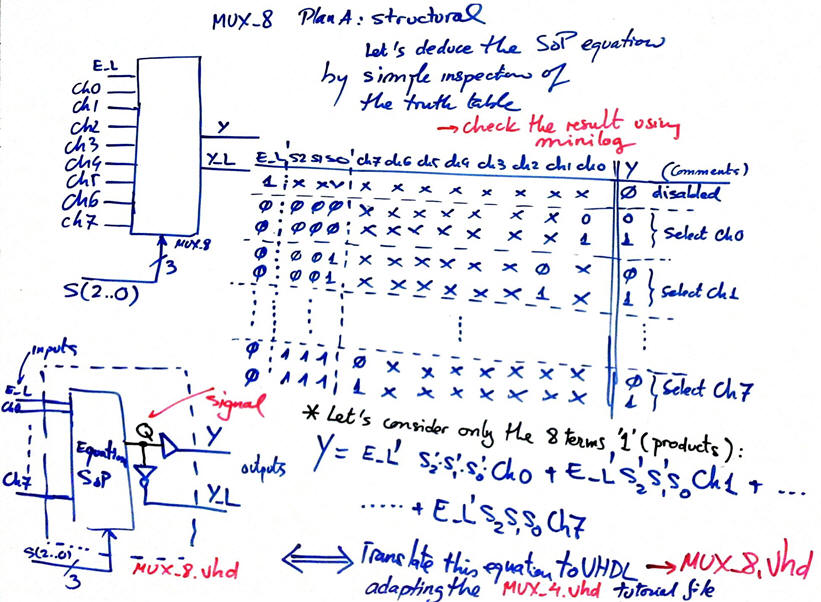

MUX_8 plan A: structural single-file VHDL with equations |

8-channel multiplexer

| 1. Specifications | Planning | Developing | Functional test | Gate-level test | Prototype | Report |

Design a MUX_8 with characteristics similar to the classic 74HCT151 chip in a programmable logic device (PLD) target chip following structural plan A using our VHDL design flow and EDA tools for developing and testing.

|

Fig. 1. Package and pin enumeration of classic 74HCT151 chip. We have to interpret and rename the pins because each company has its own way to name inputs/outputs and organise product datasheets (Nexperia, Toshiba/Renesas, ON semiconductor, Texas Instruments 74HCT151, etc.); thus, in CSD we have decided to use our own naming style and rewrite the truth table accordingly. For instance, the pin 12 will be always our input Ch7, an so the same with all the other pins. The technology of the logic family (TTL, LS, S, CMOS, AS, HC, HCT, F, etc.) is not important because the circuit will be targeted for a PLD from Intel, Xilinx or Lattice Semiconductor. Thus, only the chip functionality is considered. |

Fig. 2 shows our MUX_8 symbol adaptation.

|

|

| Fig. 2. Symbol adapted from datasheets. A multiplexer is a data selector. |

In Fig. 3 is represented the circuit's truth table using don't care terms.

|

|

|

Fig. 3. Truth table. The circuit has twelve inputs, it means 4096 binary combinations. |

|

| Fig. 4. Example of a timing diagram sketch to demonstrate how the circuit works for different inputs. This input activity will be translated to VHDL as a stimulus process in the simulation testbench (Fig. 10). |

Find and study similar products, like MUX_16, MUX_4, MUX_2 and also demultiplexers.

In this project we will apply our VHDL design flow using plan A: flat (single-file) structural VHDL project. Take some time studying this specifications and how a structural plan will look like (rec.). Is it possible or easy) to write canonical equations based on minterms or maxterms?

This is the general concept map rec. to design most of CSD circuits.

| Specifications | 2. Planning | Developing | Functional test | Gate-level test | Prototype | Report |

Fig. 5. may be a sequence of operations for inventing MUX_8 in a single-file VHDL project using plan A.

|

| Fig. 5. Planning the development (synthesis) of the circuit. |

The verification of the circuit under test may be carried out following Fig. 6 sequence.

|

| Fig. 6. Testing procedure. |

For the next developing section, we have to find equations from circuit's truth table. Therefore, in this example, we have two ways: (1) inspecting the truth table, as we did in lecture L2.1 or (2) applying the minimiser algorithm Minilog.

|

| Fig. 7. Schematic with equation SoP deduced observing the truth table and ORding the ones. Output Y_L is implemented using an inverter. Explain what is a port and what is a signal. |

Project location. For instance, you can save the project based on SoP here:

C:\CSD\P2\MUX_8A_SoP\(files)

Alternatively, other students may solve the project using PoS at the location:

C:\CSD\P2\MUX_8A_PoS\(files)

Find a similar VHDL circuit in P2 with an architecture that uses logic equations to copy and adapt.

| Specifications | Planning | 3. Developing | Functional test | Gate-level test | Prototype | Report |

Find minimised equations PoS or SoP running Minilog. This is an example Minilog file "MUX_8.tbl" capturing the truth table to obtain a simplified equation.

|

| Fig. 8. Minilog results in SoP format. |

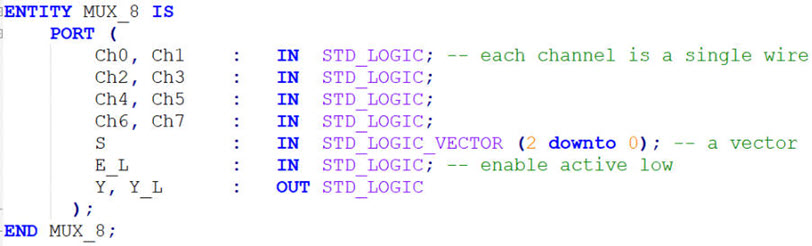

Find a similar VHDL circuit file in P2 with an architecture that uses logic equations to copy and adapt. This is a VHDL translation source file "MUX_8.vhd" that corresponds exactly to our plan in Fig. 7 using SoP. The entity name is related to the symbol in Fig. 2. Note that in this symbol channel inputs are not considered as a vector but as individual wires.

|

| Fig. 9. Description of the entity is the same for all design plans. |

KEY NOTE in CSD: Do not write VHDL code without the corresponding printed schematic / e equation / diagram / flowchart / algorithm from the previous planning section. Here in CSD, VHDL source file is always a direct translation of your handwritten sketches. Submitted VHDL files, project developments and testing will not be marked unless they go accompanied by specifications and planning discussion. Be aware also about your commitment to academic integrity at the UPC.

Name the project MUX_8_prj and use one of the EDA tools to implement it selecting a target programmable chip (sPLD, CPLD or FPGA) from our laboratory training boards. For instance, use Intel MAX II CPLD EPM2210F324C3.

|

| Fig. 10. Project name, location and top entity. Synthesis summary. |

Synthesise your circuit and examine results. Print, analyse and comment the computer generated RTL and technology views or schematics of the circuits.

|

| Fig. 11. RTL schematic of a MUX_8 generated by Quartus Prime when using SoP equation. |

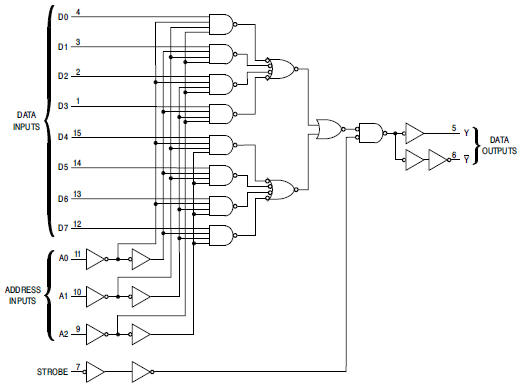

Our RTL circuit is not that different from the schematic proposed by vendors like ON Semiconductor. Chip 74HCT151 implements product terms using NAND.

|

Fig. 12. For discussion and comparison purposes, this is the schematic of a 74HCT151 MUX_8 from ON Semiconductor datasheet. |

In Quartus Prime we can inspect how the real circuit is implemented attending the chip resources and internal architecture using technology schematic viewer and chip planner tools.

|

Fig. 13. Technology view for target chip Intel MAXII EPM2210F324C3. How many resources (logic cells) are used? |

What kind of technology contain this MAXII CPLD? For example, from MAX II 300 pages handbook (page 77) we can calculate noise margins of its input/output buffer elements (IOE). Fig. 14 shows DC characteristics of the LVTTL and LVCMOS I/O standards powered at 3.3 V.

|

Fig. 14. Calculate the NMH and NML from these tables. |

| Specifications | Planning | Developing | 4. Functional test | Gate-level test | Prototype | Report |

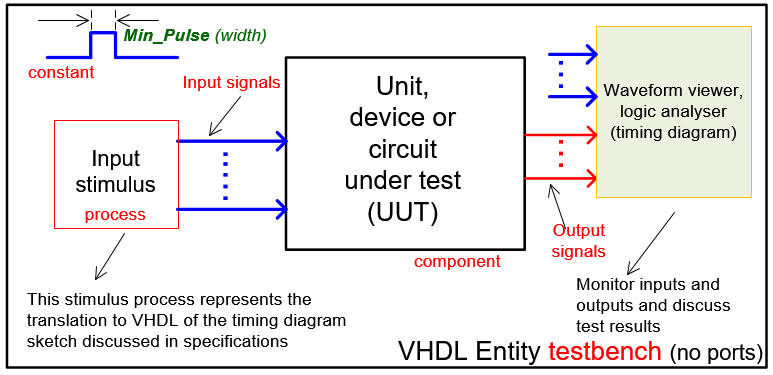

To test the synthesised design, whatever it is its internal architecture from plan A, plan B or plan C2, we use the same testbench fixture. Even if you have different internal architectures for the UUT (unit under test), the entity definition is always the same, as shown in Fig. 15, and thus the same testbench to apply stimulus can be used again.

|

| Fig. 15. Testbench VHDL schematic fixture. |

Generate the template of the VHDL simulation testbench from Quartus Prime. The name of the file will be: MUX_8_tb.vhd (if the tool generates the file MUX_8.vht rename and move it into the project folder).

This is an example of testbench "MUX_8_tb.vhd" file representing the translation into VHDL of the schematic in Fig. 15. Waveforms in Fig. 4 are placed in "tb : PROCESS " as example stimulus.

Start an EDA VHDL functional simulation project (ModelSim) to verify the device-under-test (DUT).

Run the simulation process with only a few input vectors to see if the whole simulation process works and you are able to watch correctly input and output signals activity. Add more test vectors to verify how the information of each channel is selected.

-

What value are you choosing for Min_Pulse? How long will be necessary to run the simulation for the stimulus represented in Fig. 4?

-

How long does it take to simulate the complete truth table imagining that all stimulus vectors have the same duration 2.3*Min_Pulse?

Useful hints in ModelSim. You can order the signals as in the initial sketch in Fig. 4 for a better interpretation of the truth table and simulation result.

|

|

Fig. 16. Order the entity input and output ports as in the initial sketch. |

You can save and restore this signal setup in a convenient wave.do file, as shown in Fig. 17, so that it can be reused in other simulations of the same entity.

The instrument setup can be saved as a convenient wave.do file in your project folder as shown in Fig. 17 and reused again for other simulations of the same entity.

|

| Fig. 17. Save and restore the instrument setup in a txt file wave.do (its format type is TCL language). |

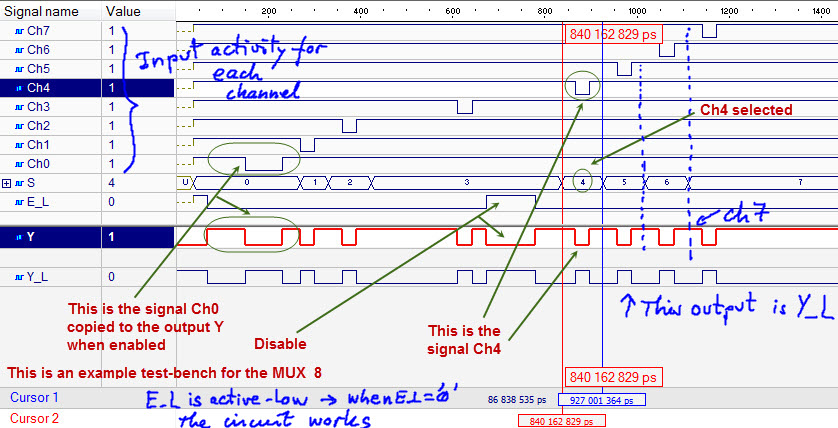

Print the timing diagram screen and add comments on the signals to show how the device works. Fig. 18 shows an example of commented test bench results from the logic analyser (wave) available in the EDA simulation tool. Use coloured pens.

|

|

Fig. 18. Example of a timing diagram produced by the simulator with some mandatory comments and discussion on the way the circuit works. |

You can change the radix in which signals are represented. For instance, in this MUX_8 circuit, the vector S(2..0) can be displayed in radix-2 or in radix-10, as shown in Fig. 19 and Fig. 20 below.

|

|

Fig. 19. Select the signal of interest S(2..0) to change to binary radix-2 representation. |

|

|

Fig. 20. Select the signal of interest S(2..0) to change to radix-10 (unsigned decimal). |

| Specifications | Planning | Developing | Functional test | 5. Gate-level test | Prototype | Report |

| Specifications | Planning | Developing | Functional test | Gate-level test | 6. Prototype | Report |

| Specifications | Planning | Developing | Functional test | Gate-level test | Prototype | 7. Report |

Follow this rubric for writing reports.