|

Installing and using Proteus-ISIS (current release 9.1 SP4) |

||

Computer simulation (virtual electronics laboratory) based on SPICE algorithms

(1) Install (2) Example (3) Mixed components (4) Subcircuits (5) Pattern generator (6) Scripting (7) Arduino

1. Installation

2. Example of a simple "flat" circuit

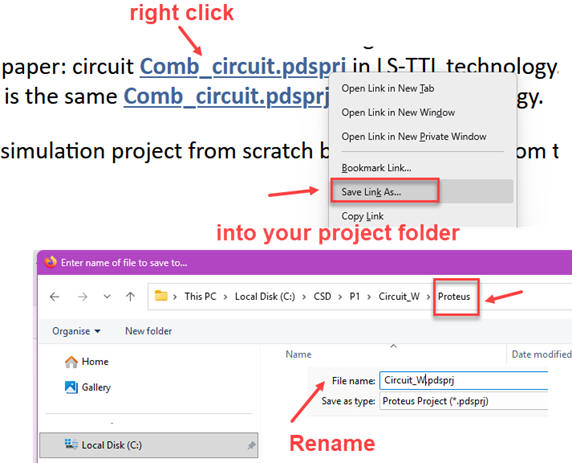

Capture a logic circuit in a Proteus project, and run simulations with the aim of obtaining its truth table. This is a simple flat capture, plan A, all the design at the same sheet of paper: circuit Comb_circuit.pdsprj in LS-TTL technology. It can be copied and adapted for other similar projects. This is the same Comb_circuit.pdsprj in CMOS technology.

|

Fig. 2.1. In your Firefox browser and using the mouse's right click option "save the link as", copy the example file into your project directory and rename it. |

NOTE: For your CSD assignments never start a new simulation project from scratch but copy & adapt from the many examples available in digsys. The procedure for capturing and debugging your circuit is to change one gate at a time and run to verify that it works.

|

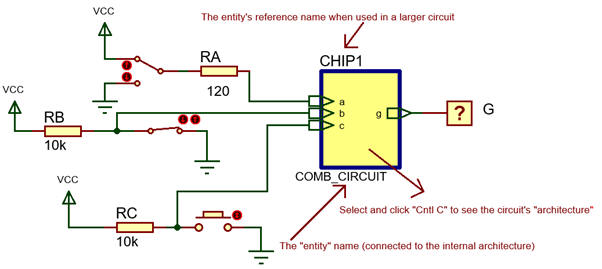

Fig. 2.2. A simple circuit that you can use as a template to be adapted to your design. This is a tutorial form the company Labcenter. |

This is another LS-TTL circuit Circuit_W.pdsprj adapted from above examples. This is an ideal version Circuit_W.pdsprj with generic gates and logic levels which is better not to use.

NOTE on how to make invisible the <TEXT> field associated to each component (Fig. 2.3). Menu Template->Set Design Default and uncheck the option "Show hidden text" in the following dialog:

|

|

Fig. 2.3. Hiding the component's <TEXT> field. |

3. Interfacing different types of real components

The circuit in Fig. 3.1 is another version Circuit_W_real.pdsprj where you can add to the digital electronic circuit Chip1 some buttons, switches, LEDs and even relays and motors. Play with the circuit and pay attention to the real voltages and currents that represent '0' and '1' symbolic logic values.

| |

Fig. 3.1. Another digital circuit including real components (click the picture to zoom) to interface buttons and power loads. |

In Fig. 3.2 there is the detail of a power driver based on a simple bipolar junction transistor (BJT) and an electromechanical relay.

|

Fig. 3.2. Logic gates manage µW of power, but conveniently amplified, can easily drive electric loads. In this example a kW motor is switch ON and OFF. |

4. Example of a hierarchical design using components (subcircuits)

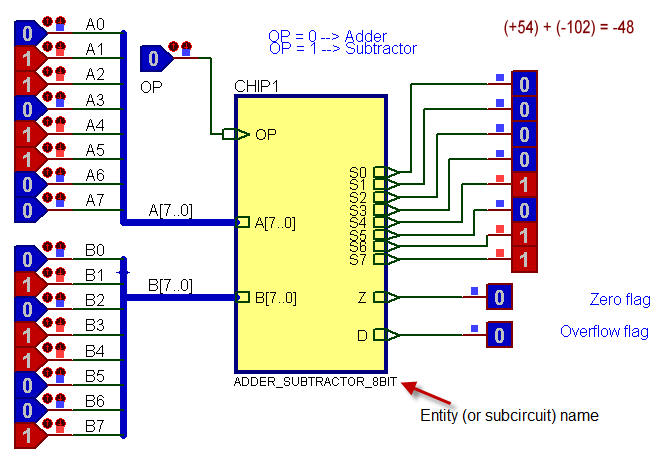

Adder_subtractor_8bit.pdsprj occupies multiple structured hierarchical sheets of paper (plan C2). Such top-down circuit organisation that will allow us to draw large circuits will be studied from P3 sketching schematics and translating them to VHDL.

|

Fig. 4.1. The subcircuit block allows packing circuits in boxes or "entities" that can be used many times in the same schematic. This example can be taken as a hierarchical template circuit to copy and adapt. |

5. Pattern generator instruments for providing stimulus digital signals

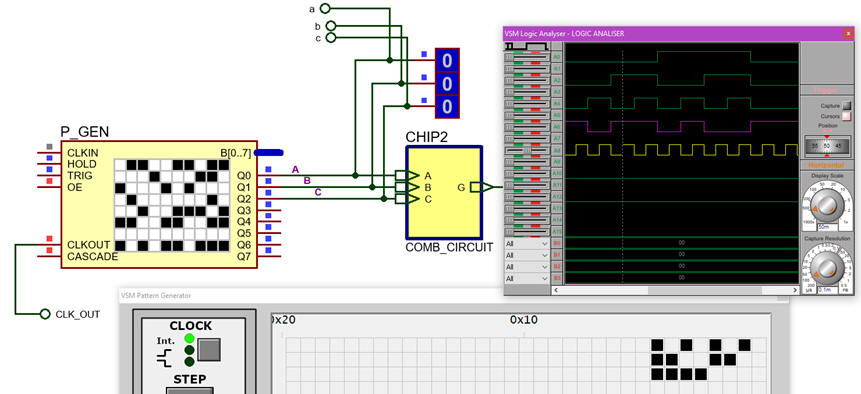

Fig. 5.1 represents yet another way to visualise the circuit truth table stimulating the circuit using a pattern generator instrument. In this simple case we are sending the eight values of the truth table G = f( C, B, A) repeatedly every second to the circuit. Circuit file: "Comb_cir_pattern_gen.pdsprj", pattern file: "truth_table_pattern_gen.PTN".

|

| Fig. 5.1. Using the pattern generator to stimulate a circuit with digital signals. |

A similar instrument is presented in Fig. 5.2, the multi-purpose generator that can be used to drive CLK signals or generate any digital pattern.

|

| Fig. 5.2. Configuring the DPATTERN generator. |

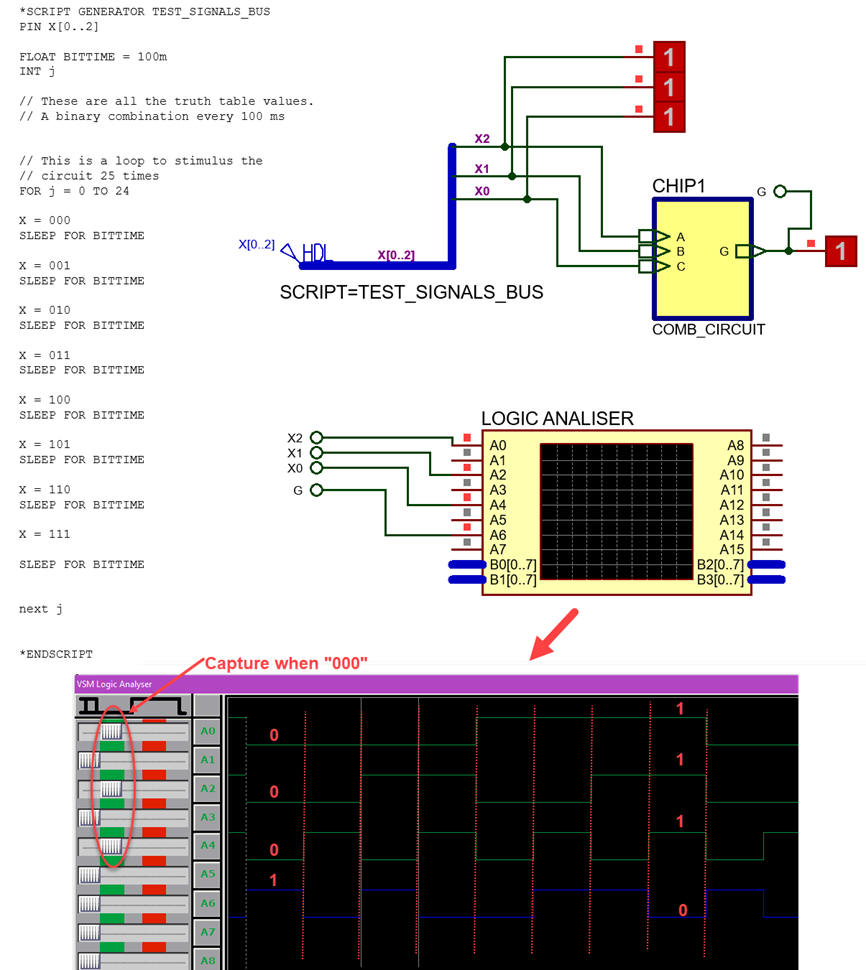

6. Scripting language Easy HDL

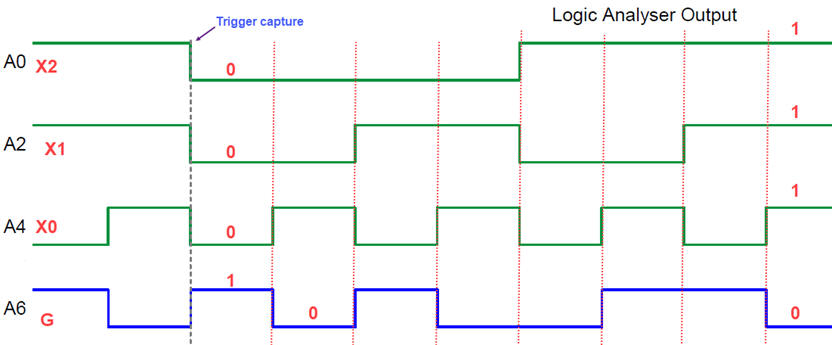

Sometimes it is a good idea to automate the generation of stimulus signals. The example Comb_circuit.pdsprj in Fig. 6.1 shows you how to use the internal scripting language Easy HDL for implementing digital generators, in this case a bus of three inputs. In the same way that you did it in the VHDL testbench fixture as a PROCESS, firstly draw in paper your stimulus signals and your job will be to translate it to this specific language adapting an example. Pay attention to the different parameters, wire label, scrip name, pins, loop variables, etc. You can also use the logic analyser instrument to observe the truth table in time or the signal that you have just generated. This is another example with "Comb_circuit_three_inputs.pdsprj". This is another circuit with two scripts: "Comb_circuit_two_scripts.pdsprj".

|

| Fig. 6.1. Digital generator implemented using the Easy HDL scripting language and signal visualisation in the logic analyser. |

Important NOTE: when printing for written reports, never use black background, use write background to save printer ink as shown below:

|

| Fig. 6.2. Waveforms from the logic analyser with white background and annotations for your reports and presentation |

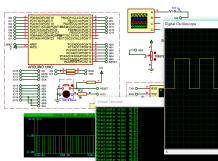

7. Proteus VSM for Arduino AVR

(Optional, beyond CSD scope) We also have acquired the academic licence to capture and run the basic functionality of the Arduino board in the Proteus VSM simulator. This is an "Example_Arduino.pdsprj" sample project including the simulation of the Arduino program code. It generates a programmable PWM waveform. We have other Arduino circuits simulated in Proteus in this DEE extension.

|

Fig. 7.1. Example of a circuit based on Arduino running in Proteus. This feature opens a new set of interesting opportunities for comparing technologies. |