Chapter 1 problems |

- D1.2 - |

9's complementer for BCD arithmetic operations |

1. Specifications

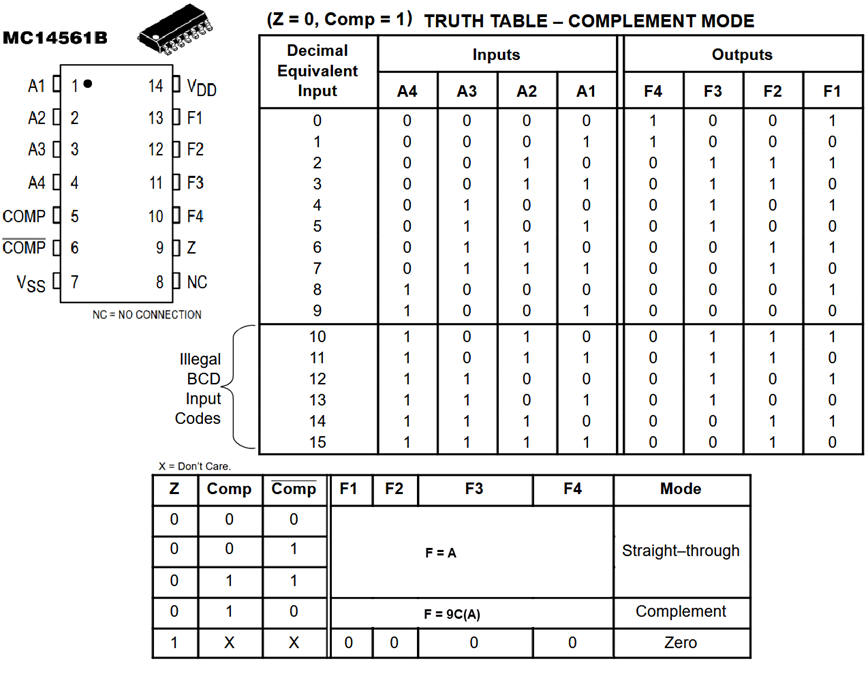

Design a 9's complementer circuit (9C) type MC14561. The idea is like the 2's complement (2C) for integer numbers studied in P4. We can add and subtract BCD numbers using only BCD adders and 9C modules. The chip and its truth table is shown in Fig. 1. This chip is a companion to the classic MC14560B BCD adder to allow BCD subtraction. A complete 3-digit BCD adder-subtractor is proposed in D1.17. adapting schematics proposed in these datasheets.

The same project B3.2 is proposed in Chapter 3 for learning the basics of μC software organisation and basic digital I/O.

|

Fig.1. MC14561 classic chip truth table. |

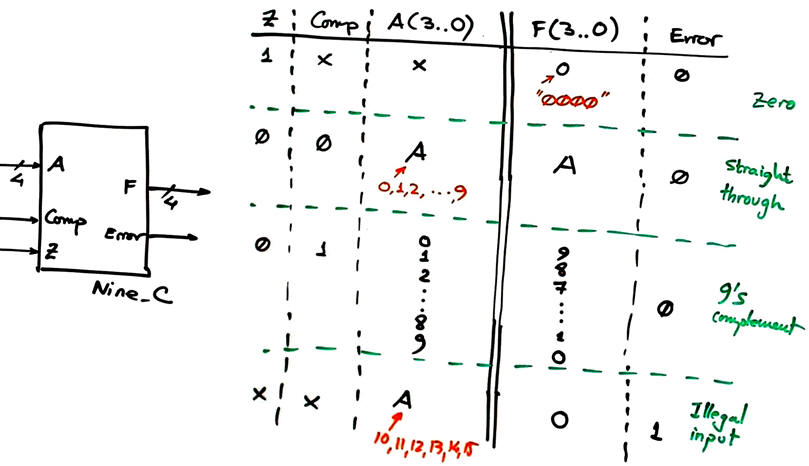

We will modify the circuit's truth table eliminating Comp_L input and adding another output Error to indicate error condition when the input codes are illegal. Draw the full truth table renaming the signals as shown in Fig. 2. When Z = 1 , output is zeroed; when Comp = '1', the output is the 9's complement of the input; when Comp = '0' the output F(3..0) is the same input A(3..0); and when A(3..0) is one of the illegal codes, combinations not existing as BCD numbers, output is zeroed and Error = '1'.

|

Fig.2. Our Nine_C circuit symbol and truth table. |

Draw an example of timing diagram to be used later as stimulus in the VHDL testbench when verifying the synthesised circuit. Consider Min_Pulse = 3.74 ms.

Example of test options for checking the project, try at least these Z, Comp and A values (add other vector values if you need it to clarify how the truth table works):

Option #1: Z = '1', Comp = '0', A = "0101"; Z = '0', Comp = '0', A = "0101"; Z = '0', Comp = '1', A = "0101"; Z = '0', Comp = '1', A = "1101"; Z = '0', Comp = '1', A = "0111"; etc.

Option #2: Z = '1', Comp = '0', A = "0110"; Z = '0', Comp = '0', A = "0110"; Z = '0', Comp = '1', A = "0110"; Z = '0', Comp = '1', A = "1110"; Z = '0', Comp = '1', A = "1001"; etc.

Option #3: Z = '1', Comp = '0', A = "0011"; Z = '0', Comp = '0', A = "0011"; Z = '0', Comp = '1', A = "0011"; Z = '0', Comp = '1', A = "1101"; Z = '0', Comp = '1', A = "1000"; etc.

CPLD or FPGA target chip options:

option #1.: MAX II

option #2.: MAX 10

option #3.: Cyclone IV

2. Planning

Plan A structural circuit based on logic gates and equations in a single VHDL file. We have many strategies, for instance:

option #1: use Minilog to obtain PoS.

Project location:

C:\CSD\P2\Nine_C_A_PoS\(files)

option #2: use Minilog to obtain SoP.

Project location:

C:\CSD\P2\Nine_C_A_SoP\(files)

Plan B behavioural approach writing the truth table or the high-level description or algorithm in VHDL in a single VHDL file.

Project location:

C:\CSD\P2\Nine_C_B\(files)

Plan C2 is a hierarchical architecture based (multiple VHDL file) on components and signals.

Invent a way, studying in details the circuits truth table, to connect simpler standard circuits and logic gates to generate this Nine_C device. Project location:

C:\CSD\P2\Nine_C_C2\(files)

After having studied P4 tutorials, additional questions can be added to our report. For instance:

-

Perform a gate-level simulation to measure propagation delays in a given signal transition.

-

Deduce the worst-case propagation delay running the timing analyser tool and calculate the circuit's maximum frequency of operation for the target chip used in the design.