|

|

|||||

Chapter 2 problems |

- D2.14 - |

Traffic light controller (version 2) |

|||

|

|

|||||

1. Specifications

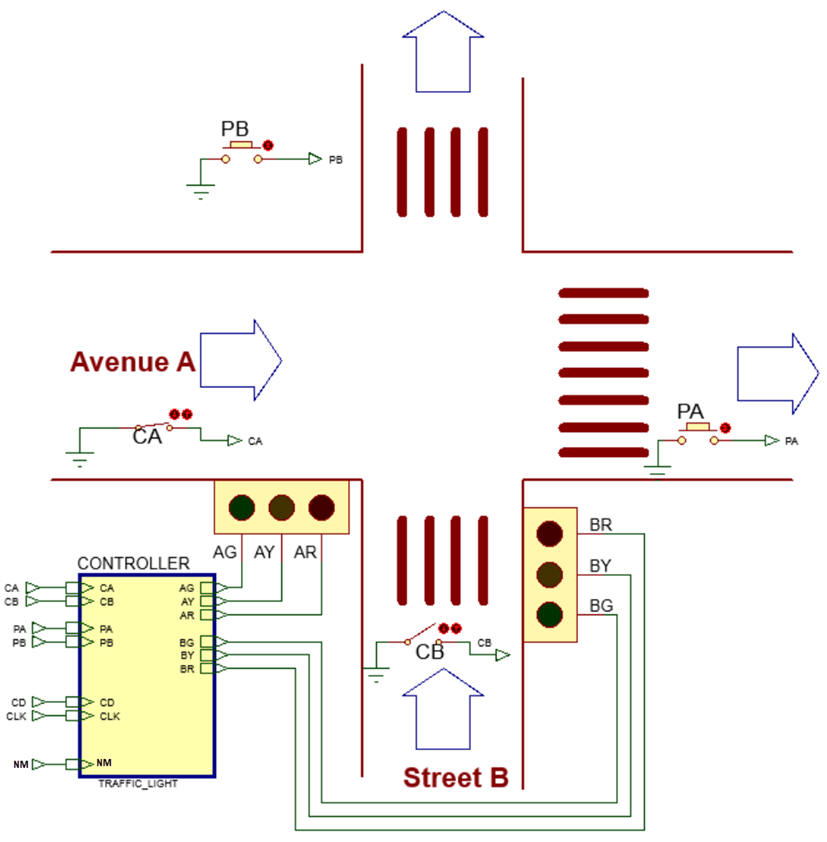

Design a traffic light controller for the given street intersection in Fig. 1. Our aim is to implement a kick off project with some listed features, but not all the ones described in the Traffic light tutorial. And also organise several design phases to make it easy to design and conceive.

|

|

Fig 1. Street intersection to be controlled by our traffic_light system. |

Find information in internet on the green/yellow/red traffic light sequence used currently in Europe. Or simply observe a real traffic light operating and deduce its operative sequence.

Draw an example of timing diagram (for example considering only the control signal in the design phase #1 bellow)

NOTE: The idea is to read and study as much as you like materials, books, examples or advanced tutorials like the one linked above, but do not copy from them. Your aim is to imagine that this project is derived from the LAB6 tutorial where we organised a FSM controlled clicking a single button. The better you comprehend the laboratory tutorial the faster will you design this application.

2. Planning ideas and options

The planning is based on applying our FSM recipe. This architecture is translated to VHDL as a plan C1 single file where the three main components are processes.

Imagine several design phases to conceive and complete the full project. For instance:

Design phase #1: implement the basic traffic light sequence including only the button NM (night mode). This signal may come from a light sensor or an auxiliary clock. When NM = 0, day time, the normal traffic light sequence is generated. When NM = 1, night, both light poles are displaying intermitent yellow lights and thus the vertical pole signs are in use on the street intersection.

Logically, in a commercial traffic light controller, the time duration of each colour pattern in avenue A and street B is programmed or configured by technicians or the authorities in charge of road networks. Here, specially in this first design phase we simply will consider that there is a new colour pattern every CLK period.

Project location:

C:

Therefore, only when this phase #1 is complete and functionally working (1-2-3-4).

Design phase #2: Add car sensors CA and CB to stop the normal traffic light sequence operation when cars are not detected in a given street. The idea is that if no cars are detected in street B, there is no need to stop the cars in avenue A, they can circulate always in green.

Project location:

C:

And here, you can add the section 5 on calculating delays and maximum frequency of operation.

Propose a state diagram.

|

| Fig. 2. Traffic light controller state diagram for design phase #1. |

Adapt the FSM architecture to this problem, naming and connecting all signals and inputs and outputs.

Deduce how many D_FF are required when encoding FSM states using the following options and draw the state register memory:

Option #1: radix-2 (sequential)

Option #2: Gray

Option #3: Johnson

Option #4: one-hot

Draw the state register memory block.

Write the truth table of CC2 and CC1 and their equivalent behavioural interpretations (plan B) using flowcharts.

Write the FSM VHDL file.

Start a Quartus Prime synthesis project for one of the following programmable target chips:

Option #1: Cyclone IV EP4CE115F29C7

Option #1: MAX II EPM2210F324C3

Inspect and annotate the RTL and technology views. Check the number of D_FF synthesised in this application.

Generate a VHDL testbench fixture schematic. Translate the timing diagram sketch from the specifications into de corresponding stimulus processes.

Run functional simulations to verify your design. Visualise as well in the wave timing diagram the internal states.

Run gate-level simulations to measure the propagation time CLK to output (tCO). Measure the minimum TCLK period or the maximum frequency of operation of the FSM.

Optional: Add PA and PB push-buttons to allow pedestrians to cross the intersection at any time when the traffic light sequence is locked in a given street because there are no cars in the other.

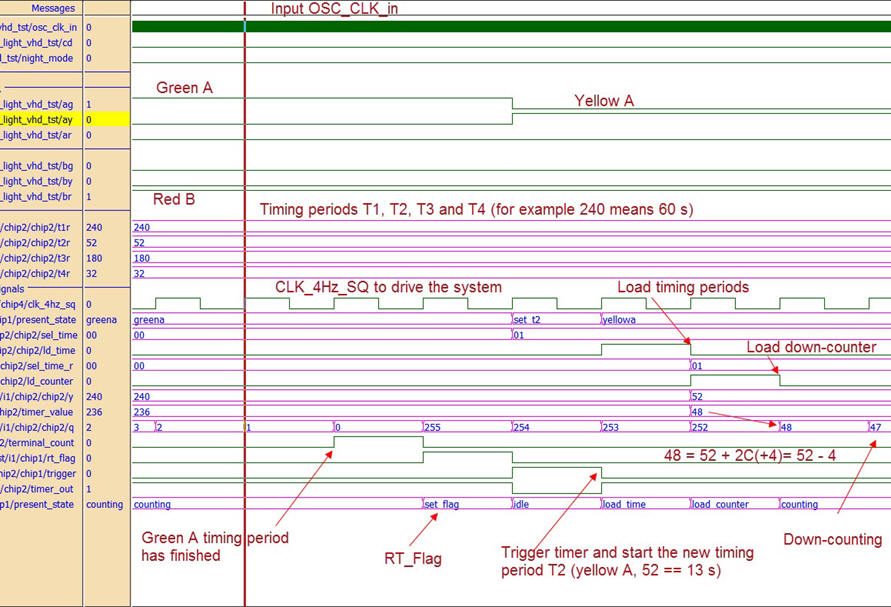

Optional: Add a programmable timer to adjust green/yellow/red light times in street B and avenue A. Thus conventing this circuit into a dedicated processor as the example projects in P8. Fig. 3 shows an example of internal architecture.

|

|

Fig 3. The complete traffic light controller building blocks (Visio). |

Solve the CLK generator. Generate 4 Hz squared CLK signal from the crystal quartz oscillator available on the training board. For instance, 25.175 MHz in the Altera's UP2 (example of architecture) or 50 MHz in the Digilent NESYS 2 or MAX10-Lite boards. Generate the 2 Hz square signal to drive the yellow LED at night mode.

Using this Programmable_timer generate the signals required by the traffic light. For instance: Green A = 63 s, Yellow A = 13 s, Green B = 45 s, Yellow B = 8 s. Reorganise your state diagram so that you can command the programmable time as well as external lamps.

|

Fig. 4. Example of traffic light waveforms. Results from the VHDL EDA simulator zooming the transition from Green_A to Yellow_A in order to demonstrate how the FSM changes states synchronously while generating both internal signals and external outputs. |

Optional: Other additional features:

Add a transmission system able to report the current state of the traffic light controller to a remote computer and to accept orders from a central system (full duplex communication).

Add a car speed measurement system with speed limit indicators and numeric displays signs.