|

|

|||||

Chapter 1 problems |

- D1.9 - |

16-bit comparator for integer numbers |

|||

|

|

|||||

1. Specifications

Build the comparator Int_Comp_16bit represented in Fig. 1 for 16-bit two's complemented (2C) integers.

The same project B3.9 is proposed in Chapter 3 for learning the basics of μC software organisation and basic digital I/O.

|

| Fig. 1. Symbol. |

Specifications include: symbol, truth table, data range, example timing diagram and comparison operations, example commercial chip, etc.

Int_Comp_16bit target chip is one of the following:

- MAX II EPM2210F324C3.

- Cyclone IV EP4CE115F29C7

- Calculate the propagation delay in a given signal transition using gate-level simulations.

- Calculate the circuit's longest propagation delay and maximum speed for a given target chip.

2. Planning

Invent the plan C2 schematic for this Int_Comp_16bit after having studied the example Int_Comp_8bit.

Comp_4bit component is designed using a chain of expandable Comp_1bit.

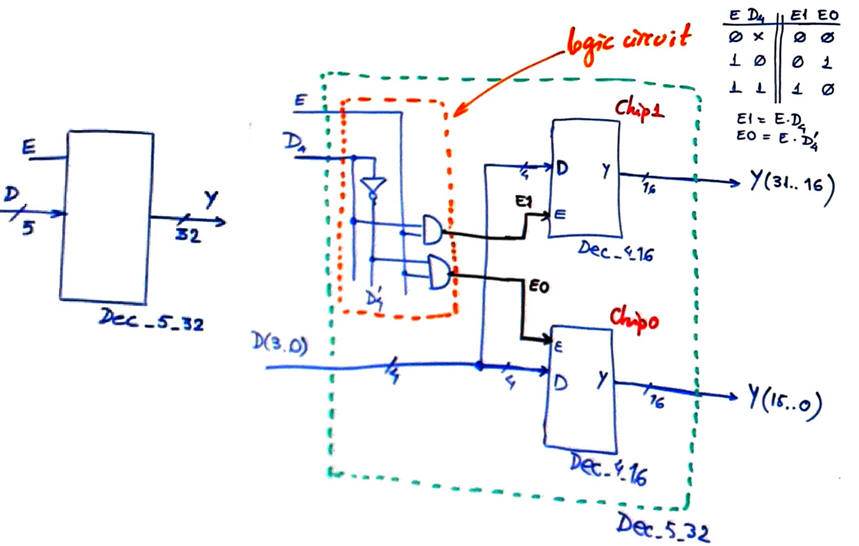

Invent the Comp_1bit using plan C2 based on the method of decoders (MoD). In P3 tutorials we find the Comp_1bit truth table and in P2, the Dec_4_16.vhd component can be used to implement the Dec_5_32 required in this application.

|

| Fig. 2. Designing Dec_5_32 expanding Dec_4_16. |