|

|

|||||

Chapter 2 problems |

- A2.5 - |

Analysis of a synchronous circuit (Circuit_F) |

|||

|

|

|||||

1. Specifications

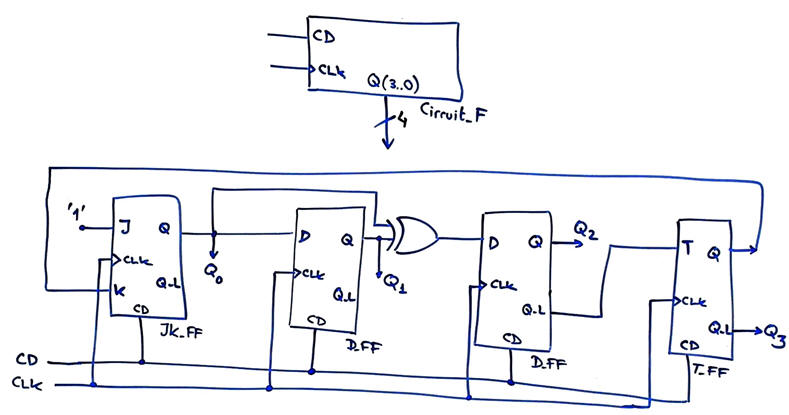

The circuit represented in Fig. 1 is composed of several flip-flops and gates. Synchronous structures are much simple to analyse than asynchronous circuits because all flip-flops are driven by the same CLK signal.

Determine how does the Circuit_F work, finding the output vector Q(3..0) using our three analysis methods.

Discuss how many states the system is capable of memorising.

Discuss what may be the function or application of the circuit, if any.

Measure propagation delay CLK to output (tCO) and deduce the maximum CLK frequency fMAX that can be applyed to the circuit.

As we proposed in P1 analysing combinational circuits, self-assess the validity of your solution comparing results obtained from different methods.

|

|

Fig 1. Circuit_F symbol and internal structure. |

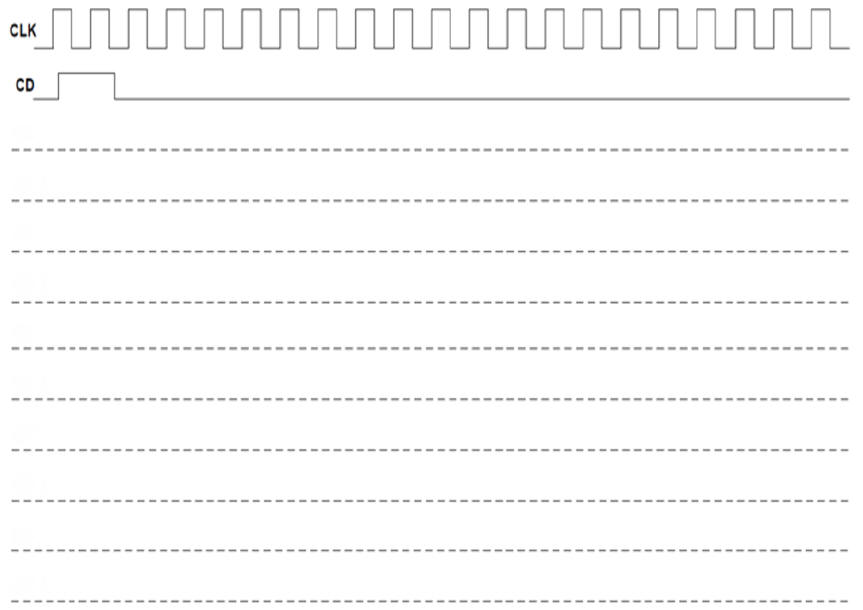

A convenient waveform template is shown in Fig 2.

|

|

Fig 4. Waveforms tempalte. |

2. Planning

Method I. Handwritten analysis to draw the circuit's timing diagram and determining the outputs. In LAB5 session we fixed a procedure consisting of several steps.

Use this project location to save your paper solution, class notes, pictures, theory, etc.:

C:\CSD\P5\Circuit_F\paper\(files)

Method II. Proteus capture and electrical simulation. Apply the planned stepped procedure in LAB5 capturing and analysing your circuits to get experience using Proteus. Find circuits to copy and adapt using the corresponding library of components.

Proteus components library options:

option #1: LS-TTL

option #2: CMOS

Project location:

C:\CSD\P5\Circuit_F\proteus\(files)

Method III. VHDL synthesis and simulation. Apply the planned stepped procedure in LAB5 to use correctly our VHDL EDA tools and find the flip-flop components in our tutorials (D_FF, JK_FF, T_FF).

CPLD or FPGA target chip options:

option #1: MAX II

option #2: Cyclone IV

Synthesise the project and print the RTL view. Be aware that the "number of registers" in the project's summary spreadsheet must be correct.

Use a VHDL test bench to demonstrate that the timing diagram looks like that obtained in the previous analysis methods.

How can you observe and measure glitches, false states and complications around CLK transitions?

Project location:

C:\CSD\P5\Circuit_F\VHDL\(files)

Optional. Exercise related to the next P6 content: How to implement the same application using a standard synchronous circuit? Design an FSM to generate synchronously the same output Q(3..0).