|

|

||

|

|

Dual_MUX_4 plan C2: hierarchical multiple-file VHDL |

|

|

|

||

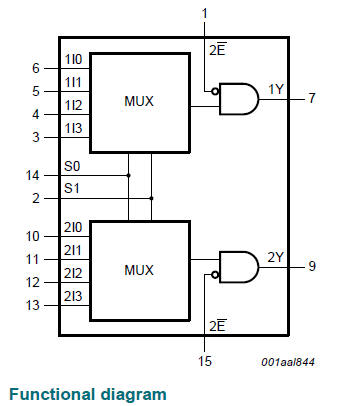

Type 74HCT153

| 1. Specifications | Planning | Developing | Functional test | Gate-level test | Prototype | Report |

Design a classic chip like the 74HCT153 using behavioral approach (plan C2).

a) a) |

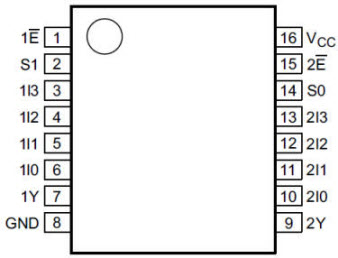

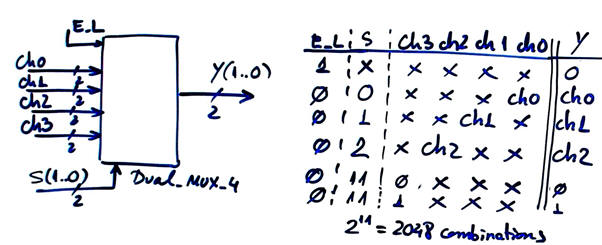

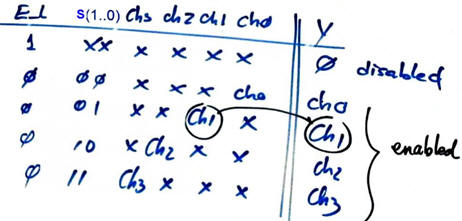

Fig. 1. a) Case and pin naming and enumeration of a classic 74HCT153 chip. We will interpret it as shown in b). Vector data select S(1..0) may be represented in binary radix-2 or as an unsigned decimal. Symbol name is Dual_MUX_4 meaning that data input channels and output are dual, they have two-bit size Ch0 --> Ch0(1..0). In other applications we may have other expanded devices like Octuple_MUX_8, meaning that Channel size is 8-bit for instance Ch0(7..0), and select channel is S(2..0) to be able to switch 8 data channels . Enable is active-low (E_L) meaning that the chip operates when E_L = '0'. |

b)  - How many maxterms does Y(1) have? - How many minterms does Y(0) have? |

|

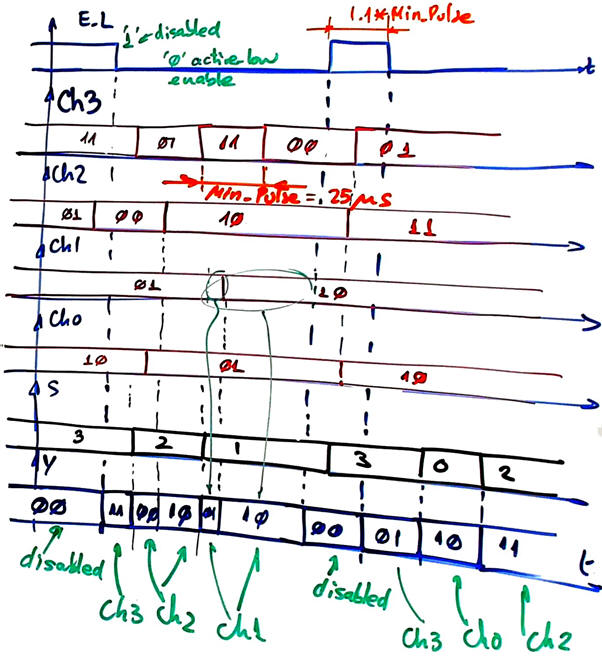

Draw the sketch of a timing diagram to demonstrate how the circuit works for several input stimulus.

|

| Fig. 2. Example timing diagram. |

| Specifications | 2. Planning | Developing | Functional test | Gate-level test | Prototype | Report |

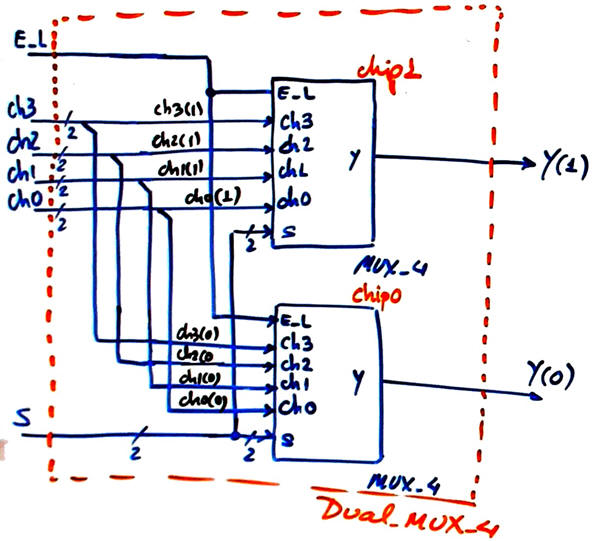

The idea now is the interpretation of the circuit imagining that it can be inferred chaining smaller chips of the same kind. For instance a pair of MUX_4, as the datasheet from Nexperia suggests. Out Dual_MUX_4 is basically two MUX_4 working in parallel because they share the same select channel inputs.

Component MUX_4 is already available in our Digsys library from another project (for instance MUX_8 based on plan C2). We simply need to use two of them as Chip0 and Chip1 in our top entity Dual_MUX_4, as represented in Fig. 3.

|

| Fig. 3. Plan C2 suggested by Nexperia datasheet and our proposed plan schematic. |

Project and file locations:

C:/CSD/P3/Dual_MUX_4_C2/(files)

| Specifications | Planning | 3. Developing | Functional test | Gate-level test | Prototype | Report |

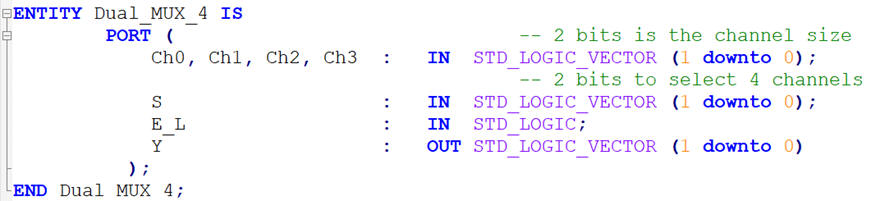

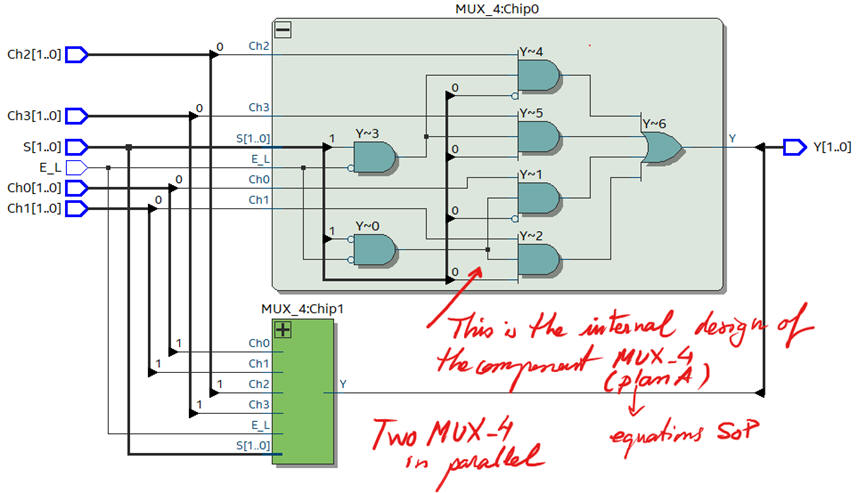

VHDL translations of Fig 3: top entity Dual_MUX_4.vhd and component MUX_4.vhd (for instance using plan A based on simplified SoP equations).

This is the description of the entity accordingly to the CSD input and output naming.

|

| Fig. 4. Entity definition that is the same whatever the plan. |

Start an EDA synthesis project named Dual_MUX_4_prj for a given CPLD or FPGA target chip and examine results.

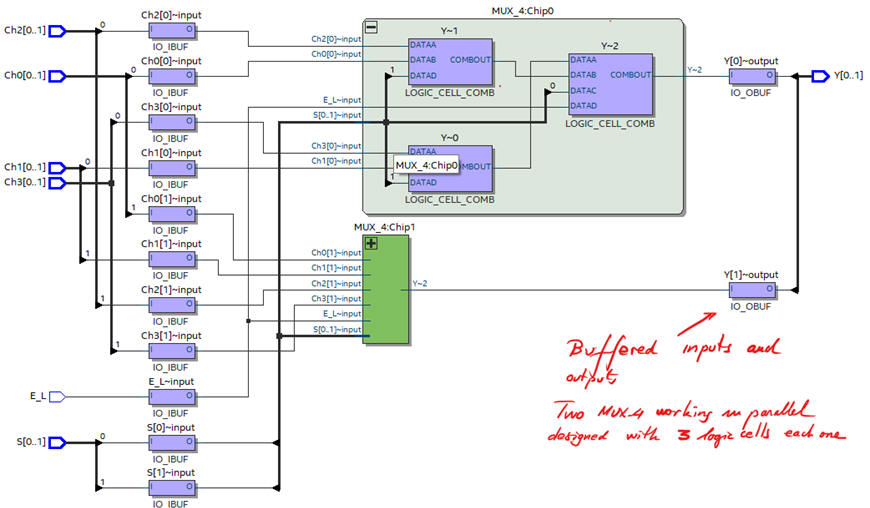

Schematics RTL:

|

| Fig. 5. RTL schematic. |

In the end, the same final circuit (technology view) will be placed and routed into the PLD accordingly to its technology (sPLD, CPLD or FPGA) and manufacturer (Lattice, Intel, Xilinx, etc.).

|

| Fig. 6. Technology view for a Cyclone IV FPGA. |

| Specifications | Planning | Developing | 4. Functional test | Gate-level test | Prototype | Report |

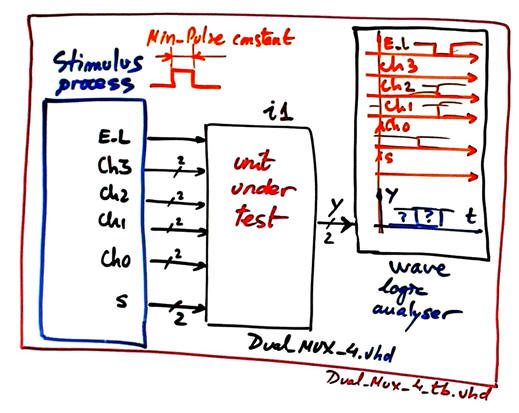

In Fig. 7 is represented the testbench schematic to stimulate the unit under test (UUT) with input vectors. Generate the skeleton of the testbench file and add stimulus translating to VHDL input activity from the time diagram in Fig. 2. This is an example of a simple test bench Dual_MUX_4_tb.vhd where the inputs have been stimulated with logic values.

|

Fig. 7. Testbench fixture to verify that our circuit works as expected. |

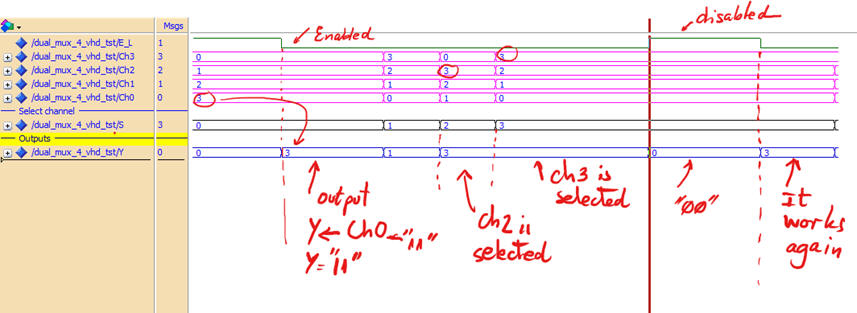

Start the VHDL simulator project, Dual_MUX_4_functional_sim, and run the test. Verify applying sufficient test vector that the device works as expected (verify how the information of each channel is selected). Print timing diagram screen and add comments on the signals to show how the device works.

|

| Fig. 8. Waveform results from the logic analyser. |

| Specifications | Planning | Developing | Functional test | 5. Gate-level test | Prototype | Report |

| Specifications | Planning | Developing | Functional test | Gate-level test | 6. Prototype | Report |

An example prototype for this circuit is presented here.

| Specifications | Planning | Developing | Functional test | Gate-level test | Prototype | 7. Report |

Follow this rubric for writing reports.