|

|

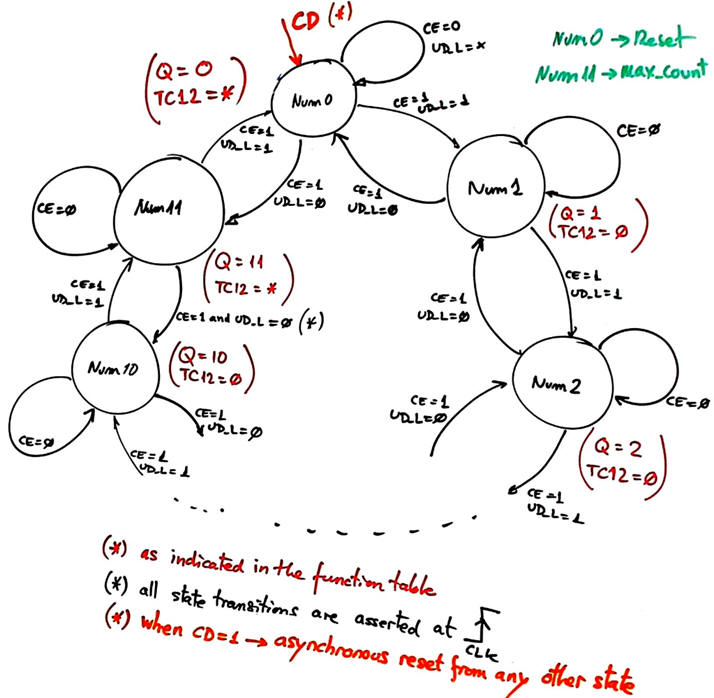

Radix-2 synchronous counter modulo 12 using plan Y |

FSM application using the VHDL arithmetic library

| 1. Specifications | Planning | Developing | Test functional | Test gate-level | Prototype | Report |

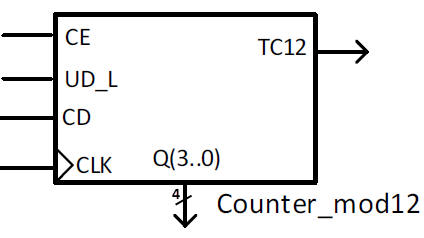

Design the synchronous counter modulo 12 (Counter_mod12) represented in Fig. 1 using plan Y.

|

|

| Fig 1. Symbol and function table. |

|

|

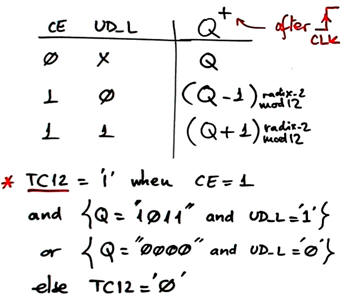

Fig 2. Example of timing diagram. |

|

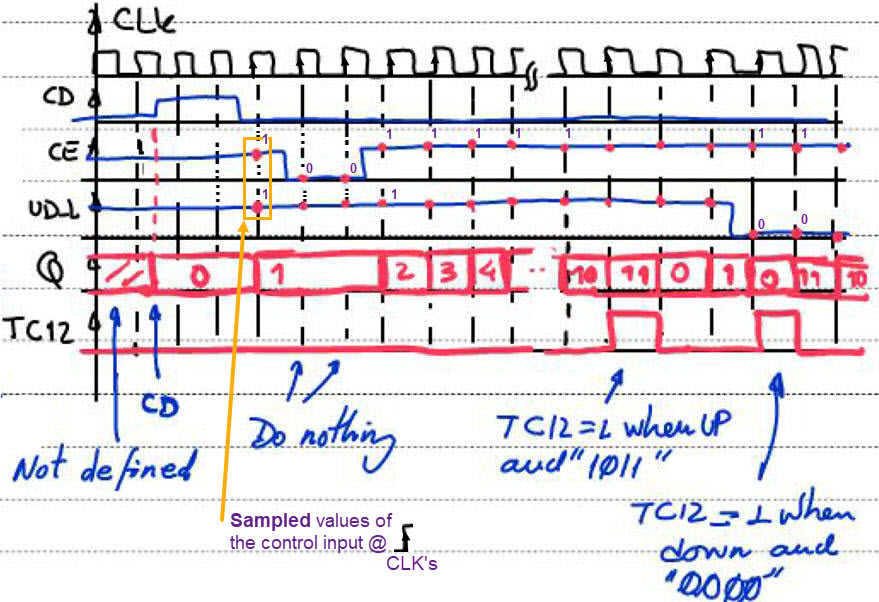

Fig. 3. State diagram representing the 36 state transitions and outputs. |

| Specifications | 2. Planning | Developing | Test functional | Test gate-level | Prototype | Report |

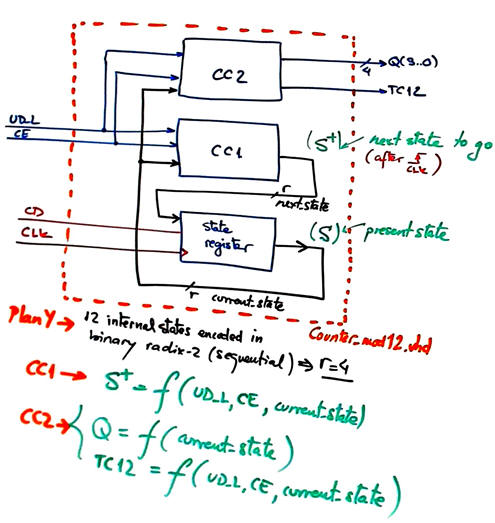

Let us plan this circuit as a FSM. The idea now is to use sequential (radix-2) encoding because the internal states will be simply buffered to the outputs.

|

Fig. 4. FSM architecture. |

|

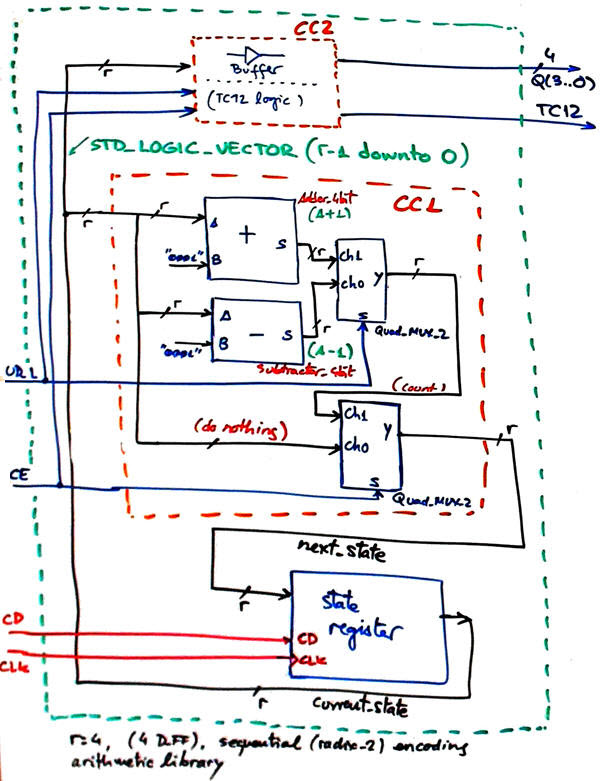

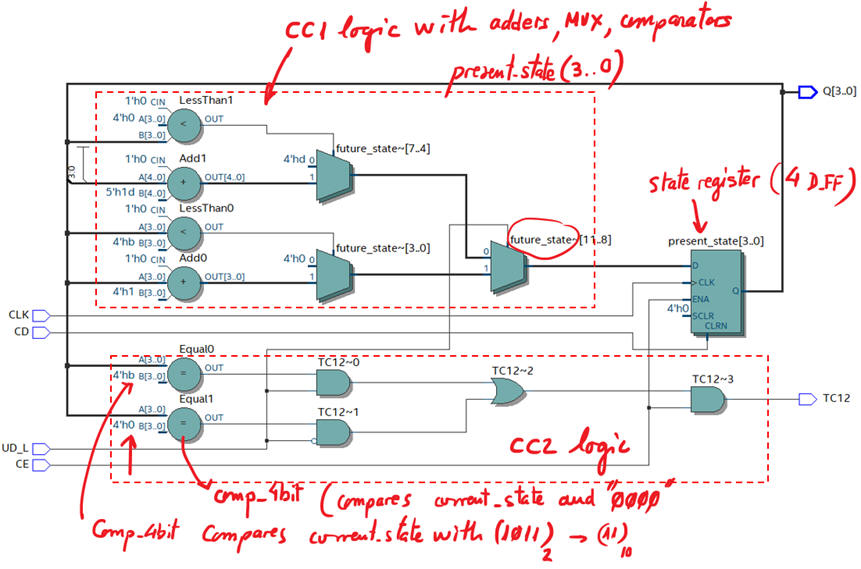

Fig. 5. FSM circuit to implement the Counter_mod12 using plan Y detailing the main ideas on CC2 and CC1 architectures. CC2 generates Q(3..0) buffering the internal state encoded in binary sequential (radix-2). It also implements the additional logic related to TC12. CC1 uses arithmetic blocks such as adders, subtractors and comparators to calculate the next state to go. Multiplexers are used to select between the several modes of operation. This circuit is easily scalable in VHDL because the internal states are configured as: STD_LOGIC_VECTOR(r-1 downto 0). |

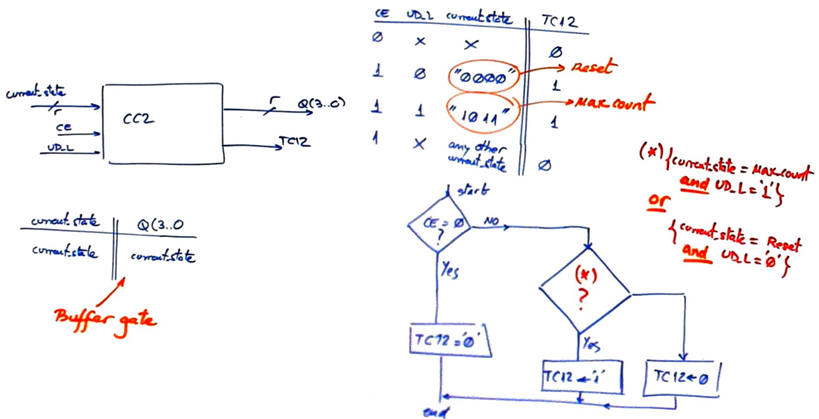

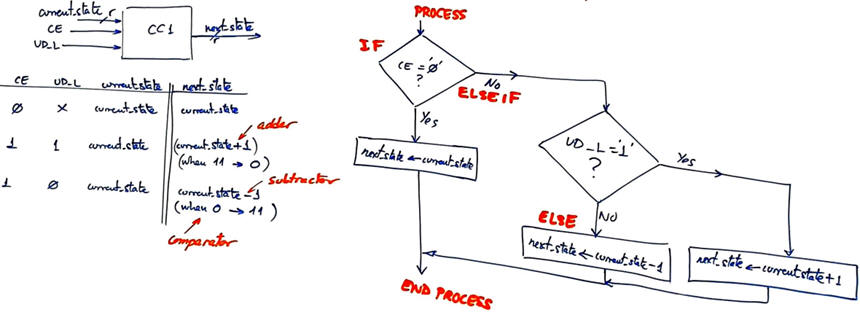

Discussion for obtaining CC2 and CC1 truth tables and their equivalent flowcharts.

|

Fig. 6. CC2 truth table and flowchart. |

|

Fig. 7. CC1 truth table and flowchart where the equivalent translation to VHDL is inferred. |

Project location:

C:\CSD\P7\Counter_mod12Y\(files:Counter_mod12.vhd, etc. )

| Specifications | Planning | 3. Developing | Test functional | Test gate-level | Prototype | Report |

This is the Counter_mod12.vhd file that translates flowcharts in Fig. 6 and Fig. 7.

|

Fig. 8. RTL view with indications of the main components. This is how the synthesis tool interprets our ideas sketched in Fig. 5. |

|

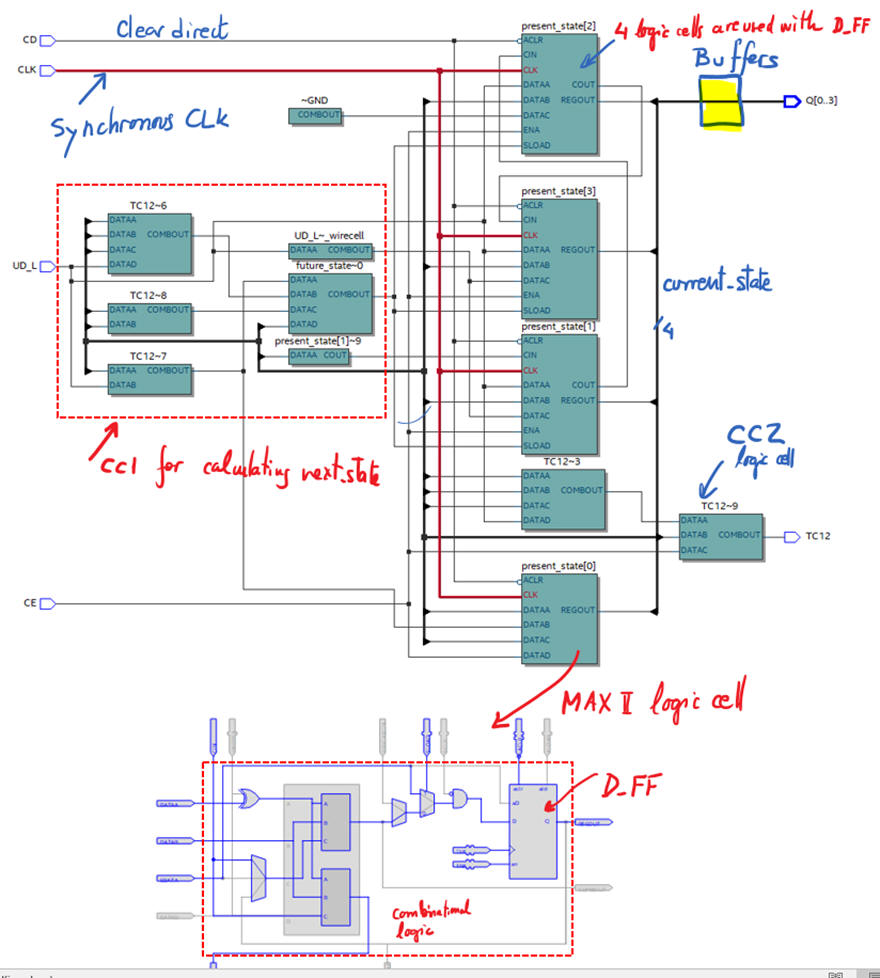

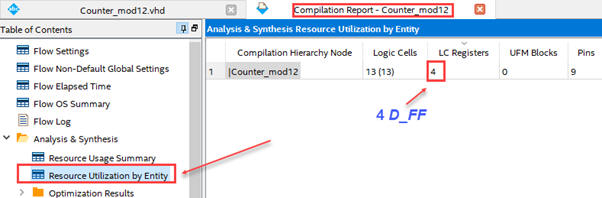

Fig. 9. Technology view schematic for a MAX II Intel CPLD and resources used (13 logic cells and 4 D_FF). |

| Specifications | Planning | Developing | 4. Test functional | Test gate-level | Prototype | Report |

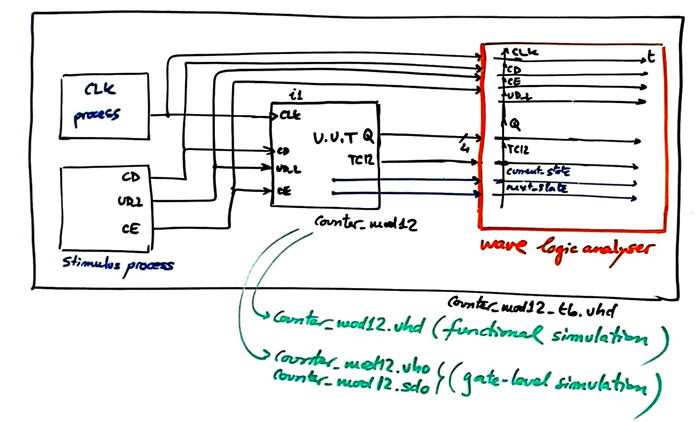

Start the testbench template and add the CLK and inputs activity translating the timing diagram. Make all the timing relative to the CLK_Period constant.

|

Fig. 10. Testbench schematic fixture. |

This is an example VHDL file translation from which you can copy the CLK_Period constant, and also the stimulus and CLK processes Counter_mod12_tb.vhd.

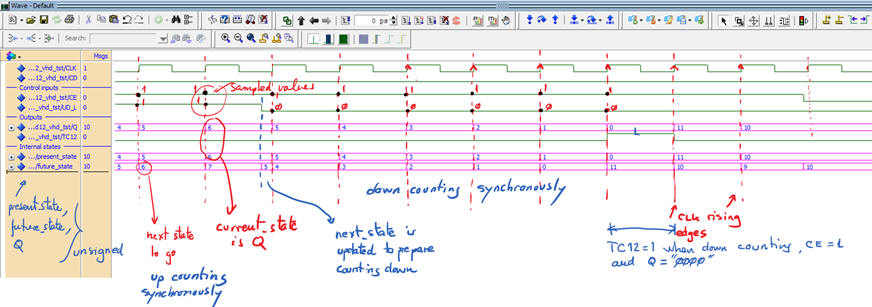

Functional simulation. Run the EDA VHDL tool and demonstrate how the circuit works adding comments to the printed sheet of paper containing the waveforms. Your system may works like the timing diagram discussed in class.

|

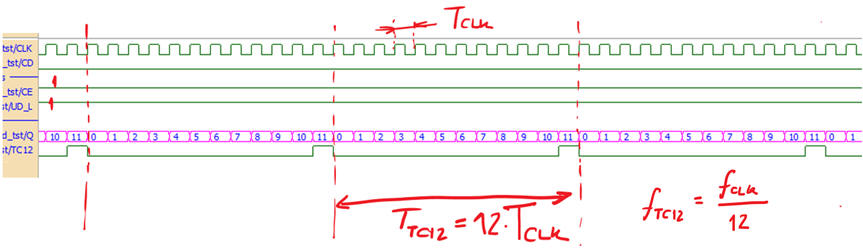

| Fig 11. Example of functional simulation of Counter_mod12. When running continuously (CE = '1'), TC12 is a periodic pulsed waveform that has a frequency fTC12 = fCLK/12 (frequency divider by 12). |

| Specifications | Planning | Developing | Test functional | 5. Test gate-level | Prototype | Report |

Gate-level simulations in ModelSim

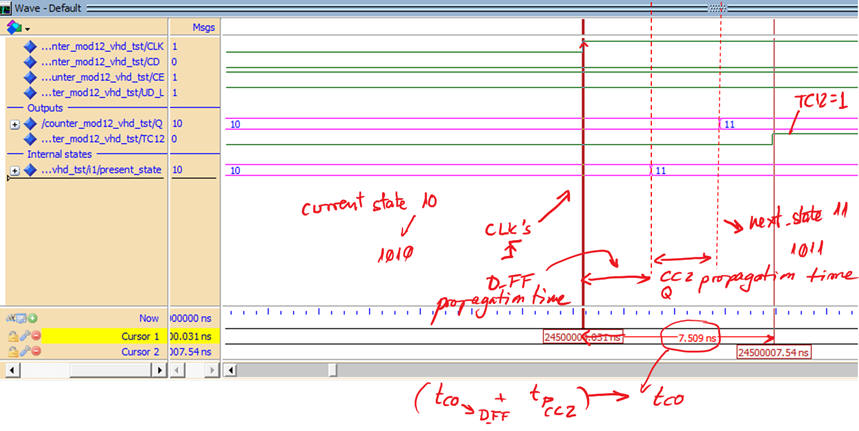

Run the gate-level simulation of the project and measure the maximum frequency of operation. It is worth to know exactly which is the maxim CLK frequency for a given target CPLD or FPGA chip.

|

| Fig 10. Example of a gate-level simulation of the counter modulo 12 used to measure the parameter tCO in a given CLK transition. Target chip Intel MAX II. |

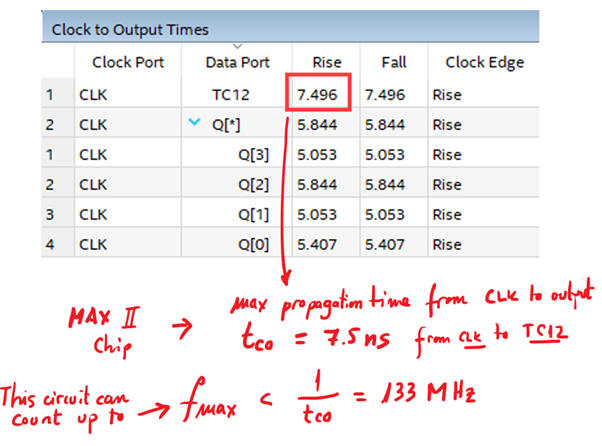

Quartus Prime timing analyser

Timing analyser spreadsheet to measure tCO. The extra logic for calculating TC12 represents a longer propagation time than for calculating Q(3..0).

|

Fig. 11. Timing analyser spreadsheet for measuring tCO. |

| Specifications | Planning | Developing | Test functional | Test gate-level | 6. Prototype | Report |

Practice with the example proposed in this version of the counter.

| Specifications | Planning | Developing | Test functional | Test gate-level | Prototype | 7. Report |

Follow this rubric for writing reports.