|

Strategies for designing combinational circuits using VHDL |

||

Concepts related to our circuit consist of: symbol, truth table, timing diagram applying some values, and a bit of theory or context if what is object of design is a standard circuit or a practical application. Therefore, comprehend the circuit specifications before attempting a plan.

|

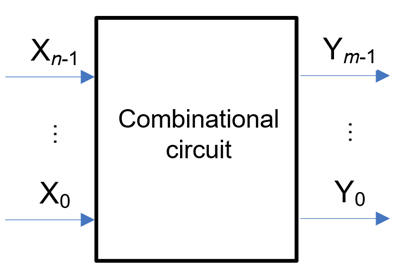

Fig. 1. Symbol (entity) of a generalised combinational circuit. In CSD we propose up to fourteen architectures for inventing logic functions using VHDL tools and methodologies. |

Plan A: structural, equation-based, flat design (a single VHDL file)

General ideas on designing combinational circuits using networks of logic gates covered in P1.

1) Canonical equations: sum of minterms. The truth table equation.

2) Canonical equations: product of maxterms. The truth table equation.

3) Simplified equations: SoP. For example, the output from minilog.exe. This method is used in sPLD-CPLD macrocells.

4) Simplified equations: PoS. For example, the output from minilog.exe.

5) Any equation using only-NOR gates.

6) Any equation using only-NAND gates.

7) Mixing equations of any kind.

Plan B: behavioural, direct truth table /algorithm translation to VHDL (flat design)

Covered from P2 where we start classifying standard logic circuits.

8) Translating the truth table directly to VHDL or to an algorithm represented by a flowchart.

Covered in P9 as an easy way to introduce microcontroller programming in C and basic I/O.

9) Translating the truth table directly to C language as software to be executed in a microcontroller.

Plan C1: hierarchical structure of components (flat design, single-file)

10) Not practical, and not used in CSD Chapter 1. Indeed, we use it only for describing FSM architecture in Chapter 2.

Plan C2: hierarchical structure of components, multiple-file design

Covered in P3) where large and chained circuits are explained:

11) The method of decoders (MoD)

12) The method of multiplexers (MoM)

13) Circuit expansion. Most of circuits that deal with n-size vectors can be organised using identical chips or similar ones chained by means of a given pattern (i.e. carry in, carry out; enable in , enable out) using special inputs and outputs. For instance, we can invent an Enc_4_10 using Enc_2_4.

Covered in L5.4 were memory components are introduced:

14) The method of ROM/RAM memory chips or lookup tables (FPGA - LUT)