Chapter 2 problems |

- A2.1 - |

Analysis of the synchronous Circuit_E |

|

1. Specifications

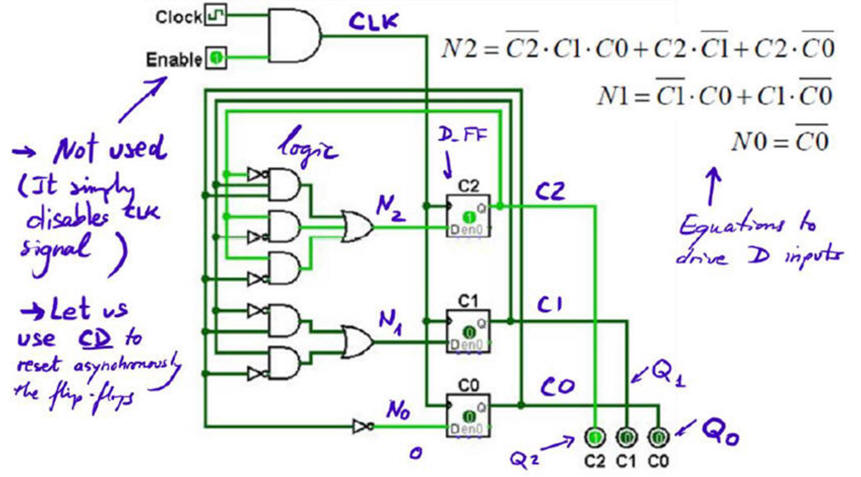

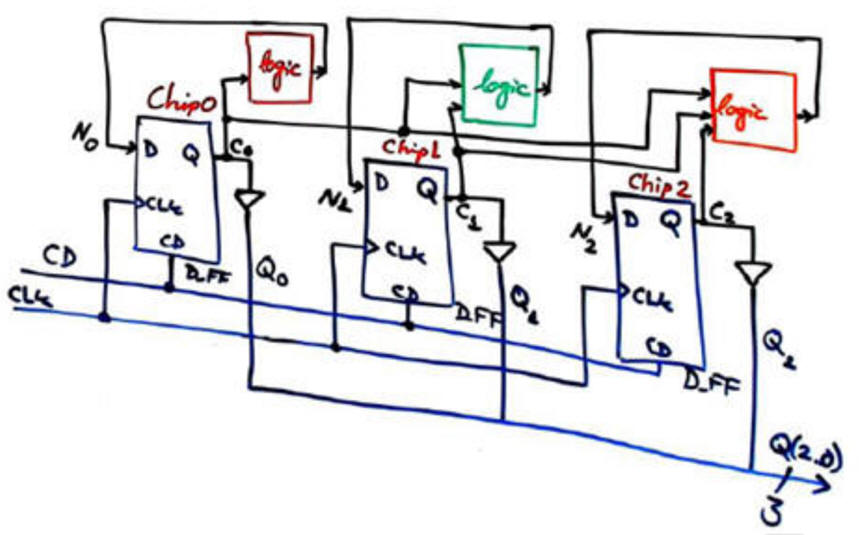

Fig. 1 represents a circuit based on D_FF found browsing Internet. Let us name it Circuit_E. Enable input is not required because it is simply a CLK blocker when '0' freezing the circuit activity (in P7 we will present better methods for inhibiting, disabling or stopping a circuit activity without connecting the special CLK signal). In Fig. 2 we have redrawn and adapted it as usual to our conventions and naming style so that we can use our tools to analyse it.

|

|

Fig. 1. Circuit based on D_FF and logic gates. |

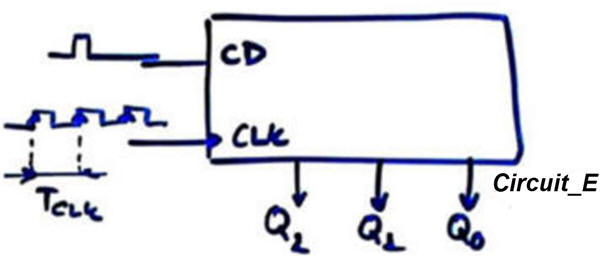

Determine how does the circuit work, meaning finding the output vector Q(2..0) using our three analysis methods. Measure propagation delays CLK to output (tCO) and deduce the maximum CLK frequency fMAX that can be applied to the circuit.

2. Planning

Method I. Handwritten analysis to draw the circuit's timing diagram and determining the outputs.

Two analysis steps: (1) analyse one D_FF, (2) analyse the complete circuit. Here it is necessary to determine the three truth tables for the combinational circuits before applying them on calculating N1, N2 and N0 outputs to be sampled on the CLK's rising edges.

Use this project location to save your paper solution, class notes, pictures, theory, etc.:

C:\CSD\P5\Circuit_E\paper\(files)

Method II. Proteus capture and electrical simulation.

Proteus components library options:

option #1.: LS-TTL

option #2.: CMOS

Project location:

C:\CSD\P5\Circuit_E\proteus\(files)

Method III. VHDL synthesis and simulation.

What is the maximum CLK frequency when picking a target chip MAXII EPM2210F324C3?

|

|

Fig. 2. Circuit_E to be analysed using our three methods. |

CPLD or FPGA target chip options:

option #1.: MAX II

option #3.: Cyclone IV

Project location:

C:\CSD\P5\Circuit_E\VHDL\(files)