|

|

|||

|

|

Tutorial analysis of Circuit_K |

||

|

|

|||

| Method I | Method II | Method III | Method IV |

| 1. Specifications | Planning | Developing | Testing | Report |

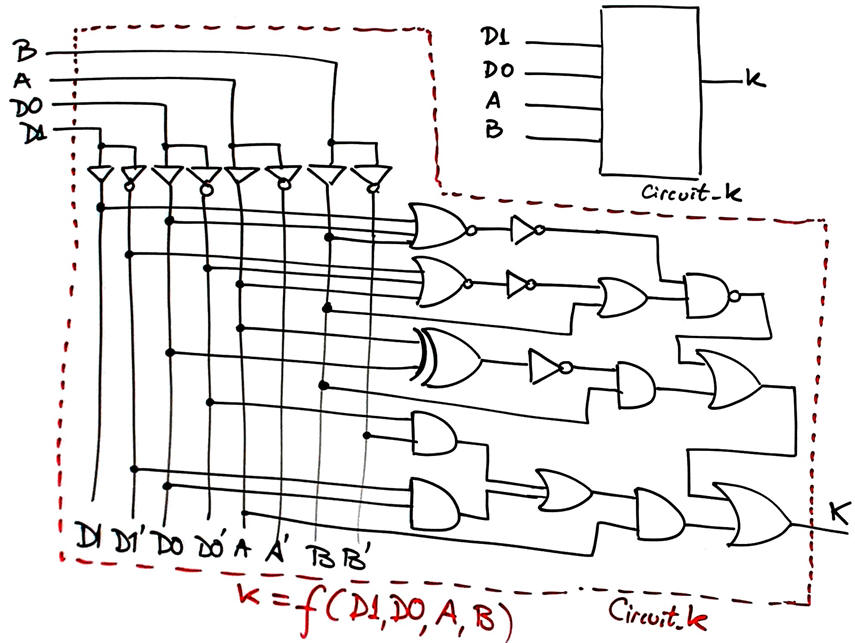

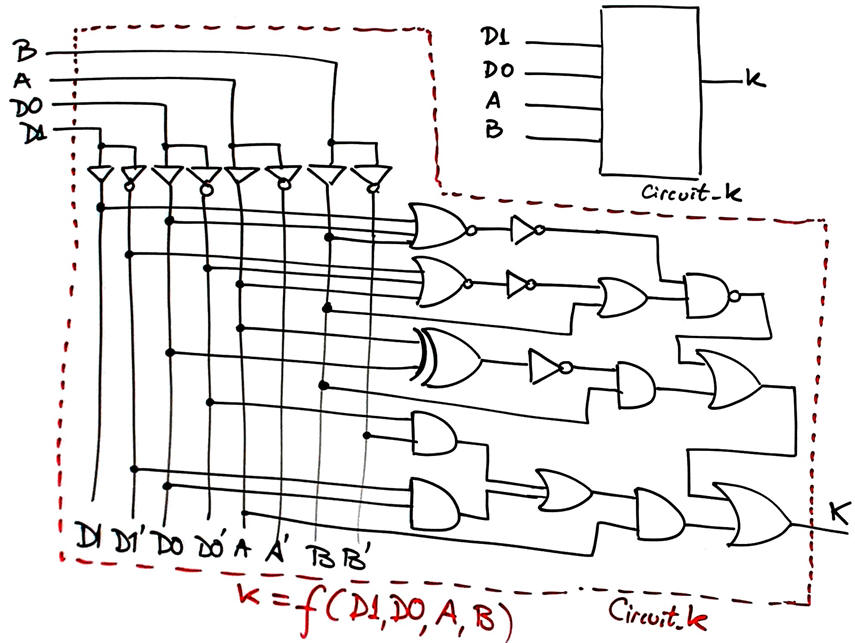

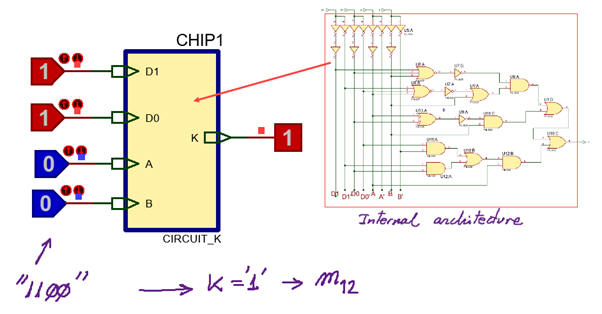

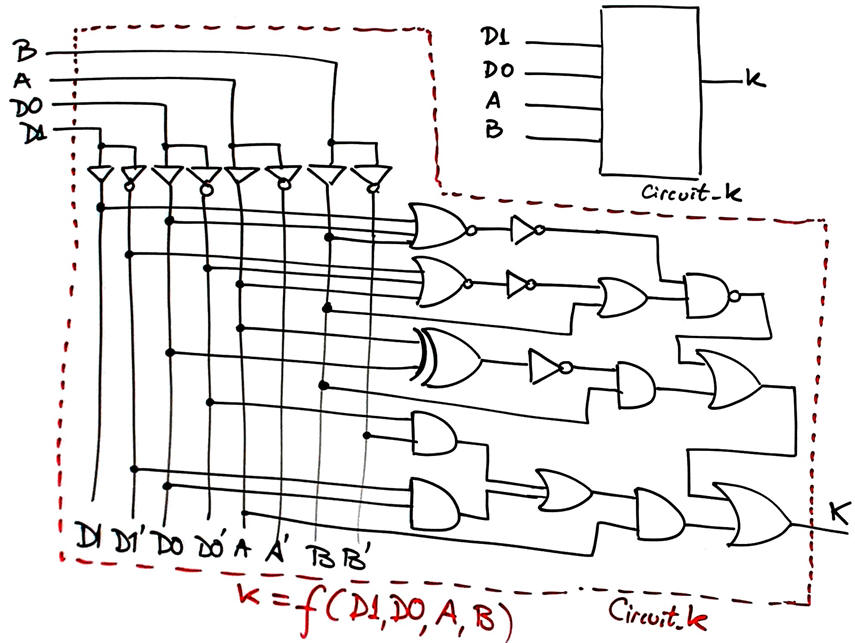

Deduce the truth table of Circuit_K in Fig. 1 using analysis method I and compare and discuss solutions.

|

| Fig. 1. Example Circuit_K to analyse. |

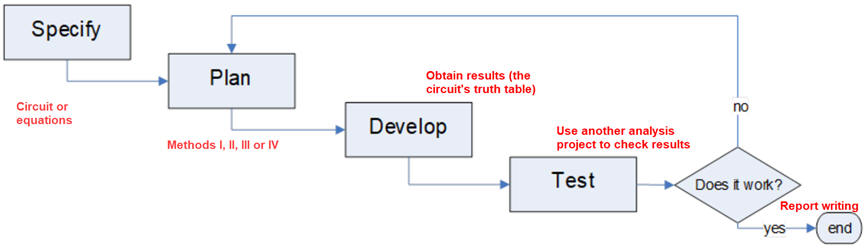

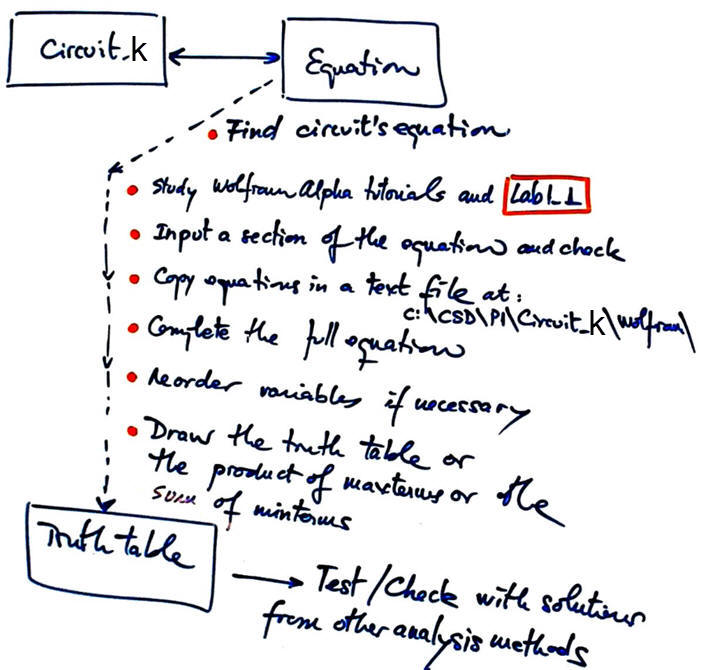

Analysis projects consist of four sections as shown in Fig. 2.

|

| Fig. 2. Organise your analysis project following this sequence.Write your report only when your result is verified using another analysis method. |

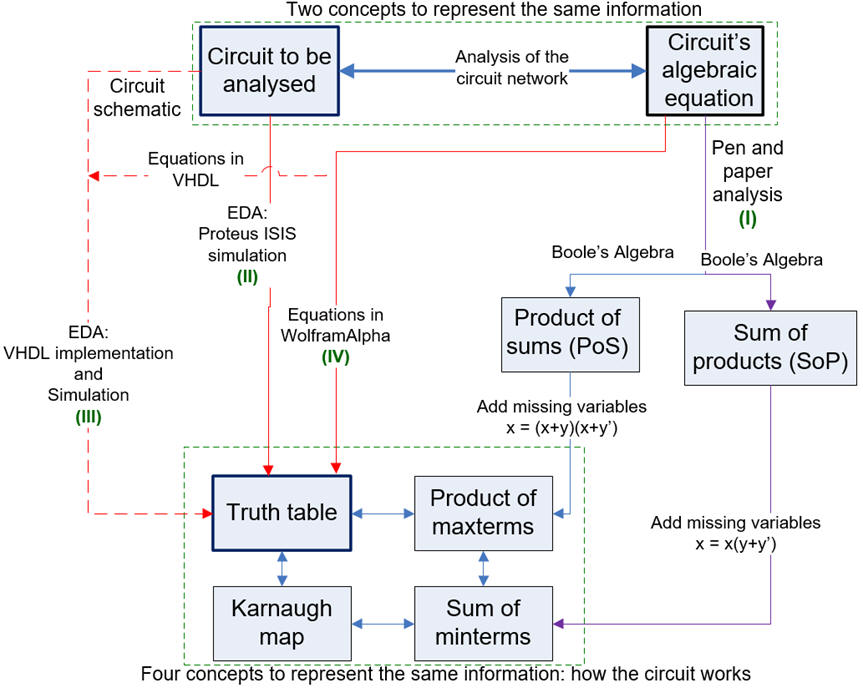

Fig. 3 shows the general concept map including up to four methods for analysing simple combinational circuits.

|

| Fig. 3. Proposed analysis methods (Visio). The concept map combining analysis and design (Visio). |

Note something very important: do not start a project or a simulation from scratch but copying and adapting a similar exercise or file from this web. For instance Circuit_W from lecture L1.3 or from the highlighted project Circuit_C. Our web contains many examples and exercises that can be used as templates to copy and adapt.

| Specifications | 2. Planning | Developing | Testing | Report |

Analytical method using Boolean algebra and pen & paper. If the circuit is too large or you are still learning basic Boole's algebra, it is better to start solving to the end only a section of the circuit.

Place the projects in different folders and name them accordingly. Normally we use our C: hard disk drive, for instance:

C:\CSD\P1\Circuit_K\algebra\Circuit_K.jpg, circuit_K.pdf, etc. (pictures, scanned sheets of paper, ...)

Find the circuit equation.

Simplify equations until SoP or PoS equations are obtained.

In order to fill in the truth table, add missing variables to convert SoP into sum of minterms or PoS into product of maxterms.

| Specifications | Planning | 3. Developing | Testing | Report |

Proceed using Boolean algebra following the plan until you obtain a simplified expression like SoP or PoS.

Discuss results with your group mates, and continue adding missing variables until your products are transformed into minterms, or your sums into maxterms.

There are some notes and a rec. on the analysis of Circuit_K using method I.

| Specifications | Planning | Developing | 4. Testing | Report |

Testing means to check or verify that the solution is correct and agrees with the initial specifications.

In this analysis section, the simplest way to check the truth table is by comparison with the truth table obtained by other methods.

| Specifications | Planning | Developing | Testing | 5. Report |

Project report: sheets of paper, scanned and annotated figures, file listings, notes or any other resources. In CSD follow this rubric of indications for writing reports.

| Method I | Circuit_K method II | Method III | Method IV |

| 1. Specifications | Planning | Developing | Testing | Report |

Deduce the truth table of Circuit_K in Fig. 1 using analysis method II and compare and discuss solutions.

|

| Fig. 1. Example Circuit_K to analyse. |

| Specifications | 2. Planning | Developing | Testing | Report |

Planning means organising and discussing how to proceed to reach solutions. A flow chart of sequential operations will be necessary to explain what to do, how to do it and when.

- Choose Proteus as circuit simulator: draw/capture the circuit schematic in Proteus and run a simulation.

- In CSD we never start a project or a simulation from scratch, but we copy and adapt from similar exercises found here in this digsys web. For example, use files to copy and adapt from Lab 1.1.

- Select a library of a classic technology, for instance LS-TTL or CMOS series 4000.

- Try all the possible input combinations to fill in and complete the truth table.

Project location:

C:\CSD\P1\Circuit_K\Proteus\Circuit_K.pdsprj (the circuit captured in Proteus to be simulated)

| Specifications | Planning | 3. Developing | Testing | Report |

Developing means executing a given plan to achieve a circuit solution. Circuit simulator: Draw/capture the circuit schematic in Proteus and run a simulation.

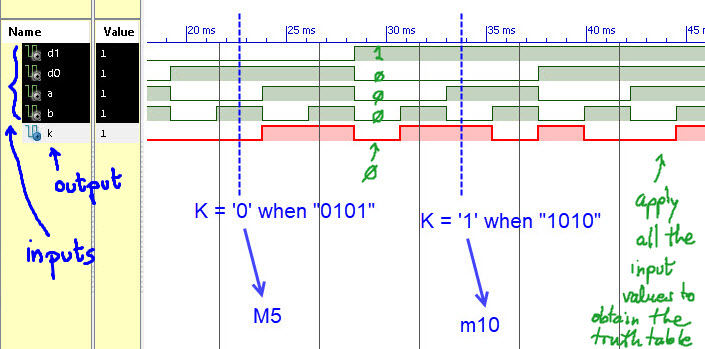

Try all the possible input combinations to complete the truth table. Use, copy and adapt files from Lab 1.1. This is an example circuit captured: Circuit_K.pdsprj.

|

| Fig. 2. This is the solution of the truth table for a given input stimulus vector. You can repeat 2^4 = 16 times to measure and an write down the complete truth table (but print only a few combinations). |

| Specifications | Planning | Developing | 4. Testing | Report |

Testing means to check or verify that the solution is correct and agrees with the initial specifications.

In this analysis section, the simplest way to check the truth table is by comparison with the truth table obtained by other methods.

| Specifications | Planning | Developing | Testing | 5. Report |

Project report: sheets of paper, scanned and annotated figures, file listings, notes or any other resources. In CSD follow this rubric of indications for writing reports.

| Method I | Method II | Circuit_K Method III | Method IV |

| 1. Specifications | Planning | Developing | Testing | Report |

Deduce the truth table of Circuit_K in Fig. 1 using analysis method III and compare and discuss solutions.

|

| Fig. 1. Example Circuit_K to analyse. |

| Specifications | 2. Planning | Developing | Testing | Report |

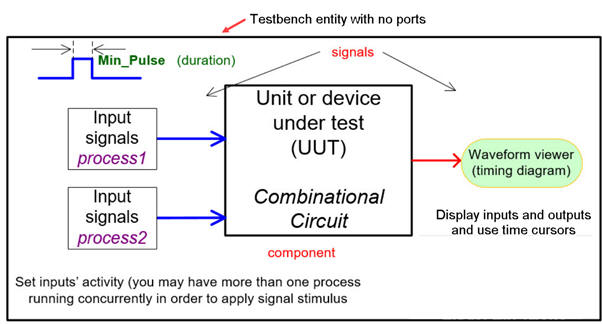

VHDL synthesis and simulation project.

- Translate to VHDL Circuit_K algebraic equation in Fig. 1 using a similar file to copy and adapt.

- Choose a target chip, for instance CPLD MAX II EPM2210F324C3, and start a VHDL synthesis project using an EDA tool, for instance Quartus Prime.

- Examine and print the RTL and technology schematics.

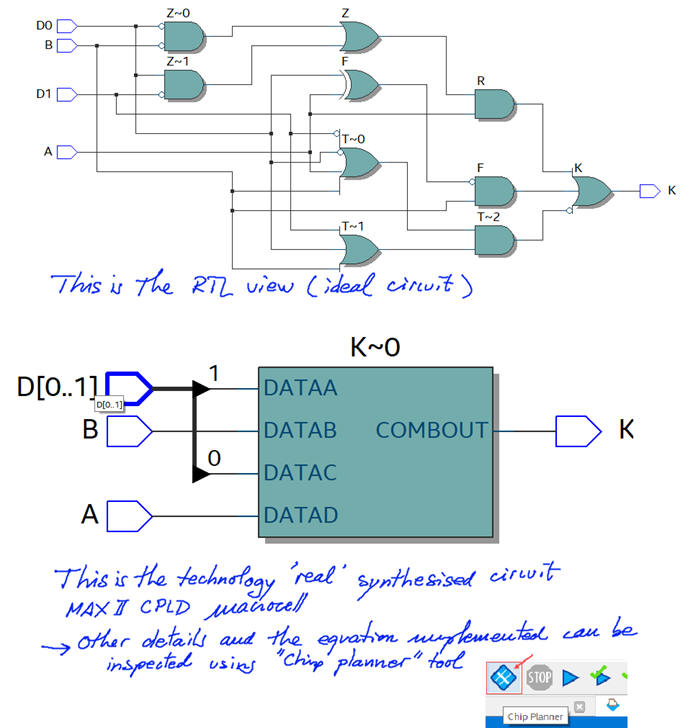

- Start a VHDL simulation project, for instance in ModelSim-Intel FPGA Starter Edition, using a testbench to input signal stimulus .

Project location:

C:\CSD\P1\Circuit_K\VHDL\Circuit_K.vhd, Circuit_K_tb.vhd (VHDL files for running the EDA tools)ç

| Specifications | Planning | 3. Developing | Testing | Report |

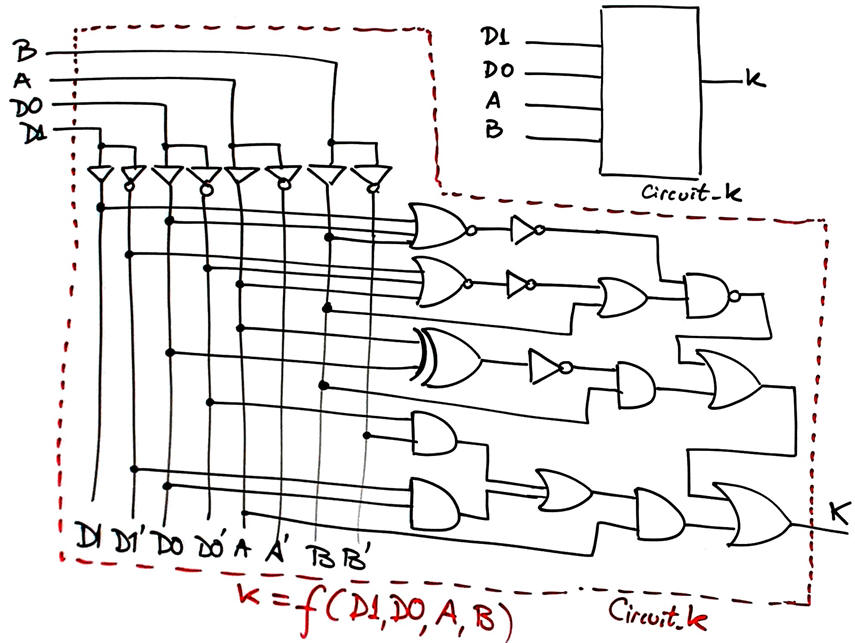

Write a VHDL file like this Circuit_K.vhd consisting of entity and architecture based on the circuit's algebraic equation shown in Fig. 2.

Start a VHDL synthesis project using an EDA tool for a given target chip, such MAX II EPM2210F324C3 CPLD from Intel.

|

| Fig. 2. RTL and technology results. |

Once examined the RTL and technology views, continue starting a VHDL simulation project using a testbench to obtain the circuit's truth table. This is an example testbench Circuit_K_tb.vhd file written translating all truth table combinations into the skeleton generated from Quartus Prime.

|

| Fig. 3. VHDL testbench fixture for measuring how the circuit works using a timing diagram when applying several input stimulus. |

In this analysis project, simulation all truth table combinations will allow us complete the circuit's truth table.

|

Fig. 4. Example of a simulation using VHDL tools of the Circuit_K. Testing all the combinations means obtaining the truth table of the circuit as it was done using the method I in Proteus. |

| Specifications | Planning | Developing | 4. Testing | Report |

Testing means to check or verify that the solution is correct and agrees with the initial specifications.

In this analysis section, the simplest way to check the truth table is by comparison with the truth table obtained by other methods.

| Specifications | Planning | Developing | Testing | 5. Report |

Project report: sheets of paper, scanned and annotated figures, file listings, notes or any other resources. In CSD follow this rubric of indications for writing reports.

These are some notes on the project reporting.

| Method I | Method II | Method III | Circuit_K method IV |

| 1. Specifications | Planning | Developing | Testing | Report |

Deduce the truth table of Circuit_K in Fig. 1 using

analysis method IV and compare and discuss solutions. Fig. 1. Example Circuit_K to analyse.

Numerical engine

WolframAlpha

to be used for inferring the truth table from the circuit's

algebraic equation. Fig. 2. Planning

the method IV as a bullet list of

operations.

- Write the circuit equation in Fig. 3 in a text

file step-by-step.

- Use files to copy and adapt them from

Lab 1.1.

or

WolframAlpha.

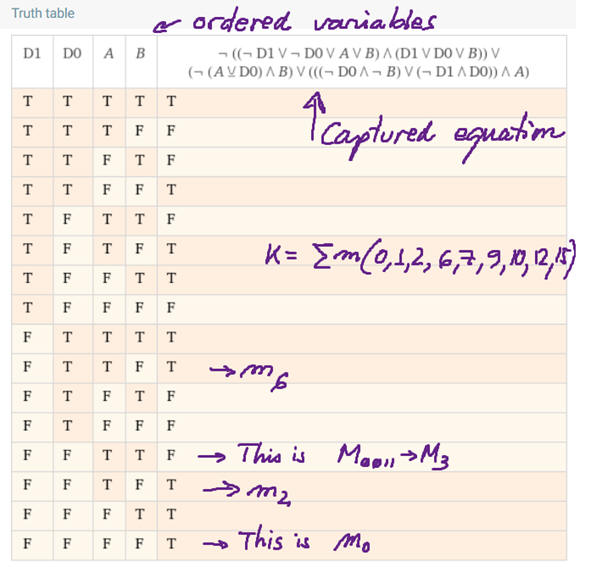

- Reorder input variables if such is the case before annotating maxterms and minterms.

- Draw the truth table. - Project location: C:\CSD\P1\Circuit_K\Wolfram\Circuit_K.txt (logic equations

compatible with WolframAlpha engine) Deducing the circuit's equation analysing the circuit. Fig. 3. Circuit and equation.

Write the circuit equation in a text file step by step, for instance,

Circuit_K_equation.txt. Copy and paste it in WolframAlpha and run the engine to obtain the circuit's

truth table. pay attention to the variable order before

annotating minterns or maxterms. Fig. 4. WolframAlpha results from the circuit's equation in Fig. 3. These are some notes on the project reporting using WolframAlpha tool. Testing means to check or verify that the solution is

correct and agrees with the initial specifications. In this analysis section, the simplest way to check the truth

table is by comparison with the truth table obtained by other methods. Project report: sheets of paper, scanned

and annotated figures, file listings, notes or any other resources.

In CSD follow this

rubric of

indications for writing reports.

Specifications

2. Planning

Developing

Testing

Report

Specifications

Planning

3. Developing

Testing

Report

Specifications

Planning

Developing

4. Testing

Report

Specifications

Planning

Developing

Testing

5. Report