Chapter 1 problems |

- D1.12 - |

16-bit comparator for integer numbers |

1. Specifications

Build the comparator Int_Comp_16bit represented in Fig. 1 for 16-bit two's complemented (2C) integer operands.

The same project B3.12 (for 8-bit operands) is proposed in Chapter 3 for learning the basics of μC software organisation and basic digital I/O.

|

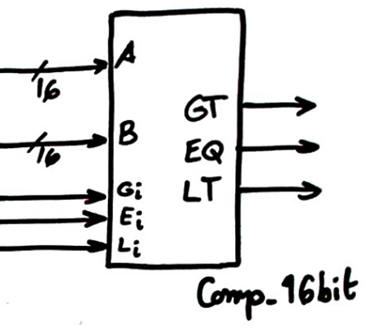

| Fig. 1. Symbol. |

PLA3 specifications include: symbol, truth table, data range, example commercial chips with similar functionality, etc. You may like to add theory to better explain and comprehend these circuits.

Draw the testbench fixture and an example of timing diagram to be used later as stimulus in the VHDL verification of the synthesised circuit. Consider Min_Pulse = 53.6 ms. You can use as example test vectors for the integer operands A and B (add other numbers if you like):

-

Option #1: (+32760), (+18841), (-30504), (-22), (+18340), (-13740), 0, (+31220)

-

Option #2: (-31554), (+22780), (-19306), (+12408), (-5), 0, (-5545), (+15554)

-

Option #3: (-17306), (+30701), (+32767), (-29830), 0, (-13208), (+6), (-19301)

If we liked to test all the circuit, how long would it take to run the full verification?

Int_Comp_16bit target chip is one of the following:

-

Option #1: MAX II EPM2210F324C3.

-

Option #2: Cyclone IV EP4CE115F29C7

MAX10 chips are not used because Intel Quartus Prime does not generate the "*.sdo" file for running gate-level simulations with this technology.

Additional specifications for PLA4_1 for performing timing simulations and measurements:

Calculate the propagation delay in a given signal transition using gate-level simulationsin VHDL.

Calculate the circuit's longest propagation delay and maximum speed for a given target chip using the timing analyser tool.

If we liked to test all the circuit, how long would it take?

Be aware that the location of this project enhanced with timing simulation and measurements (section 5) is:

C:\CSD\P4\Int_Comp_16bit\(files)

2. Planning

Invent the plan C2 schematic for this Int_Comp_16bit after having studied the example Int_Comp_8bit and designing the Comp_16bit as indicated in the annex below.

Project location:

C:\CSD\P3\Int_Comp_16bit\(files)

Annex: |

Comp_16bit |

16-bit comparator for radix-2 numbers |

Specifications

Build the 16-bit radix-2 comparator Comp_16bit represented in Fig. 1.

|

| Fig. 1. Comp_16bit symbol. |

Specifications include: symbol, truth table, data range, example timing diagram and comparison operations, example commercial chip, etc.

Draw an example of timing diagram for the testbench fixture to be used later as stimulus in the VHDL verification of the synthesised circuit.

2. Planning

Two options are possible for this Comp_16bit:

-

Option #1: expanding Comp_4bit in a ripple chain plan C2. Draw and fully annotate your schematic to be ready for VHDL translation.

-

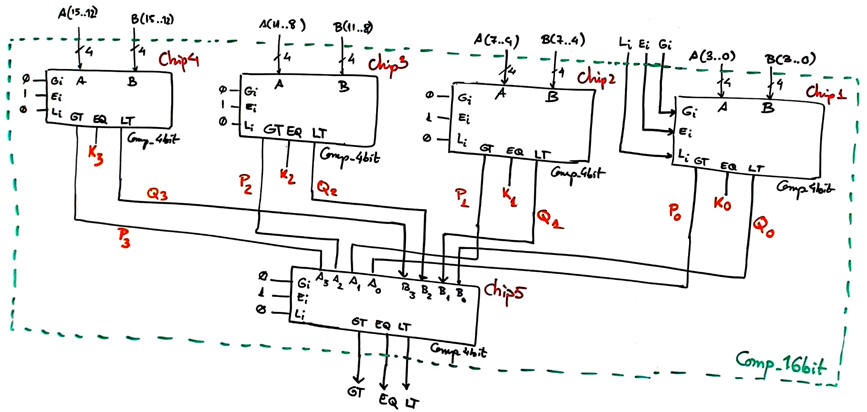

Option #2: Parallel tree expansion plan C2 as proposed in the architecture the Comp_16bit component is represented in Fig.2.

|

| Fig. 2. 16-bit tree comparator network adapted from this reference book: Ercegovac, M., Lang, T., Moreno, J. H., "Introduction to Digital Systems", John Wiley & Sons, 1999). It includes slides: Chapter 10 is on arithmetic circuits. This is Fig. 10.17 in the referenced book slides. |

Two options are possible for the component Comp_4bit:

-

Option #1: Using plan C2 to obtain a ripple comparator chaining expandable Comp_1bit as as shown in this project Comp_4bit.

-

Option #2: Using plan A equations as shown in this project Comp_4bit. This plan implies that the Comp_1bit component is not required.

And finally we got up to four proposals for inventing the Comp_1bit component, three of which are already available in our product examples:

-

Option #1: Comp_1bit plan A (minimised equations from the truh table in the form of PoS or SoP)

-

Option #2: Comp_1bit plan B (behavioural interpretation of the truth table)

-

Option #3: Comp_1bit plan C2 based on the method of multiplexers (MoM)

-

Option #4: Comp_1bit plan C2 based on the method of decoders (MoD) proposed as follows:

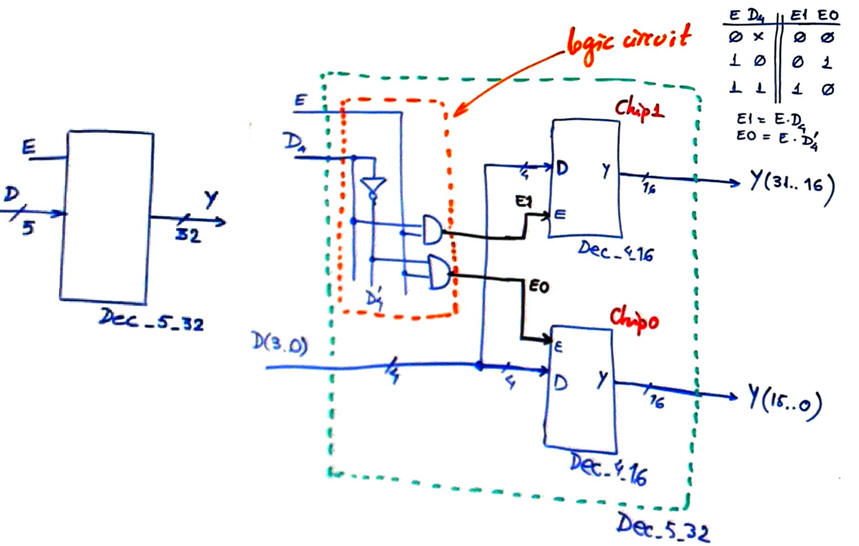

Find in our Comp_1bit tutorials the specifications (symbol, truth table, etc). Study how the decoders work in L2.3, use the the Dec_4_16.vhd component to implement the Dec_5_32 required in this application following the ideas in Fig. 3.

|

| Fig. 3. Designing a larger Dec_5_32 expanding Dec_4_16. |