|

|

|||

|

|

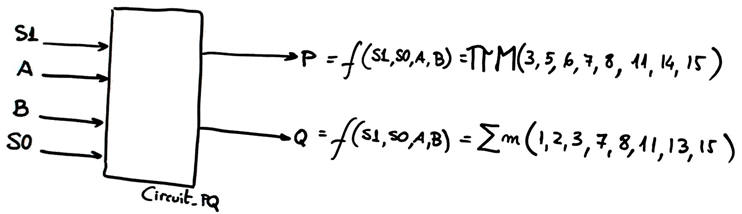

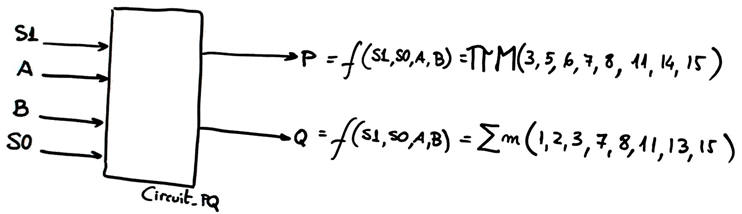

Design the Circuit_PQ using plan B |

Circuit_PQ plan C2 |

|

| B1: schematic | B2: flowchart |

| 1. Specifications | Planning | Developing | Testing | Report | Prototype |

B1. Implement the circuit in Fig. 1 using a VHDL behavioural plan B based on capturing the truth table directly translating a schematic interface.

|

| Fig. 1. Circuit_PQ to desing. |

| Specifications | 2. Planning | Developing | Testing | Report | Prototype |

The project location may be:

C:\CSD\P2\Circuit_PQ_B1\(files)

| Specifications | Planning | 3. Developing | Testing | Report | Prototype |

| Specifications | Planning | Developing | 4. Testing | Report | Prototype |

| Specifications | Planning | Developing | Testing | 5. Report | Prototype |

Follow this rubric for writing reports.

| Specifications | Planning | Developing | Testing | Report | 6. Prototype |

We can use the DE10-Lite board to implement this project, as shown in Lab 1.2 for the similar Circuit_W.

| B1: schematic | B2: flowchart |

| 1. Specifications | Planning | Developing | Testing | Report | Prototype |

B2. Implement the circuit in Fig. 1 using a behavioural plan B based on interpreting the truth table as a flowchart.

|

| Fig. 1. Circuit_PQ to desing. |

| Specifications | 2. Planning | Developing | Testing | Report | Prototype |

The project location may be:

C:\CSD\P2\Circuit_PQ_B2\(files)

| Specifications | Planning | 3. Developing | Testing | Report | Prototype |

| Specifications | Planning | Developing | 4. Testing | Report | Prototype |

| Specifications | Planning | Developing | Testing | 5. Report | Prototype |

Follow this rubric for writing reports.

| Specifications | Planning | Developing | Testing | Report | 6. Prototype |

We can use the DE10-Lite board to implement this project, as shown in Lab 1.2 for the similar Circuit_W.