|

L7.3: Counter truncation; counter and register expansion [P7] Count truncation (plan C2). Chaining counters and registers (plan C2). |

[19/11] |

2.7.4. Count truncation and count expansion

2.7.4.1. Concepts and chaining signals

2.7.4.2. Design plan C2: designing counters using hierarchical structures, standard components (Counter_mod16) and logic, VHDL hierarchical multiple-file project

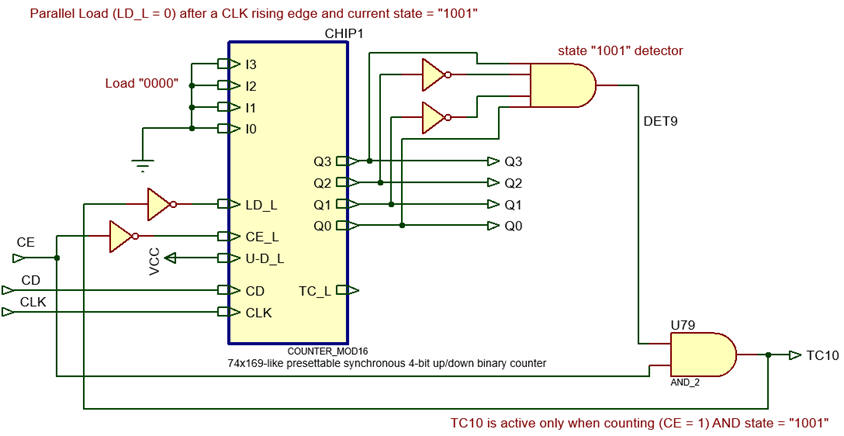

2.7.4.2.2. Example of count truncation: Decade counter (10 states) or Counter_BCD_1digit

- Design: Counter_BCD_1digit using plan C2 and a Counter_mod16 as component.

Other count truncation examples:

- Design the Counter_mod12 using plan C2 and a Counter_mod16 as component (LAB7)

2.7.4.2.3. Example of count expansion: 2-digit BCD counter (modulo 100)

Count expansion. Let us discuss about the concept of counter or register expansion (chaining/rippling). In this way you can design a counter or a register of any size using plan C2 and building blocks. This is a Counter_BCD_2digit in Proteus.

2.7.4.2.4. Example of count truncation and expansion: Counter_BCD_mod60

Count expansion and truncation

- Design a Counter_BCD_mod60 (minutes or seconds counter) using plan C2 and a Counter_mod16 as component.

2.7.4.2.5. Example of count expansion: Hour_counter (Counter_BCD_mod24)

- Design an Hour_counter (or Counter_BCD_mod24) using plan C2 and a Counter_mod16 as component.

How to plan a typical YY-MM-DD HH:MM:SS calendar watch? This DS1307 chip is an example of real-time calendar. How many bits are necessary for implementing a 100 years calendar (counting in BCD, counting in binary sequential)?

How to invent a BCD counter modulo 10.000.000 using Counter_BCD_1digit components? For instance, this is a professional frequency/period meter instrument that includes such large counter.

Invent a reversible Counter_mod128 with adjustable count between Min_count and Max_count. For instance if CE = '1', UD_L = '0', Min_count = 40; Max_count = 50, the device will generate the following eleven state sequence: 50, 49, 48, ..., 41, 40, 50, 49, ...

You may think on the following plan based on several steps: (1) invent a Counter_mod128 with parallel inputs, using plan Y or using plan C2 including two Counter_mod16. (2) Discuss a plan C2 schematic on how to make it adjustable between Min_count and Max_count using standard components such multiplexers and comparators.

Data register expansion.

- Invent a Data_reg_16bit using Data_reg_4bit components and plan C2.

Compare the solution with the design of a Data_reg_16bit using plan Y.

Shift register expansion.

- Invent a Shift_reg_12bit using Shift_reg_4bit components and plan C2.

Compare the solution with the design of a Shift_reg_12bit using plan Y.

Exercise: Invent a Shift_reg_10bit using Shift_reg_4bit components and plan C2. How many VHDL files are required?

Compare the solution with the design of a Shift_reg_10bit using plan Y. How many VHDL files are required? Which technology schematic uses more resources (logic elements and D_FF?

Exercise: Invent a Counter_mod38 using Counter_mod16 components and plan C2. How many VHDL files are required? Solve it in two steps: (1) study how to expand up to 8-bit modulo 256; (2) truncate at the 37 state. How many VHDL files are required? Which? How many D_FF will contain the circuit?

Compare the same Counter_mod38 solved using using plan Y. How many VHDL files are required? Which? How many D_FF will contain the circuit?