|

Lecture 2 |

L7.2: Registers [P7] Standard sequential blocks: Synchronous data and shift registers (Plan Y and plan C2) |

[15/11] |

2.7.5. n-bit data register: for example Data reg_4bit

2.7.5.1. Symbol, function table, parallel load, timing diagram, state diagram, commercial chips

This is the key component for saving data.

2.7.5.2. Plan Y

2.7.5.3. Plan C2 using components (Counter_mod16 or Data_reg_4bit)

As an alternative, figure out how to plan a Data_reg_16bit using plan C2 and Data_reg_4bit components

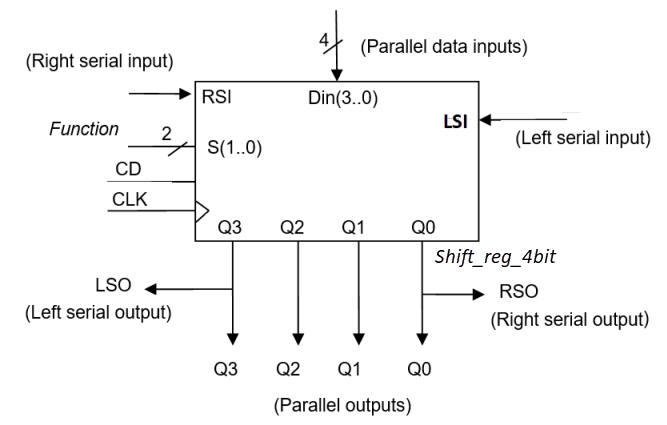

2.7.6. n-bit shift register: for example Shift reg_4bit

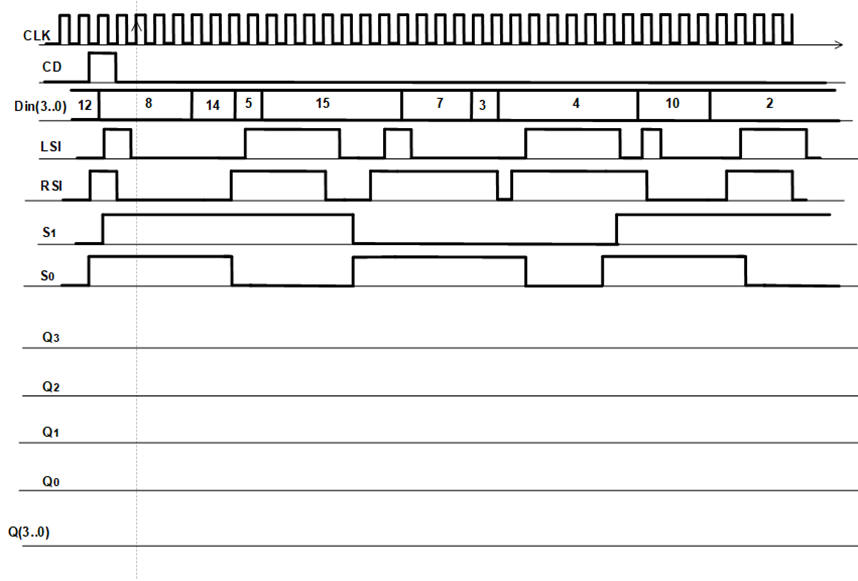

2.7.6.1. Symbol, function table, parallel load, timing diagram, state diagram, commercial chips

2.7.6.2. Plan Y

Type 74LS94, where the parallel input - parallel output mode of operation is identical to the data register.

2.7.6.3. Plan C2 using components Shift_reg_4bit

Figure out how to plan a Shift_reg_32bit using plan C2 and Shift_reg_4bit components

Exercise: Draw an example timing diagram (pdf)of the Shift reg_4bit