|

Lecture 3 |

L5.3: Flip-flop specifications and applications [P5] - D-type, JK, and T flip-flops |

[18/10] |

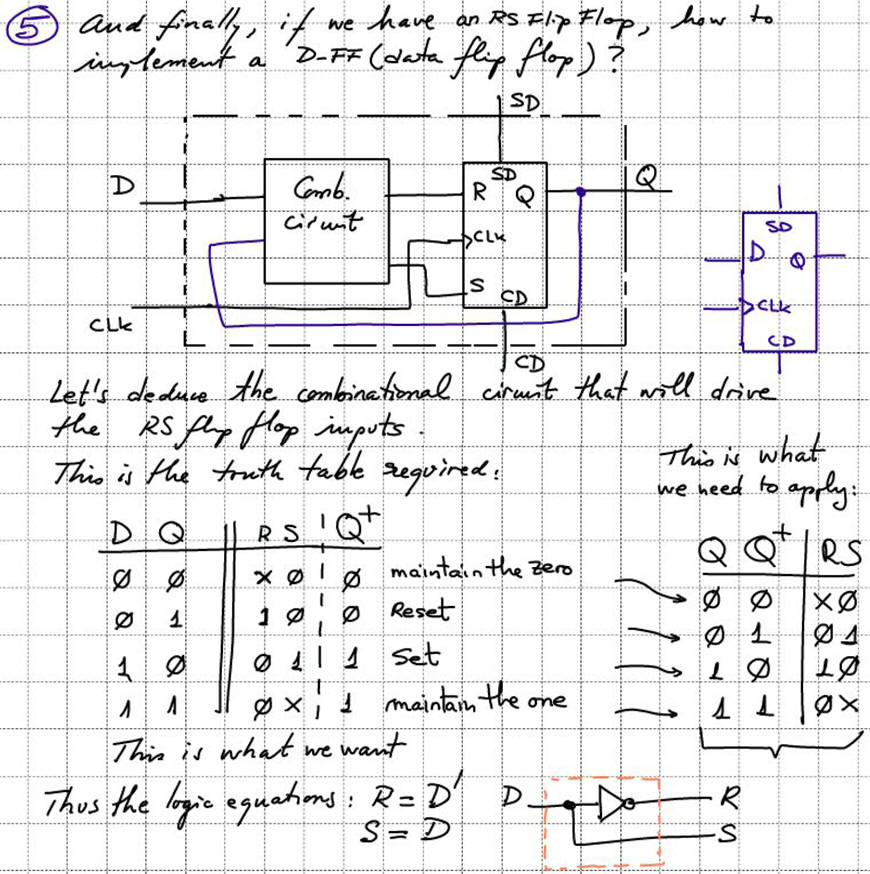

2.3.6.2. Data flip-flop (D_FF)

2.3.6.2.1. Function table, state diagram, timing diagram

This is the full tutorial on designing our D_FF. In the development section are presented two VHDL files that translate the behaviour of this component.

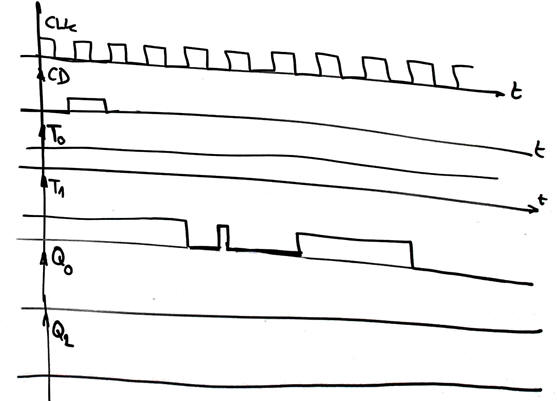

2.3.6.2.2. Deducing D_FF from RS_FF

As an alternative, we can add a bit of theory using plan C2 to imagine D_FF from the previous RS_FF.

2.3.6.2.3. Commercial chip

A standard commercial D_FF is the 74HCT273.

2.3.6.3. JK flip-flop (JK_FF)

2.3.6.3.1. Function table, state diagram, timing diagram

This is the full tutorial on designing our JK_FF. In the development section are presented two VHDL files that translate the behaviour of this component.

2.3.6.3.2. Commercial chip

Classic chips of this kind are HEF4027B and 74HCT73.

2.3.6.4. Toggle flip-flop (T_FF)

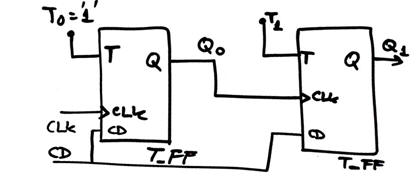

2.3.6.4.1. Function table, state diagram, timing diagram

This is the full tutorial on designing our T_FF.

2.3.6.4.2. Frequency divider by two

This is simple and typical application if such component, imagining it a a CLK's frequency divider by 2. We will take advantage of this circuit when inventing CLK generator circuits in P8.

Flip-flops are basic building blocks for digital systems. They are very well documented.

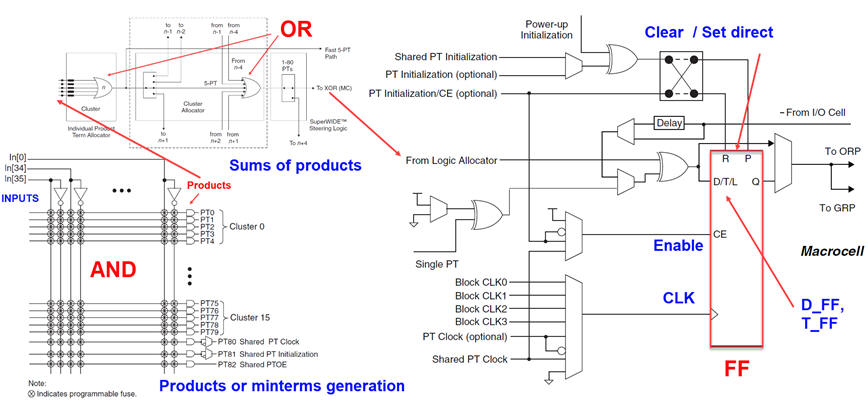

Programmable logic devices (PLD) implements logic functions using SoP or sums of minterns. Additionally each cell contain a flip-flop. For instance, the Lattice Semiconductor CPLD ispMACH4128V contains 128 logic blocks and macrocells. Each macrocell includes a configurable register D_FF along with some logic for CD, SD, CLK and enable.

2.3.7. Analysis of asynchronous and synchronous circuits based on flip-flops and logic

NOTE. Analysis of circuits with memory cells and gates (such the one presented in P5 is covered in several tutorial projects, where we propose three analysis methods:

2.3.7.1. Method I: Handwritten pen-and-paper analysis and discussion.

2.3.7.2. Method 2 Proteus simulation

2.3.7.3. Method 3 VHDL synthesis and simulation.

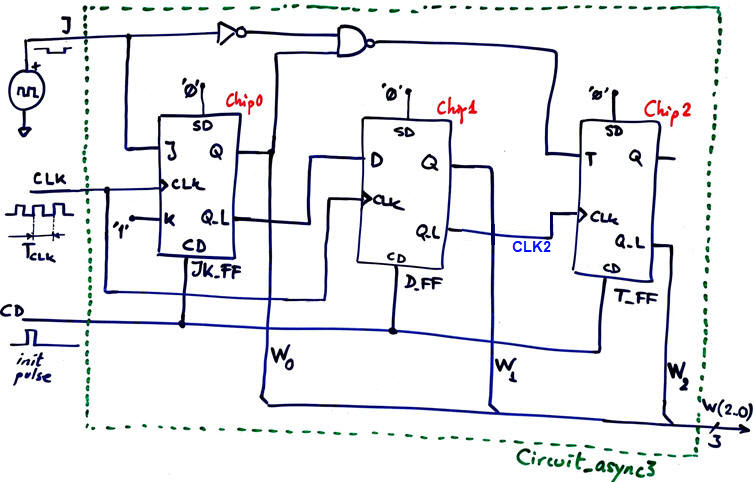

Thus, let us repeat and apply again the same three P1 analysis methods. This below is another example circuit:

Specifications: Find the timing diagram and infer which binary codes are available at output W(2..0). Imagine that J is a 70% duty cycle waveform of 230 Hz, and fCLK = 2.5 kHz.

Planning: You can use the three analysis methods and compare results.

You can organise several steps:

Step #1: Only the first JK_FF Chip0

Step #2: Only Chip0 and Chip1

Step #3: The complete circuit

Exercise: Deduce the outputs of the circuit below: