|

L5.2: RS flip-flops [P5] On the internal architecture of an RS flip-flop, CLK and clear direct concepts |

[15/10] |

2.3. Flip-flop. Synchronous 1-bit memory cell

2.3.1. The concept of CLK signal. Synchronicity

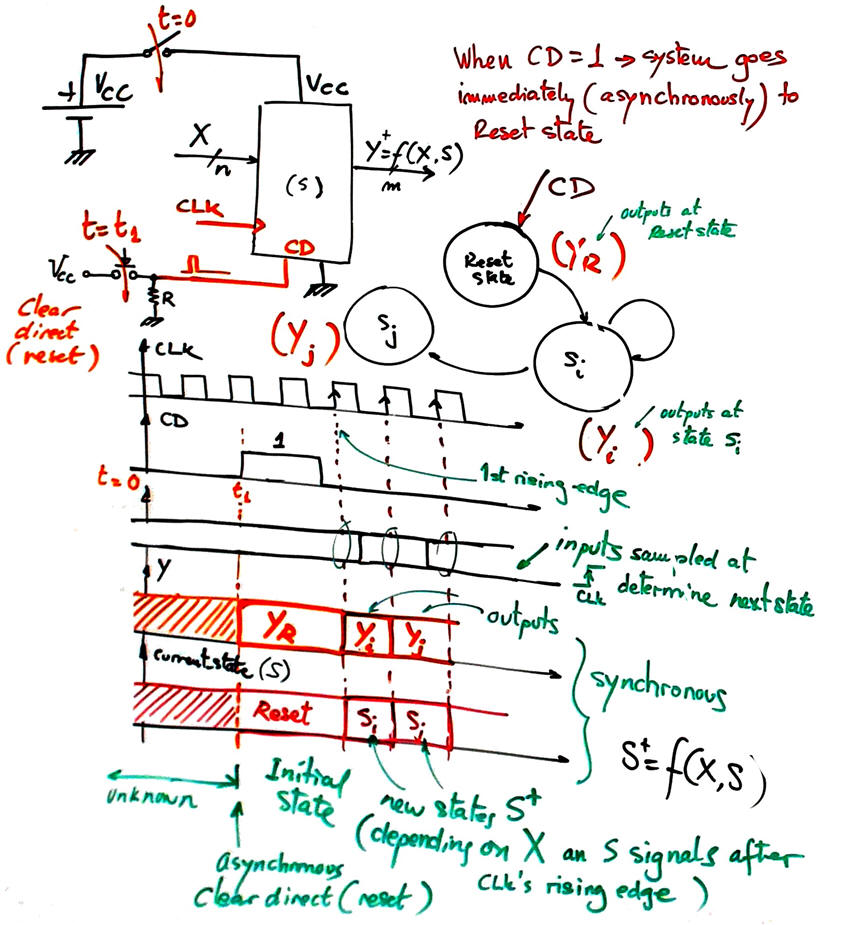

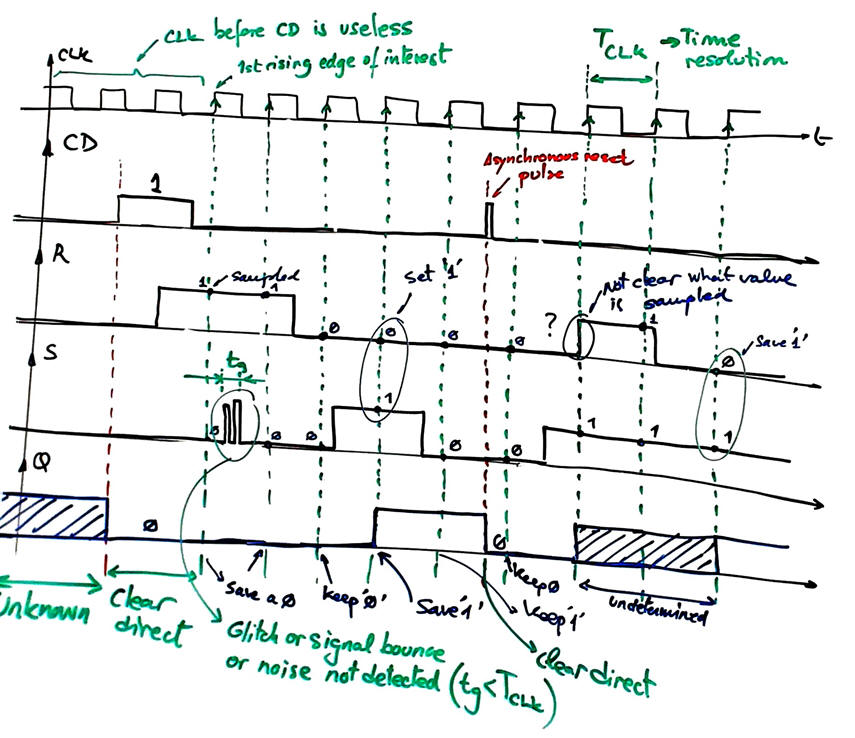

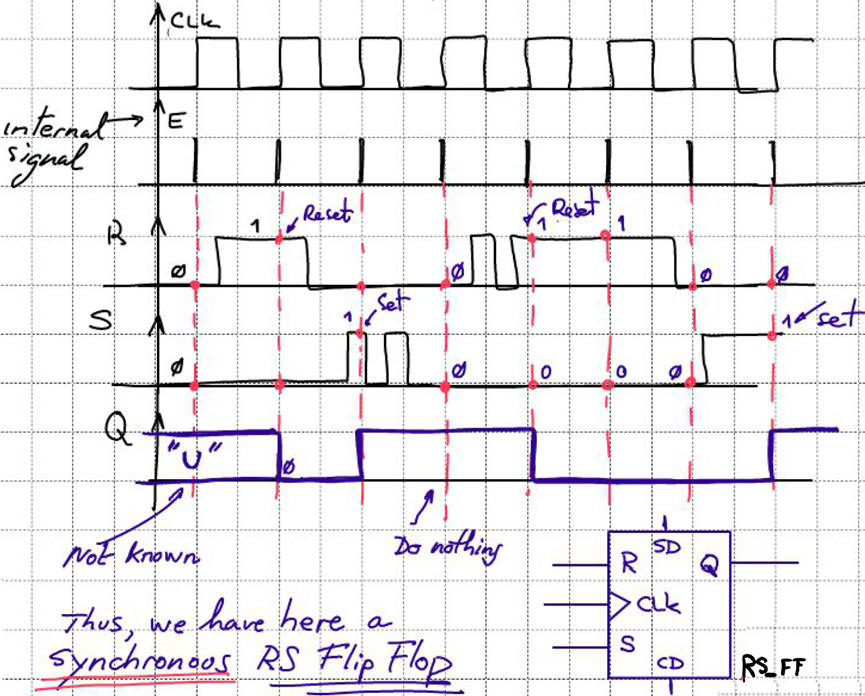

In a digital system, outputs (Y) and internal states (S) update to the future value only on the CLK's rising edge transition, this is the idea of synchronicity or synchronous digital system.

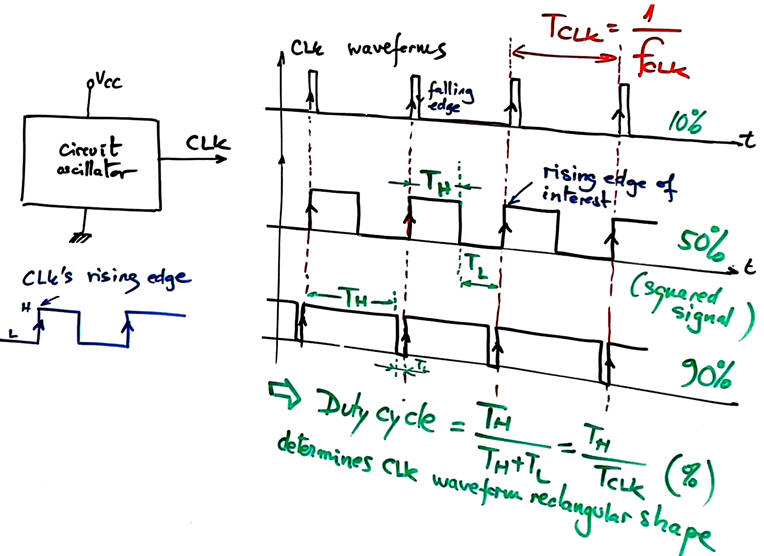

Digital CLK oscillators generates rectangular signals for running digital systems. One rising edge per period.

2.3.4. The concept of clear direct (CD), asynchronous reset or master reset.

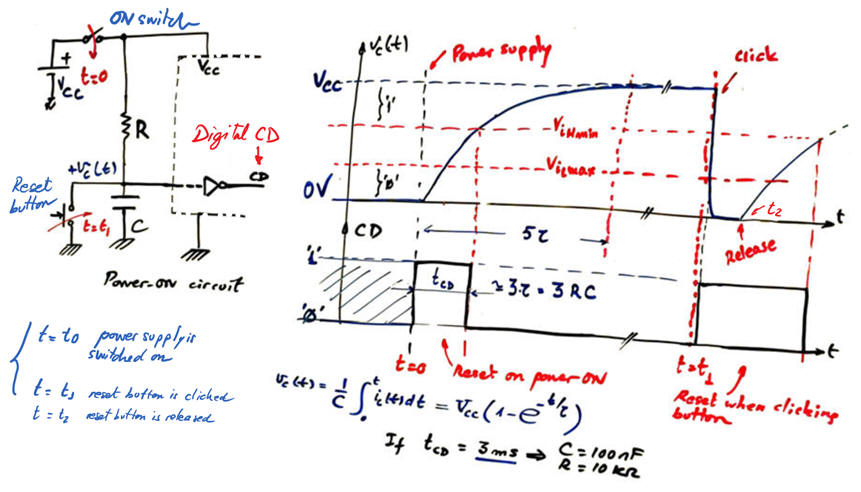

In a digital system time starts when turning ON the power supply at t = 0. System internal state (S) and outputs (Y) remains undetermined, unknown or unpredictable until a reset or clear direct (CD) button is clicked at t = t1. While CD is set high, the systems remains at its initial state. Once CD is low the system starts updating outputs (Y) and internal states (S) after each CLK's rising edge.

2.3.5. Automating system initialisation: power-ON reset.

2.3.6. Standard flip-flops

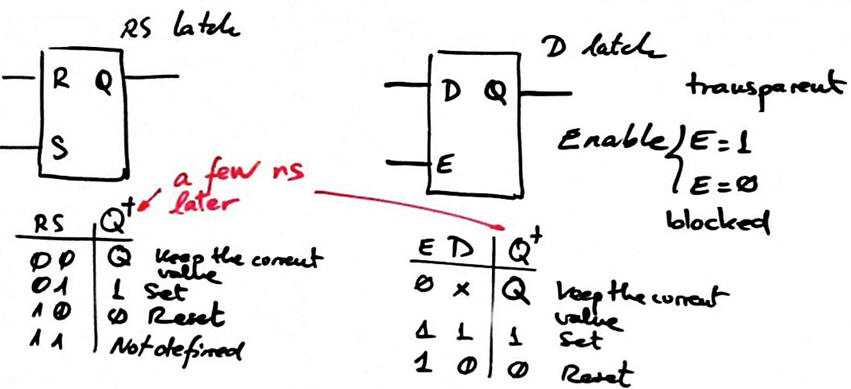

In previous lesson we studied asynchronous latches RS_latch and D_Latch

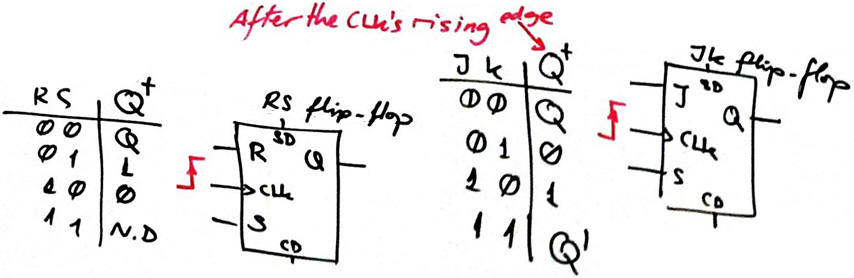

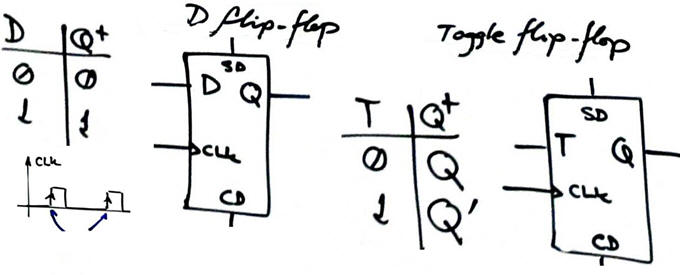

Now we can present common types of synchronous flip-flops, 1-bit memory cells: RS_FF, D_FF, JF_FF and T_FF .

2.3.6.1. RS flip-flop (RS_FF)

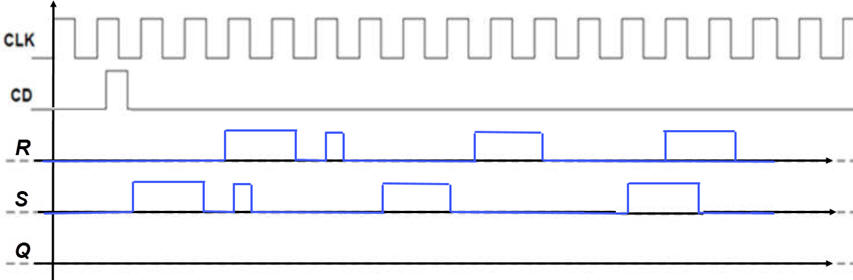

2.3.6.1.1. Function table, state diagram, timing diagram

Run in Proteus the RS_FF.pdsprj example to grasp differences with respect a latch. What is the meaning of sampling input values?

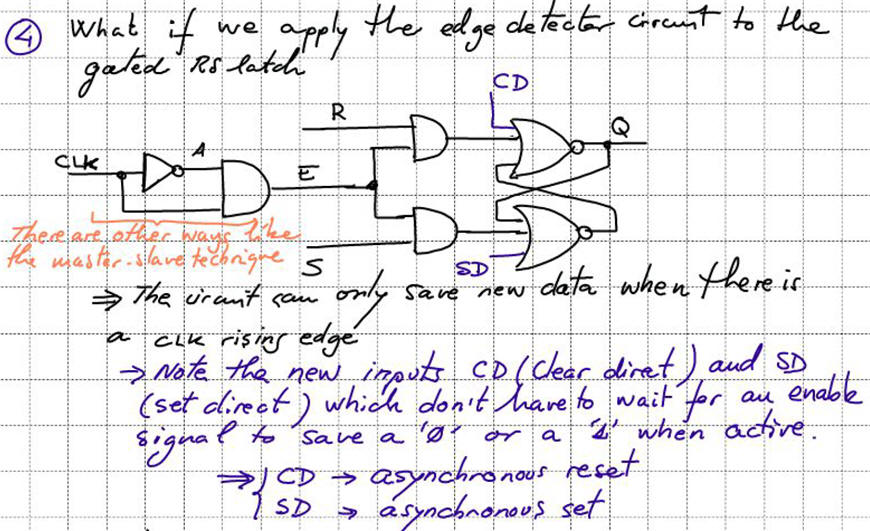

2.3.6.1.2. Deducing RS_FF from RS_latch, CLK's rising-edge detector

Proposing an RS_FF circuit from plan A: how to deduce an RS_FF from an RS_latch?

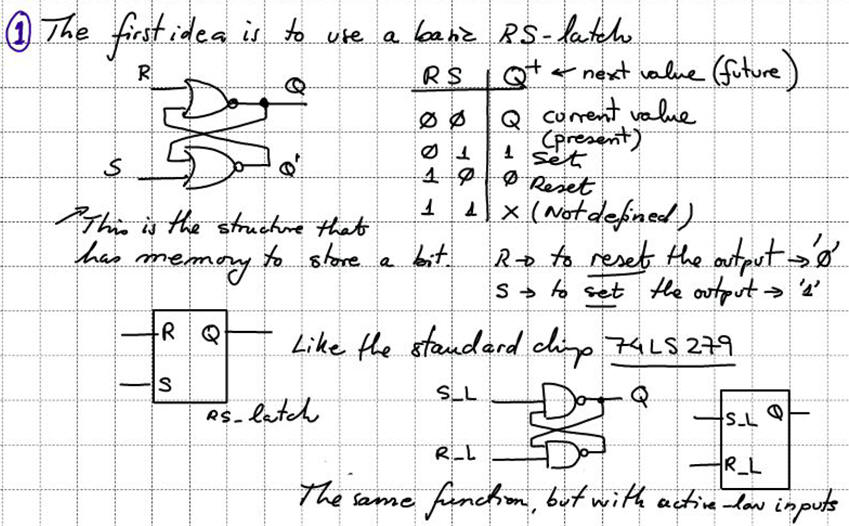

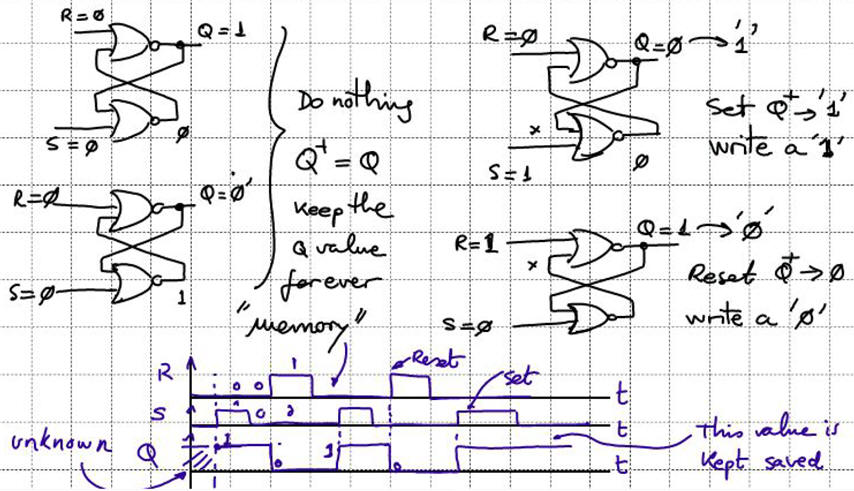

1. RS_latch operation

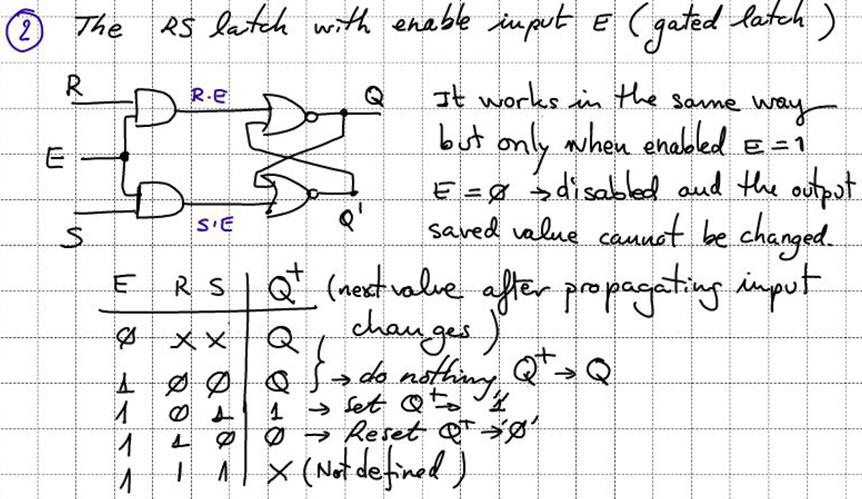

2. From RS_Latch to gated RS_Latch

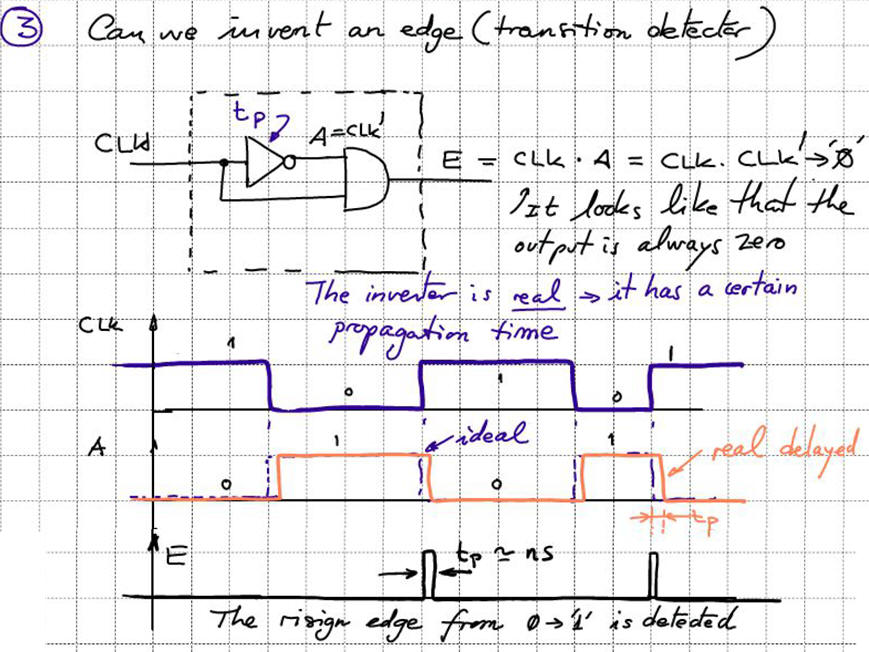

3. Edge detector circuit to convert CLK input into enable signal input

4. From gated RS latch to RS_FF

This an idea on how a CLK rising edge can trigger the sampling of inputs. Other circuits are proposed in literature, for instance master-slave configuration.

Fortunately, we well describe such components using a much simple, easier and repetitive behavioural approach, leaving to EDA tools the synthesis of such memory cells in FPGA fabrics.

2.3.6.1.3. Commercial chip

A classic chip is HEF4027B.

Exercise: Analyse the following RS_FF applying its function table.