|

|

|||||

Chapter 3 problems |

- D3.6 - |

7-segment digit sequencer (μC - C) |

|||

|

|

|||||

1. Specifications

We want to design a driver to show a sequence of movement, clockwise and counter-clockwise, in a single 7-segment display. The application will be implemented in a PIC18F4520 microcontroller chip.

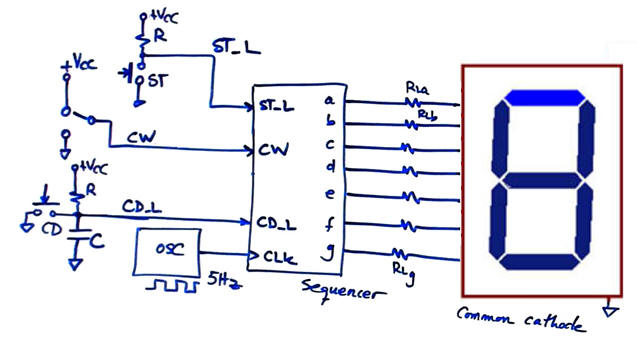

Fig. 1 represents the schematic diagram of the application. CLK signal to move segments is a 5 Hz rectangular wave. There is a switch to configure movement direction: CW = '1', clockwise; CW = '0' counter-clockwise.

The same project designed using hardware is stated in D2.6.

a) a)  |

|

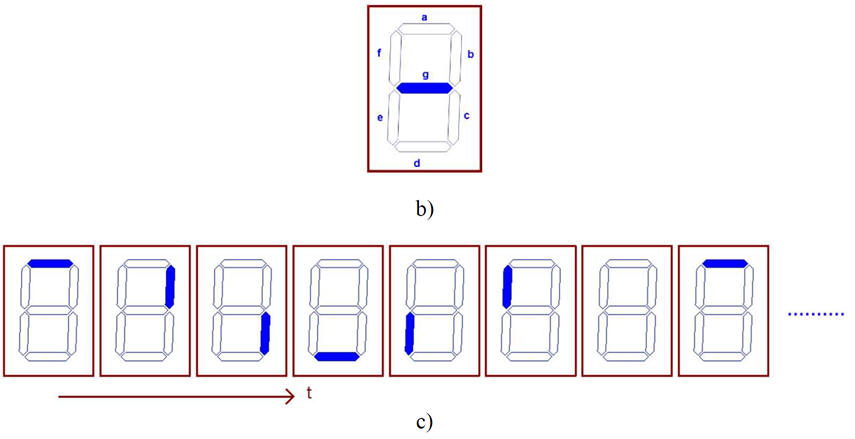

Fig. 1. a) Circuit schematic. b) Digit segments and position when idle. c) Sequence of switching LED segments for CW = '1' clockwise or up-counting. |

Fig. 1c shows the sequence of segment lighting when CW = '1'. When the system remains idle, the only segment lighting continuously is g.

When clicking the push-button start/stop ST_L the system runs continuously in the configured direction.

When running, if ST_L is clicked again, the system stops after completing the sequence.

2. Planning

Let us build the product organising several design phases, and several steps within each phase.

Design phase #1: basic features

Solve the circuit for the design step #1. Only when it is fully tested working correctly and reported, solve the design step #2.

Design step #1. Consider an initial circuit with no CW input, thus representing only clockwise movement.

Project location:

C:\CSD\P10\seq_s1\(files)

Project source files:

Seq.pdsprj, Seq.c

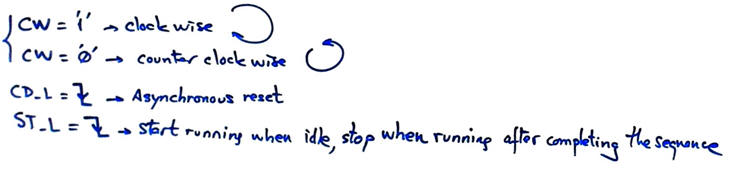

Let us start with the design step #1. We need to use an external interrupt INTx (x = 0, 1, or 2) to start the sequence when the active falling edge is detected. Furthermore, because of the requirement that when running the sequence must end only when completed after detecting an ST_L falling edge, we need to use the same flag.

How to adapt the D2.6. Fig. 2 here? What will be the RS_Latch?

How to generate the outptut codes here? In this design phase, to advance the state diagram, you can use an external 5 Hz oscillator connected to another external interrupt activated on the rising edge. You can start developing and testing using the watch window, imagining a preliminary step where the sequence is running continuously, non stop, not yet controlled by the ST_L generated interrupt.

|

|

Fig. 2. Idea of timing diagram adaptation from D2.6 with no CW input, sequencing in one direction after having detected the interrupt from ST_L falling edge. Thus, we can infer that CLK interrupts may be disabled when Idle. |

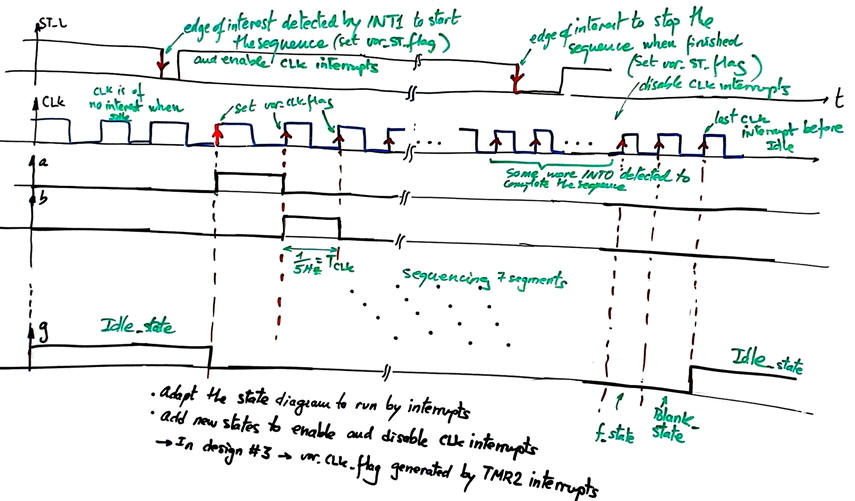

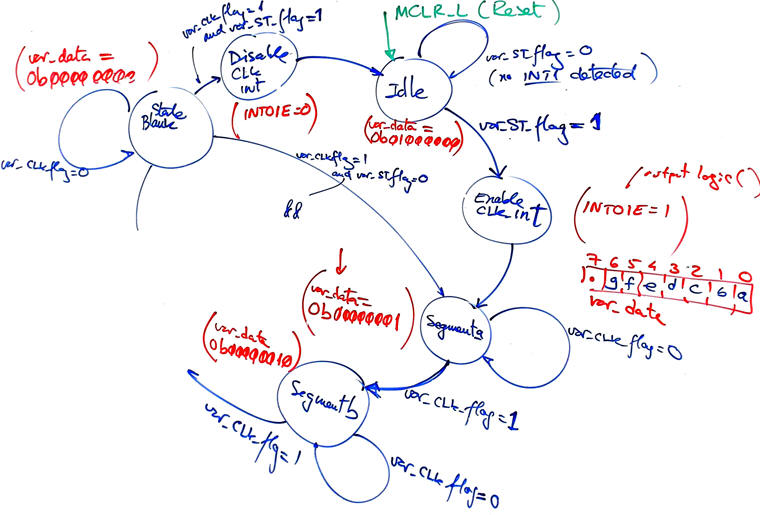

a) Draw the state diagram indicating state transitions and outputs. How the D2.6 Fig. 3 is adapted here? State transitions will depend on external interrupt detections and probably additonal states will be required to enable and disable CLK interrupts, as shown in the Fig. 3 sketch .

|

|

Fig. 3. Idea of state diagram. You better complete it with all the states and outputs generated at the samew time that you imagine the hardware/software diagram and the number of RAM variables required. |

b) Draw the hardware schematic necessary for step #1. ST_L push button, CLK push button or oscillator (5 Hz), outputs a, b, c, d, e f, g, reset circuit MCLR_L, and an 8 MHz quartz crystal oscillator. Explain how to configure the inputs and outputs in init_system().

c) Draw the hardware/software diagram indicating the required RAM variables and how the FSM is solved in software.

d) Draw the truth tables and their equivalent flowcharts for state_logic() and output_logic() functions.

e) What is the interrupt service routine ISR() used in this application? Draw its flowchart. Will the two external interrupt sources be enabled all the time? What is the interrupt that has to be enabled at init_system()?

f) Develop and test (debugging) the project capturing the hardware circuit in Proteus and writting the C source code. You must use the watch window to monitor RAM variables from the very beginning.

Design step #2. Add the CW switch to make the application bidirectional.

Inherit the step #1 source hardware and software files into de new location.

Project location:

C:\CSD\P10\seq_s2\(files)

Project source files:

Seq.pdsprj, Seq.c

a) Draw the hardware schematic necessary for step #2. Add the switch and resistor for input CW. Explain how to configure it in init_system().

Explain what is new in sections b), c), d), e), f)

Develop and test the new feature.

Let us add an LCD display as studied in P11 to this application. The idea is to use several ASCII characters to represent an equivalent sequence.

Project location:

C:\CSD\P11\seq_LCD\(files)

Project source files:

Seq_LCD.pdsprj, Seq_LCD.c

g) Enhance the schematic from the previous design phase #1 to include an LCD attached to port D as studied in tutorials.

h) Enhance the software and the source file to drive the LCD.

In this design phase you can learn the LCD interface step by step. For instance:

Design step #1. Print ASCII messages on the LCD.

Design step #2. Print as well the number of rotations (dynamic numerical data).

Develop and test the new feature.

Design phase #3: Using TMR2 peripheral subsystem.

The external CLK is replaced by the internal 8-bit TMR2 peripheral to generate interrupts (TMR2IF). Discuss the main features of this peripheral and its applications.

Project location:

C:\CSD\P12\seq_LCD_TMR2\(files)

Project source files:

Seq_LCD_TMR2.pdsprj, Seq_LCD_TMR2.c

i) Calculate TMR2 parameters required to generate a CLK of 5 Hz (var_CLK_flag period = 200 ms) to run the machine so that the external CLK signal can be eliminated.

j) Add a new switch SP (speed) to be able to select between two different rotation periods: 200 ms and 100 ms.

Develop and test the new feature.