|

|

|||||

Chapter 1 problems |

- A1.3 - |

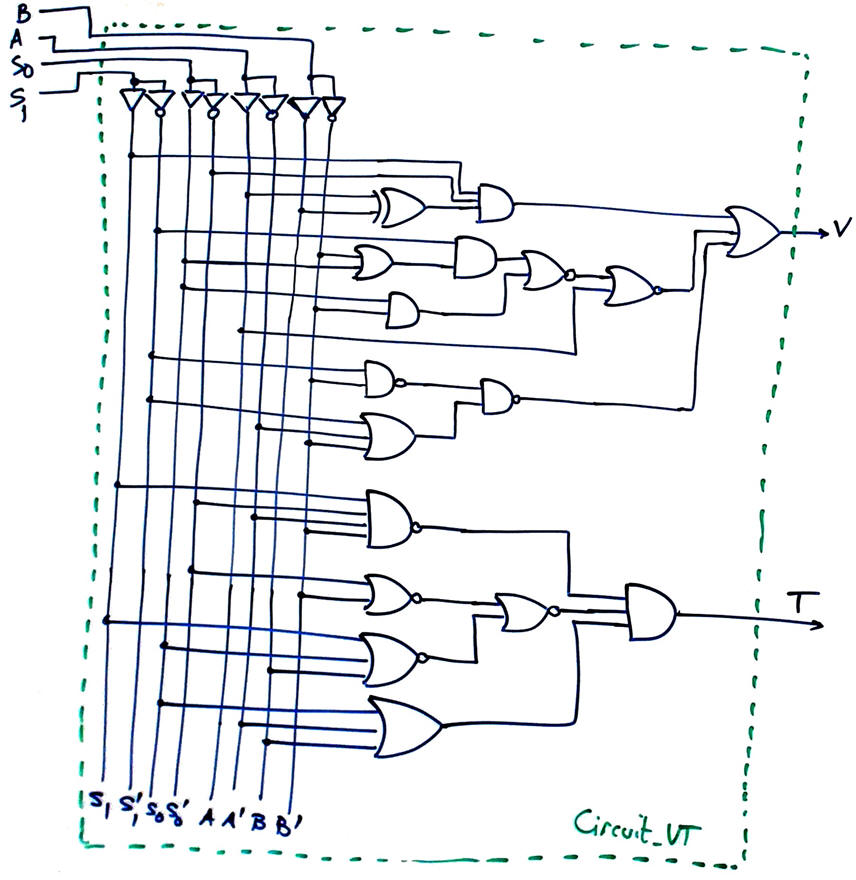

Analysing Circuit_VT |

|||

|

|

|||||

1. Specifications

Using our analysis method I in CSD (L1.3) (Boolean algebra) find the circuit's symbol and truth table of the algebraic expression represented in Fig. 1. Name it as Circuit_VT. Express the output as a sum of minterms and as a product of maxterms.

|

|

Fig. 1. Symbol and internal architecture of Circuit_VT. |

Project location to save your paper solution, class notes, pictures, theory, etc.:

C:\CSD\P1\Circuit_VT\algebra\(files)

Verify your results solving the same project using another analysis method.

Using our analysis method II (Proteus, electronic circuit simulations) find the circuit's symbol and truth table of the algebraic expression represented in Fig. 1. Project locations to save the complementary project for checking results:

C:\CSD\P1\Circuit_VT\proteus\(files)

Proteus components library options:

option #1.: LS-TTL

option #2.: CMOS

Verify your results solving the same project using another analysis method.

Using our analysis method III (VHDL EDA synthesis and simulation tools) find the circuit's symbol and truth table of the algebraic expression represented in Fig. 1. Project locations to save the complementary project for checking results:

C:\CSD\P1\Circuit_VT\VHDL\(files)

Target chip options:

option #1.: MAX II

option #2.: MAX 10

option #3.: Cyclone IV

Verify your results solving the same project using another analysis method.

Using our analysis method IV (WolframAlpha, computer numerical engine) find the circuit's symbol and truth table of the algebraic expression represented in Fig. 1. Project locations to save the complementary project for checking results:

C:\CSD\P1\Circuit_VT\wolfram\(files)

Verify your results solving the same project using another analysis method.