|

|

||

|

|

Binary radix-2 synchronous up/down counter modulo 12 using plan X |

|

|

|

||

FSM application enumerating states

1. Specifications

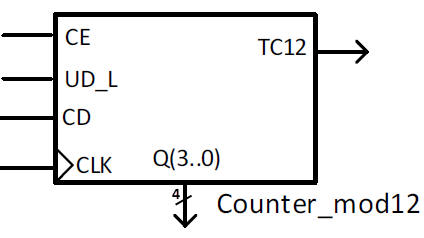

Design the synchronous Counter_mod12 represented in Fig. 1 using plan X.

|

|

| Fig 1. Symbol and function table. |

|

|

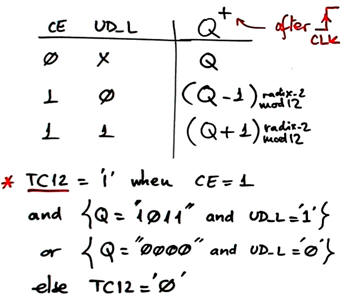

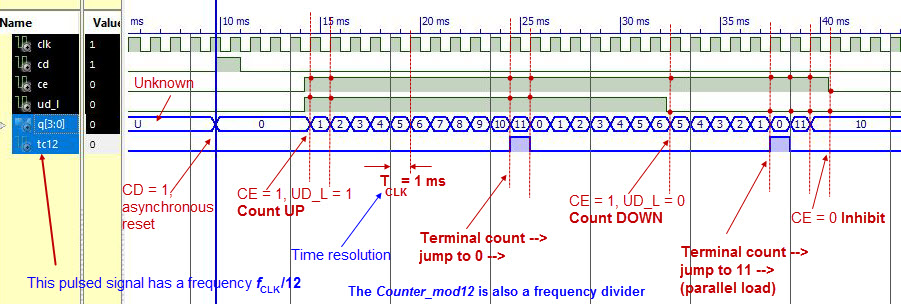

Fig 2. Example of timing diagram. |

The aim is to compare its design and architecture with alternative designs when implementing the same circuit using plan Y and plan C2 proposed at Lab7.

|

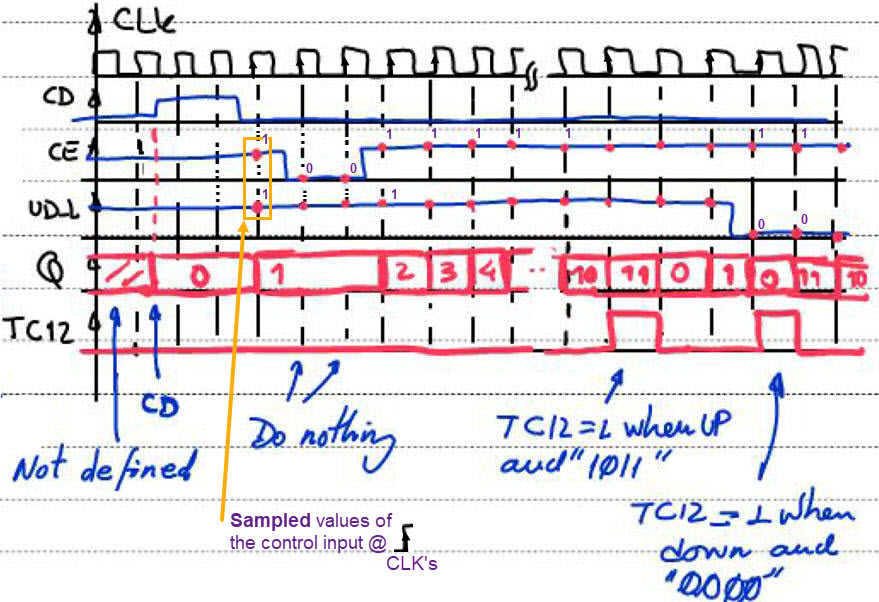

Fig. 3. State diagram representing the 36 state transitions and outputs. |

2. Planning

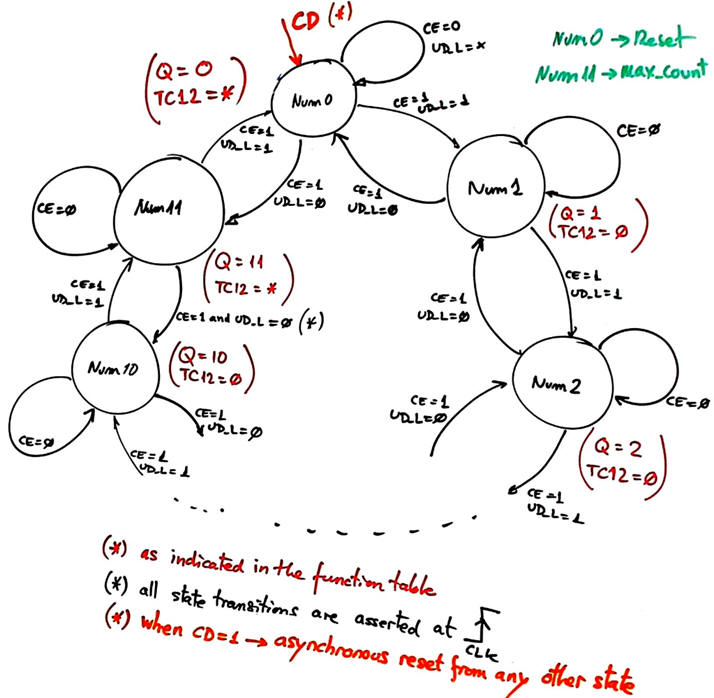

Plan X: FSM strategy as in P6 (naming all the states and State_type signals). This approach is possible because it is a sequential circuit with only a few states and a few state transitions that can be enumerated easily as with other FSM.

|

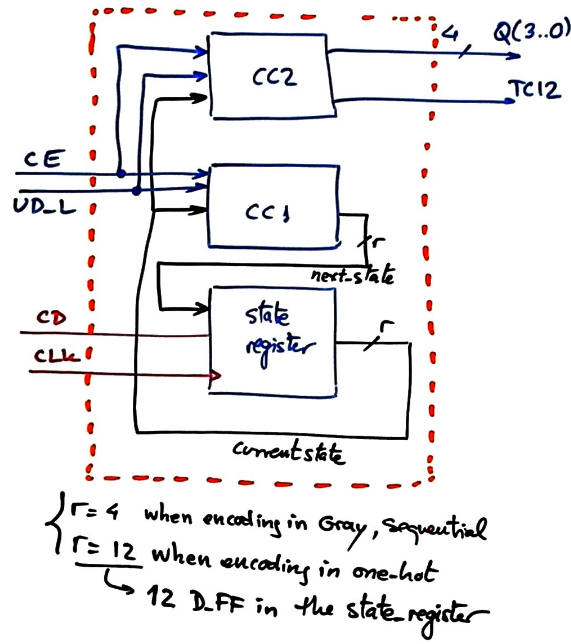

Fig. 4. FSM to implement the Counter_mod12 using plan X. |

We will follow the procedure for designing FSM.

Project location:

C:\CSD\P7\Counter_mod12X\Counter_mod12.vhd, etc.

3. Development

Some example of files for developing the circuits:

To obtain the Counter_mod12.vhd file copy and adapt for example the Counter_BCD_1digit.vhd.

|

Fig. 5. RTL view |

|

Fig. 6. State diagram interpreted by Quartus Prime, encoded in one-hot (12 D_FF are required). |

|

Fig. 7. Technology view schematic for a MAX II Intel CPLD. |

4. Testing (does the machine that we have invented work as expected?)

Start the test bench template and add the CLK and inputs activity translating the timing diagram. Make all the timing relative to the CLK_Period constant.

|

Fig. 8. Testbench schematic fixture. |

This is an example VHDL file translation from which you can copy the CLK_Period constant, and also the stimulus and CLK processes Counter_mod12_tb.vhd. You can use the same testbench that was written for the other plan Y and plan C2.

Functional simulation. Run the EDA VHDL tool and demonstrate how the circuit works adding comments to the printed sheet of paper containing the waveforms. Your system may works like the timing diagram discussed in class.

|

Fig 9. Example of a functional simulation of the counter module 12. |

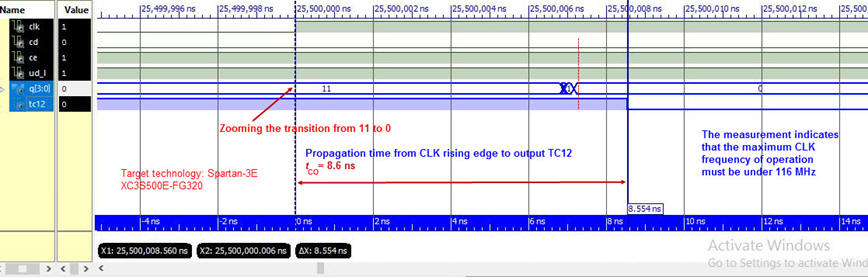

5. Testing (gate-level, timing analyser) for measuring propagation times and speed

Run the gate-level simulation of the project and measure the maximum frequency of operation. It is worth to know exactly which is the maxim CLK frequency for a given target CPLD or FPGA chip.

|

| Fig 10. Example of a gate-level simulation of the counter modulo 12 used to measure the parameter tCO in a given CLK transition. |

Timing analyser spreadsheet to measure tCO.

6. Report

Project report starting with the template sheets of paper, scanned figures, file listings, docx , pptx, or any other resources.

7. Prototyping

Use training boards and perform laboratory measurements to verify how the circuit works.