|

|

|||||

Chapter 2 problems |

- D2.16 - |

Electronic scale (FPGA-VHDL) |

|||

|

|

|||||

1. Specifications

We aim to design a BCD counter for a commercial mini digital pocket scale (Chip1 in Fig.1). The scale has to range up to 500 g and is equipped with a high accuracy load cell sensor with 0.01 g sensitivity. The maximum weight before overflow is 499.99 g and thus a Counter_BCD_mod50k is required (decimal point position has no effect on counting).

The same project designed programming a μC is in D3.16.

|

|

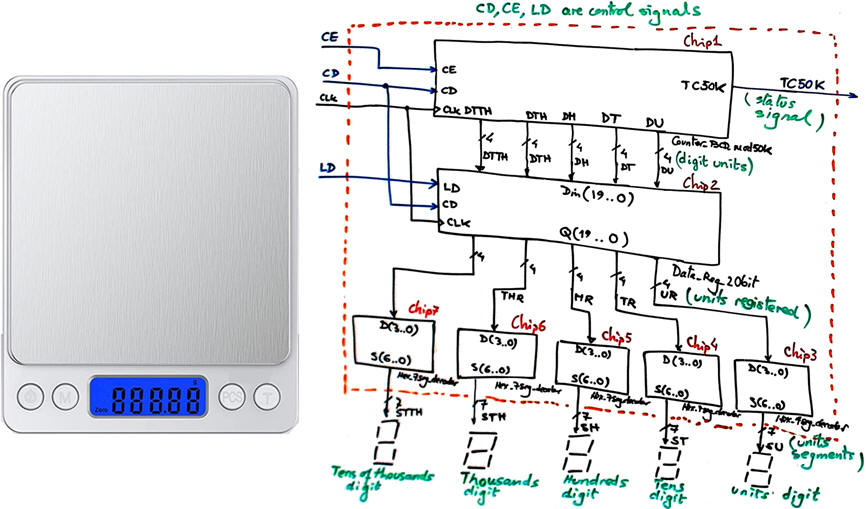

Fig 1. Electronic digital scale and its datapath for measuring mass with 0.01 g resolution. |

Find information on how the internal circuit of the scale may be conceived. For instance, it may contain a strain gauge load cell sensor in Wheatstone bridge configuration, signal conditioner (instrumentation amplifier), voltage reference circuit, dual-slope integrating analogue to digital converter (operational amplifiers, comparator, FSM and a datapath like the one represented in Fig.1 which includes Counter_BCD_mod50k, Data_reg20bit and Hex_7seg_decoder) and 7-segment displays.

Organise the design of the Counter_BCD_mod50k using plan C2 and chaining and truncation techniques based on our universal component Counter_mod16.

Optional. You can attain the full design of the scale electronics.

-Firstly, completing the dedicated processor. The aim of the FSM is to control dual-slope integrating analogue to digital conversion.

- Secondly, the analogue circuit around the sensor and its signal conditioner, for instance obtaining a full scale voltage of 3.3 V when applying 500 g.