#### Problem 1

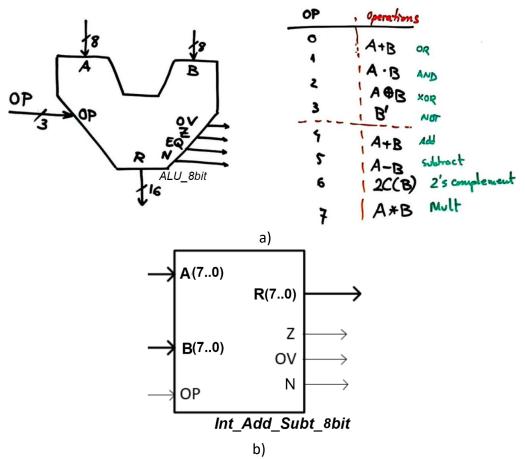

For the *ALU\_8bit* shown in Fig. 1a.

Indicate the range of the integer operands and results for the arithmetic operations in 2C. Complete the eight operations in binary for the following operands indicating as well the flag values when they care (check your results in decimal when necessary). Use a coloured square to indicate the position and value of the sign bit for arithmetic operations:

A = "10111011"; B = "01001001"

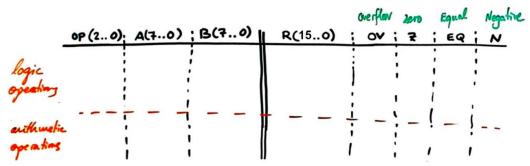

- Propose and explain the general architecture of the ALU designed internally using plan C2. Discuss using a timing diagram, which may be its maximum theoretical operational speed in Mops (millions of operations per second) if implemented using LS-TTL chips.

- 3. The ALU contains several chips and logic circuits; one of them is the chip Int\_Add\_Subt\_8bit, as shown in Fig. 1b, to perform additions and subtractions of 8-bit integer numbers in 2C. Draw a sketch plan C2 for this component. How many VHDL files will include this component?

- **4.** Another component that we can find in the ALU is the *Adder\_1bit*. Design it in plan C2 using the method of multiplexers (MoM) with *MUX\_2*. Apply some vectors to check that your circuit works as expected.

Fig. 1. a) 8-bit arithmetic and logic unit; b) one of *ALU\_8bit* internal components used for performing the arithmetic operations 4, 5 and 6.

(4p)

(3p)

## Problem 2

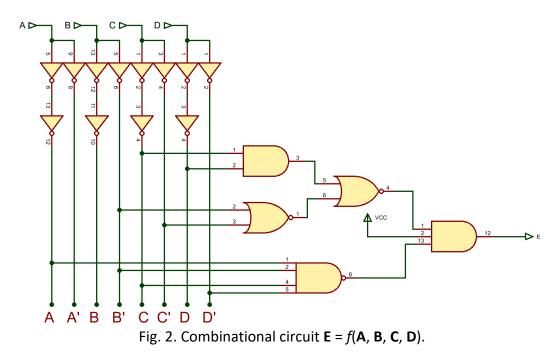

- Analyse the *Circuit\_E* in Fig. 2 using method I to obtain its truth table E = f(A, B, C, D). Firstly, explain your plan and the concepts and procedures involved in the deduction.

- 2. What is maximum frequency of the generator  $f_{MAX}$  that we can use to drive an input? Calculate the power consumption when the circuit is running at such frequency. Calculate both parameters for implementations using (a) CMOS gates and (b) TTL\_LS.

- 5. Invent the truth table using a plan A based on only NOR2 gates.

#### Problem 3

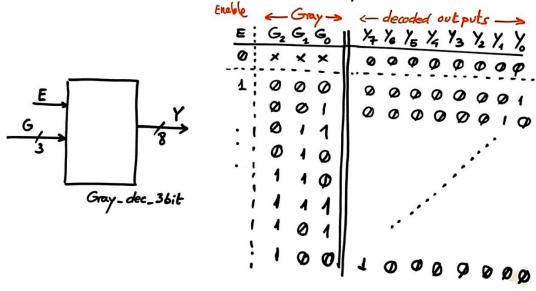

The circuit in Fig. 3 is a 3-bit Gray decoder.

- 1. Complete the truth table. Obtain the outputs equations.

- 2. Connect LED active-high at each circuit output ( $V_{AKQ}$  = 1.9 V). Calculate the limiting resistors to drive each LED with 800  $\mu$ A in the worst-case scenario using CMOS logic.

- **3.** Describe the schematic or flowchart to be able to translate the truth table into VHDL using plan B.

- 4. Plan and solve the circuit using the method of decoders (MoD). Apply some vectors to check that your circuit works as expected.

## Problem 4

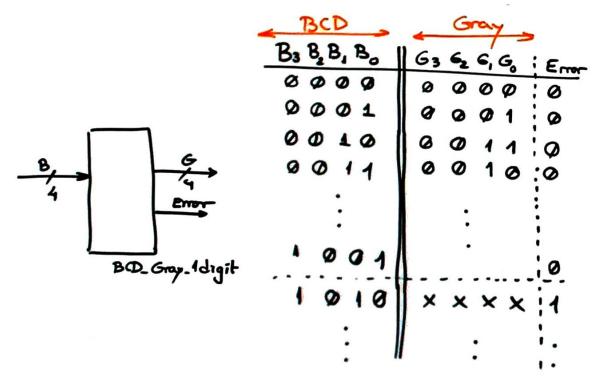

The circuit in Fig. 4 is a combinational circuit to convert from 1-digit BCD to Gray code.

- 1. Complete the truth table. Obtain the canonical equations for G<sub>2</sub> and G<sub>1</sub> indicating the terms of no interest as *don't care* values.

- If the circuit is solved completely using plan A, LS-TTL gates and simplified equations SoP or PoS from Minilog, calculate its propagation delay and maximum number of operations per second.

- **3.** Plan and solve the circuit using the method of decoders (MoD). Apply some vectors to check that your circuit works as expected.

- 4. Invent a *Dec\_4\_16* using only *Dec\_2\_4* and logic gates if necessary.

Fig. 4.

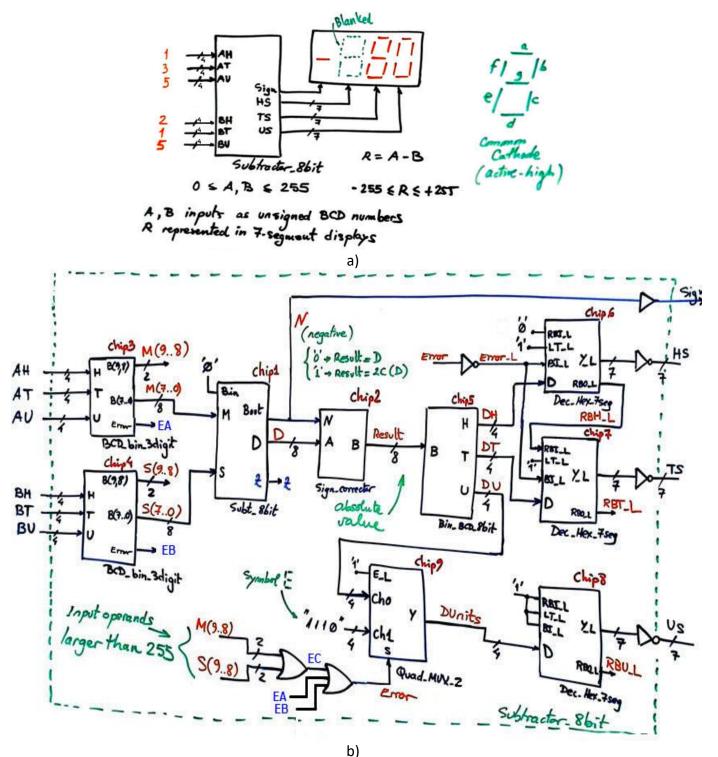

## Problem 5

Fig. 5. 8-bit subtractor and its proposed internal architecture.

- 1. Generate a timing diagram representing these operations: 135 215; 215 1B5; 155 32; 976 155.

- **2.** If we can automate a VHDL test-bench, and all the input vector signals last for *Min\_Pulse* = 3.4 μs, how long will it take to check all the truth table?

- **3.** Deduce all the outputs and internal signals while explaining the functionality of each component: Sign, HS, M, S, D, etc. for the following operation: 976 155.

- **4.** Explain what is the idea behind the chain RBO\_L  $\rightarrow$  RBI\_L implemented for several *Dec\_Hex\_7seg*.

(3p)

## (3p)

## Problem 6

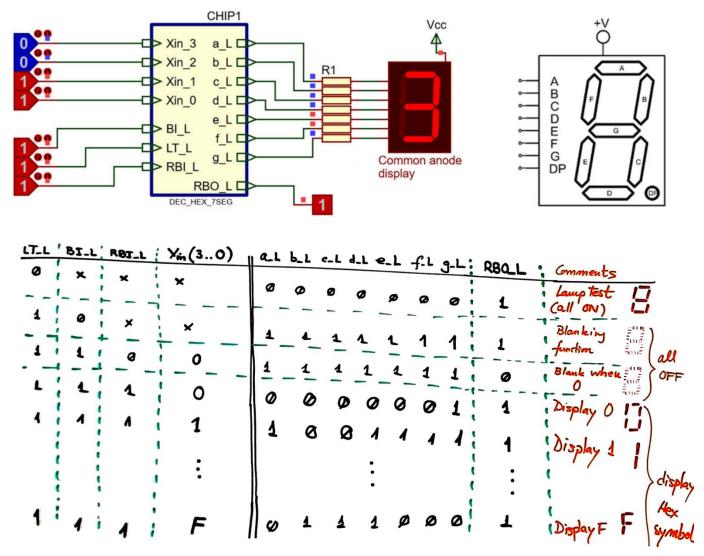

The decoder from hexadecimal to 7-segment *Dec\_Hex\_7seg* represented in Fig. 6 works as indicated in the truth table.

- **1.** Describe a flowchart to be able to translate the truth table in VHDL using plan B.

- 2. Complete the circuit's truth table. How many maxterms contains a\_L? How many logic gates will the circuit contain if solved using plan A and simpler equations SoP or PoS from Minilog or by truth table inspection? Which is power consumption of the circuit working at the maximum theoretical number of decoding operation per second if LS-TTL gates are used? Imagine all the circuit gates switching.

- 3. Calculate the limiting resistor R1 to drive the LED segments at  $V_{AKQ}$  = 2.1 V,  $I_{DQ}$  = 1.2 mA.

Fig. 6. Idea of the decoder *Dec\_Hex\_7seg* truth table used for driving active-low LED segments.

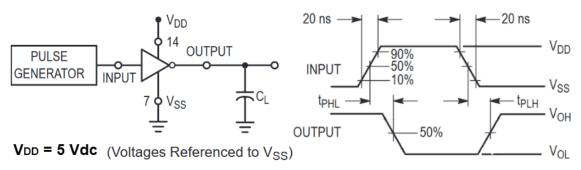

Annex. Fig. 7 shows the electrical characteristics of a single logic gate in classic CMOS

# $P_S + P_{dyn} = I_{\text{DD}Q} \cdot V_{\text{DD}} + V_{\text{DD}}^2 \cdot C_L \cdot f$

| MC14069UB                                                                                                                        | Symbol          |                                        |                      |                 |       |      |

|----------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------------------------------|----------------------|-----------------|-------|------|

|                                                                                                                                  |                 | -                                      | Min                  | Тур             | Мах   | Unit |

| Output Voltage V <sub>in</sub> = V <sub>DD</sub>                                                                                 | "0" Level       | V <sub>OL</sub>                        |                      | 0               | 0.05  | Vdc  |

| V <sub>in</sub> = 0                                                                                                              | "1" Level       | V <sub>OH</sub>                        | 4.95                 | 5.0             |       | Vdc  |

| Input Voltage<br>(V <sub>O</sub> = 4.5 Vdc)                                                                                      | "0" Level       | V <sub>IL</sub>                        | _                    | 2.25            | 1.0   | Vdc  |

| (V <sub>O</sub> = 0.5 Vdc)                                                                                                       | "1" Level       | V <sub>IH</sub>                        | 4.0                  | 2.75            | _     | Vdc  |

| Output Drive Current<br>(V <sub>OH</sub> = 2.5 Vdc)<br>(V <sub>OH</sub> = 4.6 Vdc)                                               | Source          | I <sub>OH</sub>                        | - 2.4<br>- 0.51      | - 4.2<br>- 0.88 | _     | mAdc |

| (V <sub>OL</sub> = 0.4 Vdc)                                                                                                      | Sink            | I <sub>OL</sub>                        | 0.51                 | 0.88            | —     | mAdc |

| Input Current                                                                                                                    |                 | l <sub>in</sub>                        | _                    | ±0.00001        | ± 0.1 | μAdc |

| Input Capacitance (Vin = 0                                                                                                       | C <sub>in</sub> | _                                      | 5.0                  | 7.5             | pF    |      |

| Quiescent Current (Pe                                                                                                            | r Gate)         | I <sub>DD</sub>                        | —                    | 0.084           | 42    | nAdc |

| Total Supply Current (C <sub>L</sub> = 50 pF)<br>(Dynamic plus Quiescent(Per Gate)                                               |                 | Ι <sub>Τ</sub>                         | I <sub>T</sub> = (0. | μAdc            |       |      |

| Propagation Delay Times<br>(C <sub>L</sub> = 50 pF)<br>t <sub>PLH</sub> , t <sub>PHL</sub> = (0.90 ns/pF) C <sub>L</sub> + 20 ns |                 | t <sub>PLH</sub> ,<br>t <sub>PHL</sub> | _                    | 65              | 125   | ns   |

Fig. 7. Characteristics of a logic gate in CMOS technology

Annex. Fig. 8 shows the characteristics of a single logic gate in LS-TTL technology.

# $P_S + P_{dyn} = I_{DDQ} \cdot V_{DD} + V_{DD}^2 \cdot C_L \cdot f$

| Symbo                                    | Parameter                                   |                                                | Μ                                             | Min Nom Max |        | ( L      | Inits |         |        |       |

|------------------------------------------|---------------------------------------------|------------------------------------------------|-----------------------------------------------|-------------|--------|----------|-------|---------|--------|-------|

| V <sub>CC</sub>                          | Supply Voltage                              |                                                | 4.                                            | 75          | 5 5.25 |          | 5     | V 74LS0 |        | S04   |

| V <sub>IH</sub> HIGH Level Input Voltage |                                             | 1                                              | 2                                             |             |        |          | V     |         |        |       |

| V <sub>IL</sub> LOW Level Input Voltage  |                                             |                                                |                                               |             | 0.8    |          | V     |         | ≫—     |       |

| I <sub>OH</sub>                          | HIGH Level Output Current                   |                                                |                                               |             |        | -0.4     | 1     | mA      | -      |       |

| I <sub>OL</sub>                          | LOW Level Output Current                    |                                                |                                               |             |        | 8        |       | mA      |        |       |

| Symbol                                   | Parameter                                   |                                                | Conditions                                    |             |        |          | Min   | Тур     | Мах    | Units |

| VI                                       | Input Clamp Voltage                         | $V_{\rm CC} = Min, I_{\rm I} = -18 \text{ mA}$ |                                               |             |        |          |       | -1.5    | V      |       |

| V <sub>OH</sub>                          | HGH Level                                   |                                                | V <sub>CC</sub> = Min, I <sub>OH</sub> = Max, |             |        |          | 2.7   | 3.4     |        | V     |

|                                          | Output Voltage                              | V <sub>IL</sub> = Max                          |                                               |             |        |          |       |         | v      |       |

| V <sub>OL</sub>                          | V <sub>OL</sub> LOW Level<br>Output Voltage |                                                | $V_{CC} = Min, I_{OL} = Max,$                 |             |        |          |       | 0.35    | 0.5    |       |

|                                          |                                             |                                                | $V_{IH} = Min$                                |             |        |          |       |         |        | V     |

|                                          |                                             |                                                | $I_{OL} = 4 \text{ mA}, V_{CC} = \text{Min}$  |             |        |          |       | 0.25    | 0.4    |       |

| lj –                                     | nput Current @ Max                          |                                                | $V_{CC} = Max, V_I = 7V$                      |             |        |          |       |         | 0.1    | mA    |

|                                          | Input Voltage                               |                                                |                                               |             |        |          |       |         |        |       |

|                                          | HIGH Level Input Current                    |                                                | $V_{CC} = Max, V_I = 2.7V$                    |             |        |          |       |         | 20     | μA    |

|                                          | _OW Level Input Current                     |                                                | $V_{CC} = Max, V_I = 0.4V$                    |             |        |          |       |         | -0.36  | mA    |

| l <sub>OS</sub>                          | Short Circuit Output Current                |                                                | V <sub>CC</sub> = M <b>a</b> x                |             |        |          | -20   |         | -100   | mA    |

| I <sub>CCH</sub>                         | Supply Current with Outputs HIGH            |                                                | V <sub>CC</sub> = Max                         |             |        |          |       | 1.2     | 2.4    | mA    |

| I <sub>CCL</sub>                         | Supply Current with Outputs LOW             |                                                | V <sub>CC</sub> = M <b>a</b> x                |             |        |          |       | 3.6     | 6.6    | mA    |

| Symbol                                   | Parameter C <sub>L</sub> = 50 pF            | Min                                            | Max                                           | Units       | •      |          |       |         | Vcc    | ľ     |

| t <sub>PLH</sub>                         | Propagation Delay Time                      | 4                                              | 15                                            | ne          |        | PULSE    |       |         |        |       |

|                                          | LOW-to-HIGH Level Output                    | 4                                              | 15                                            | ns          | G      | ENERATOR |       | IPUT    | $\sim$ |       |

| t <sub>PHL</sub>                         | Propagation Delay Time                      | 4                                              | 15                                            | ns          | -      |          |       | 7       | GND    | Ť°    |

|                                          | HIGH-to-LOW Level Output                    |                                                | 15                                            |             |        |          |       |         | ÷      | ÷     |

Fig. 8. Characteristics of a logic gate in LS-TTL technology

**NOTE** for all problems and questions: draw circuits, sketches or diagrams, explain as clearly as possible what you do and how you are inventing circuits or processing calculations as you did when you wrote your project reports. Justify your results.