## CSD laboratory P\_Ch3: µC-based programmable timer

I. Specifications

The aim of this project is to invent a digital programmable timer. Features:

- Programmable 16-bit pulse count (PC)

- 1 kHz external **CLK** reference (T<sub>CLK</sub> = 1ms) (or equivalent internal TMR0 time base in design phase #3)

- End of timing period pulse (ETP) flag (width =  $50 \cdot T_{CLK}$ , 50 ms)

- Active-high interrupt-driven TRG pulse

- Asynchronous reset

- Timed output signal **Timer\_out** = PC · T<sub>CLK</sub> (maximum timing period = 65535 ms)

- MICROCHIP PIC18F4520 microcontroller chip

- Dedicated processor architecture for adapting concepts and P\_Ch2 planning

- LCD display for representing ASCII messages indicating timer operation

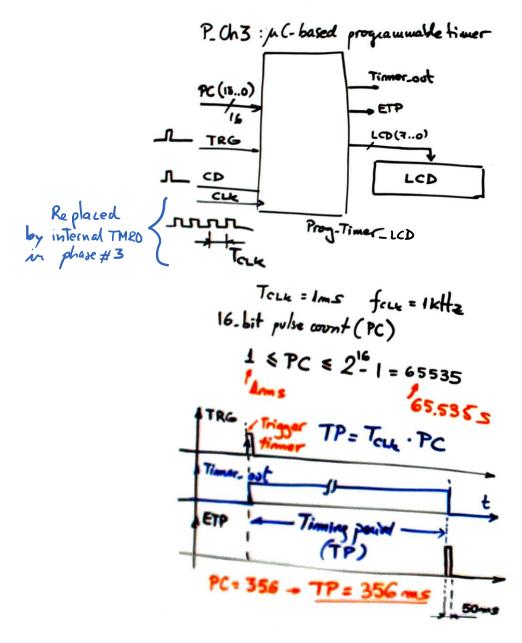

Fig. 1 shows the chip symbol at design phase #2 and an example of typical waveforms.

Fig. 1 Symbol and typical waveforms in design phase #2. A **TRG** pulse, for instance clicking a button, triggers the timing period. Once the timing period (**TP**) ends, a single pulse of  $50 \cdot T_{CLK}$  duration is generated to indicate that the device is idle and can be used again for programing any other timing interval. This device is non-retriggerable, meaning that other trigger pulses are ignored while the device is on duty.

One of the goals of the project is to compare features and performance with P\_Ch2.

Extra features may be added optionally introducing new design phases once this basic project is complete and operates correctly:

- Retriggerable switch to be able to generate arbitrary large timing periods.

- TMR2 instead of TMR0 to obtain higher precision.

- Alarm sound to indicate end of timing period.

- Serial (RS232) or keypad pulse count programing, etc.

## II. Planning

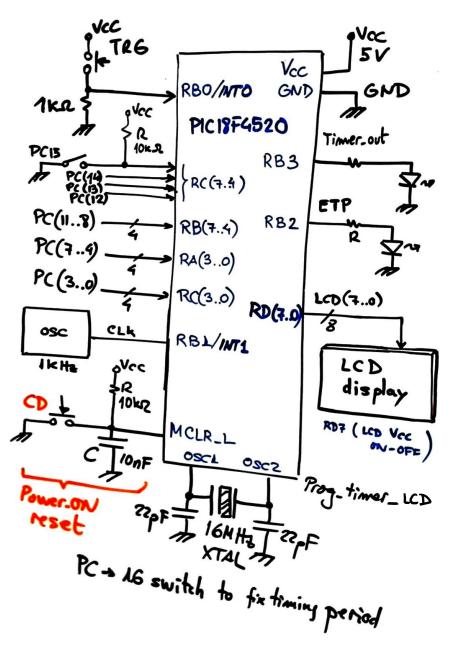

To make it simple and reasonable in the given time constraints and to be able to embed its design within CSD course timeline, we propose adapting to uC the architecture designed in P\_Ch2. Fig. 2 shows the proposed hardware circuit for design phase #2. Additional resources, diagrams, sections of C code and support will be given to speed up the design.

Fig. 2 Hardware circuit for the design phase #2 that includes the LCD display.

Subprojects planning related to lab sessions:

- Lab 9: SP3\_1 (November 30<sup>th</sup>) is used to comprehend how basic I/O works. *init system(), read\_inputs(), write\_outputs()*. We will design a combinational circuit such *Comp\_4bit* (Work assessment December 14<sup>th</sup>).

- Lab 10: SP3\_2 (December 14<sup>th</sup>), design phase #1, *Prog\_Timer*, is used to implement the FSM and counter and datapath (Work assessment December 21<sup>st</sup>).

- Lab 11: SP3\_3 (December 21<sup>st</sup>), design phase #2, *Prog\_Timer\_LCD*, is used to add an LCD for printing messages (and even numerical data).

The complete design P\_Ch3 will include the replacement of the external CLK by the internal peripheral TMRO (design phase #3), *Prog\_Timer\_LCD\_TMRO*, and the complete report and video presentation. Compare features with the programmable timer designed in P\_Ch2. (P\_Ch3 due date: January 11<sup>th</sup> report + video submissions).

## III. Development & Test

The development and test of P\_Ch3 implies solving each subproject beforehand and the final programing in C language of the complete system *Prog\_Timer\_LCD\_TMR0*.

Testing is interactive using Proteus while programming and debugging C code step by step.

VERY IMPORTANT NOTE: Solving these laboratory assignments requires studying ahead and in group in detail similar examples and tutorials in CSD <u>digsys</u>.

## Marking grids:

Work assessments (4p.):

| SP3 1 | SP3 2 | P Ch3 (Video) |

|-------|-------|---------------|

| 14-12 | 21-12 | = , ,         |

| 14-12 | 21-12 | 11-01         |

| 1p    | 1p    | 2p            |

Handwritten report (6p.):

| SP3_1 | SP3_2 | SP3_3 | P_Ch3 |

|-------|-------|-------|-------|

| 1p    | 1p    | 2р    | 2р    |