## SP1.4 Designing a standard arithmetic circuit type 74LS85 using hierarchical structures and completing P\_Ch1

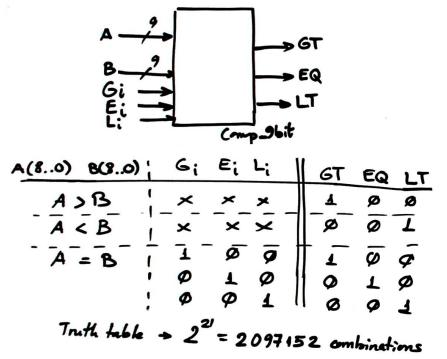

I. Specifications of Comp\_9bit

The aim of this preparatory laboratory assignment is to invent a 9-bit radix-2 comparator (*Comp\_9bit*) using hierarchical structures based on components *Comp\_1bit*. In this way, you can practise how to develop plan C2 and complete this component to be used in P\_Ch1 as Chip2.

Fig. 1 Comp\_9bit symbol.

II. Plan C2 using components and signals.

Draw a schematic plan C2 for the *Comp\_9bit* using *Comp\_1bit* components and logic if necessary.

III. Development. Synthesis.

Translate to VHDL the plan and write the *Comp\_9bit.vhd*. Run a synthesis project and examine RTL and technology schematics.

Target chip: MAX II EPM2210F324C3 or Cyclone IV EP4CE115F29C7N

IV. Test and verification using VHDL testbench.

Organise a VHDL testbench *Comp\_9bit\_tb.vhd*. Run a ModelSim functional simulation and examine results from logic analyser to determine whether the circuit works as expected.

## Completing P\_Ch1

## I. Specifications of Arith\_9bit

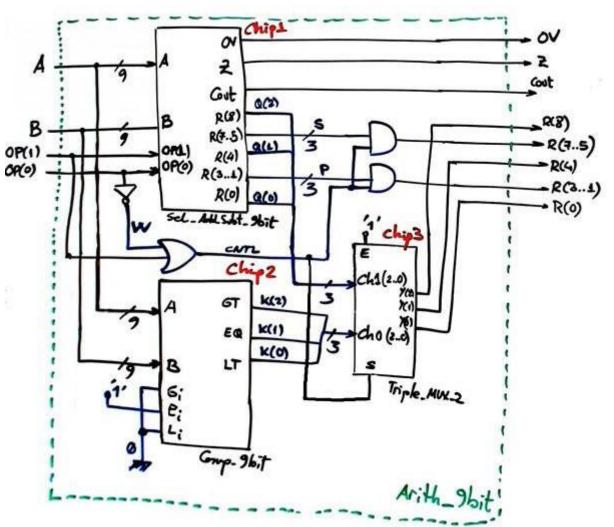

Complete P\_Ch1 using Chip1, Chip2 and Chip3 and all their internal components in Fig. 2 reporting all the previous subprojects and recording a video explaining how such hierarchical circuit is developed and tested.

II. Planning

The schematic plan of the P\_Ch1 is already represented in Fig. 2.

Fig. 2 Top architecture for P\_Ch1 arithmetic unit. How many VHDL files contains this project?

III. Development. Synthesis.

Translate to VHDL the plan in Fig. 2 and write the *Arith\_9bit.vhd*. Run a synthesis project and examine RTL and technology schematics.

Target chip: MAX II EPM2210F324C3 or Cyclone IV EP4CE115F29C7N

IV. Test and verification using VHDL testbench.

Organise a VHDL testbench *Arith\_9bit\_tb.vhd*. Run a ModelSim functional simulation and examine results from logic analyser to determine whether the circuit works as expected.