## SP1.2 Analysis of a circuit based on gates using VHDL (analysis method IV)

The aim of this laboratory exercise is to analyse Circuit\_SP1\_1 to obtain its truth table<sup>i</sup> using EDA tools.

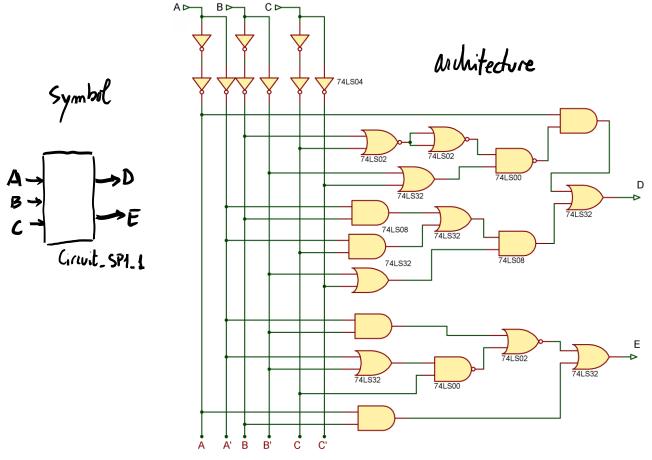

Fig. 1 Circuit *Circuit\_SP1\_1* to be analysed.

1. Deduce circuit general equations. D = f(A, B, C); E = f(A, B, C).

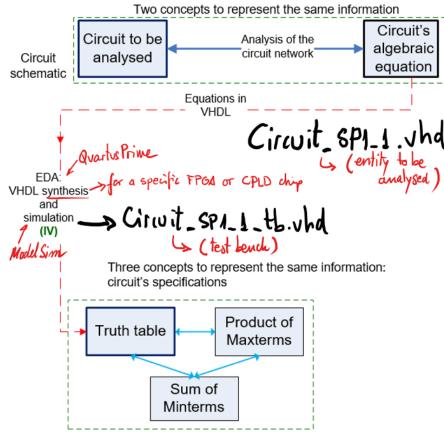

Fig. 3 Analysis method IV.

- 2. Write them in VHDL *Circuit\_SP1\_1.vhd* using an example file from the analysis section in this <u>tutorial</u>.

- 3. Start a Quartus Prime project for a target chip 10M50DAF484C7G from Intel.

- 4. Synthesise and view RTL and technologies schematics.

- Generate a skeleton of a testbench and add all the truth table input vectors.

Observe how this step is solved in this similar <u>tutorial</u>: *Circuit\_SP1\_1\_tb.vhd*

- 6. Start a ModelSim Intel Starter Edition project and simulate the testbench and the unit under test.

- 7. Using the wave logic analyser deduce the circuit truth table and compare results with other methods.

<sup>&</sup>lt;sup>i</sup> This circuit is simply another implementation of the <u>Adder\_1bit</u> solved in P3 by means of different plans.