# SP3\_2 Implementing the control unit (FSM) and completing design phase #1

### I. Specifications

The aim of this preparatory laboratory assignment is to analyse the given circuit for the programmable timer and complete hardware and software.

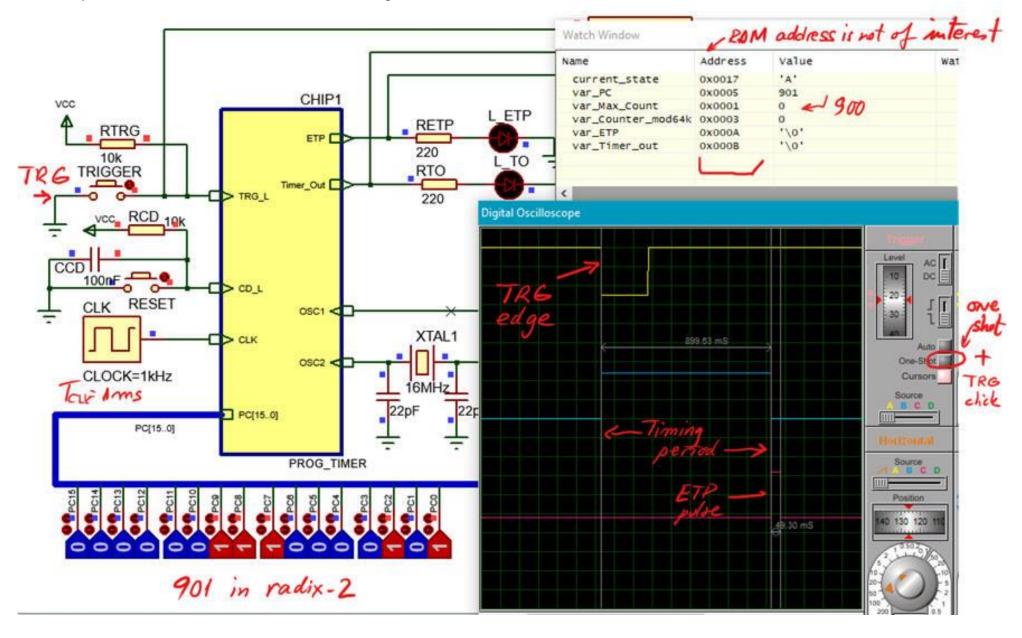

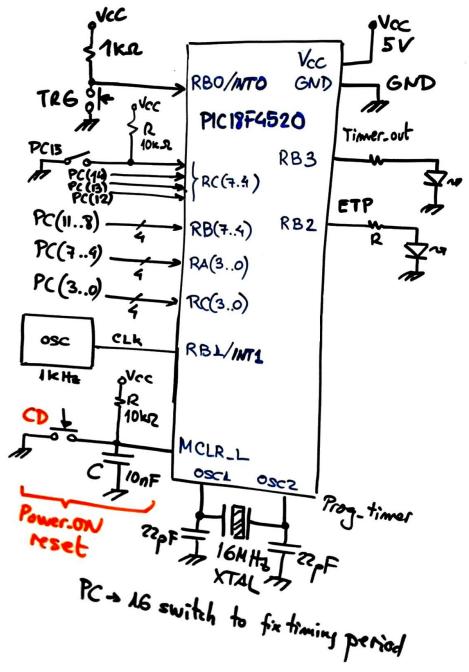

Fig. 1 Programmable timer.

#### II. Planning.

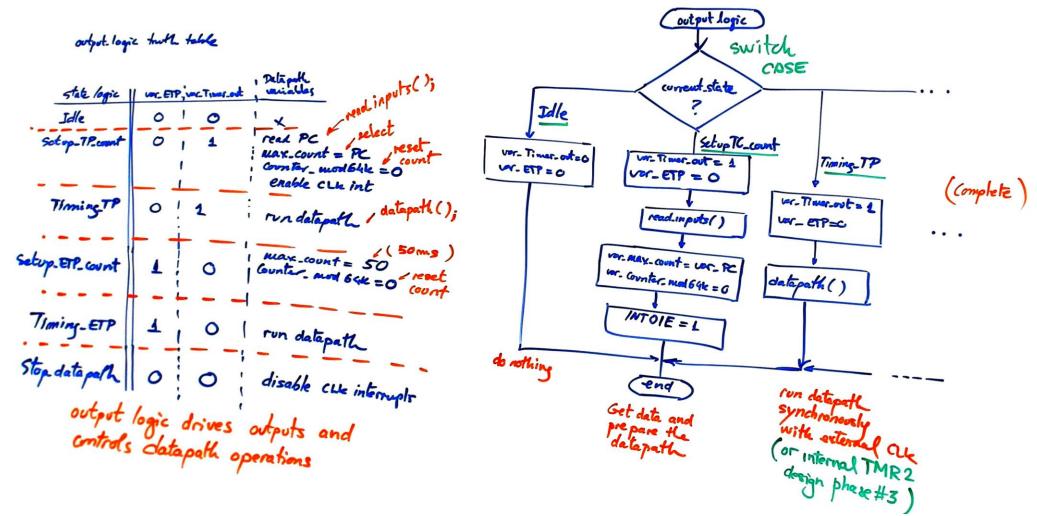

Study all the project sections and draw the truth table and its equivalent flowchart for state\_logic()

- III. Development, debugging

- IV. Test

Write the *state\_logic()* C code, start a new MPLABX project *Prog\_Timer\_prj*, compile and run and verify in Proteus that your circuit work as expected.

## V. Measurements and questions

- Measure the circuit precision in timing periods when for instance PC = 3; PC = 3000

- Measure using breakpoints how long does it takes to execute the main loop.

- Measure how long does it takes to execute ISR()

- What happens if OSC crystal is replaced by 4 MHz?

- How to make TRG sensitive to rising edges?

#### **Annex**

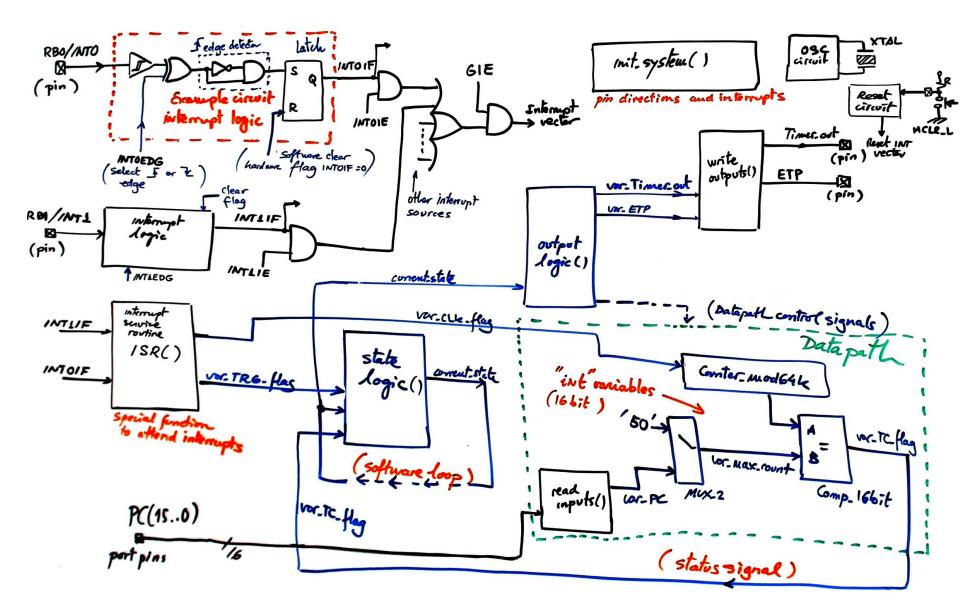

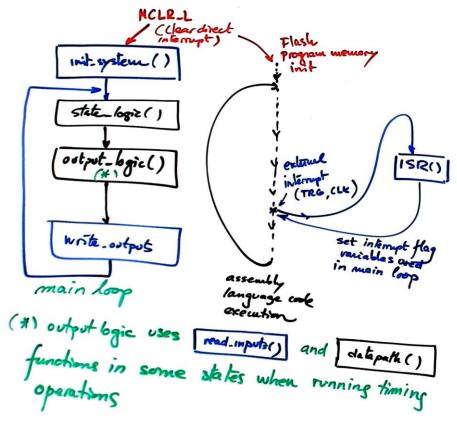

Paper work on diagrams, sketches, flowcharts and materials for studying the project in detail and completing it. Example of hardware-software diagram:

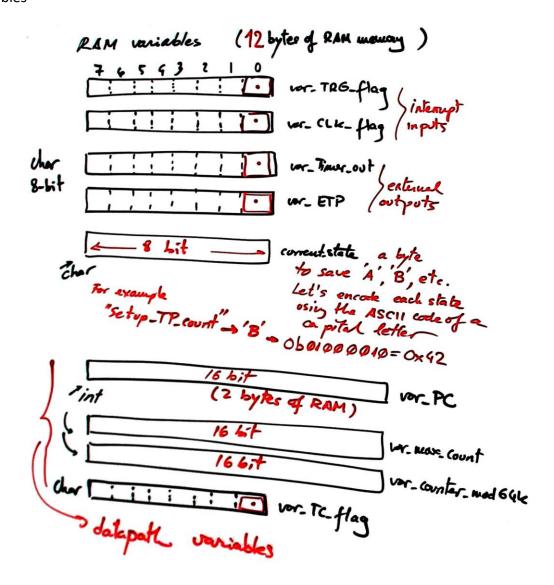

**RAM** variables

Initialising the system

/ init. system () discussion (complete the discussion)

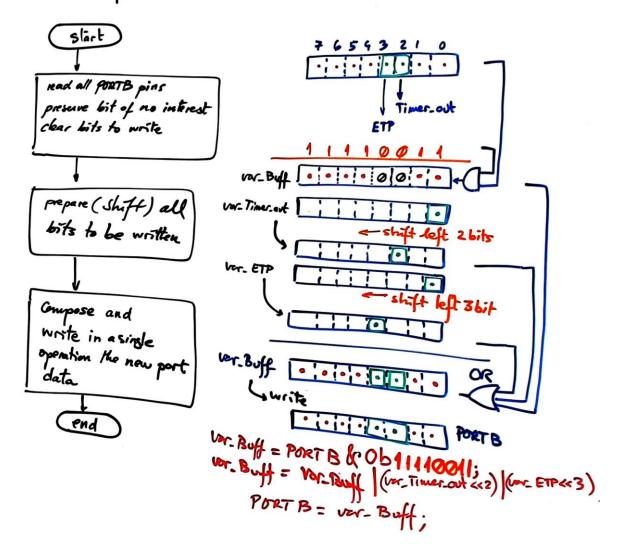

# write.outputs() discussion

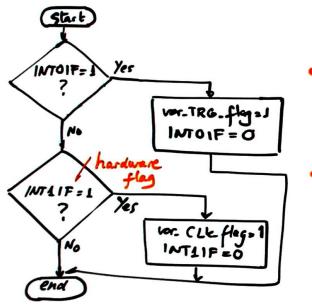

Interrupt service routine

- · Clear hardware flag means that the system can be interrupted again by the same mechanism

- · Softwere flag variables will be used in main programme and cleared once used

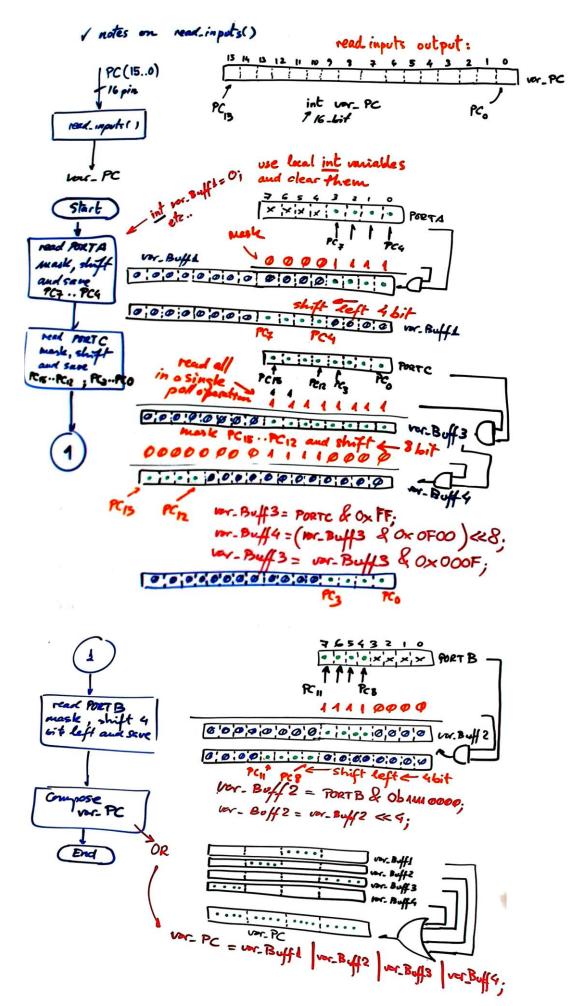

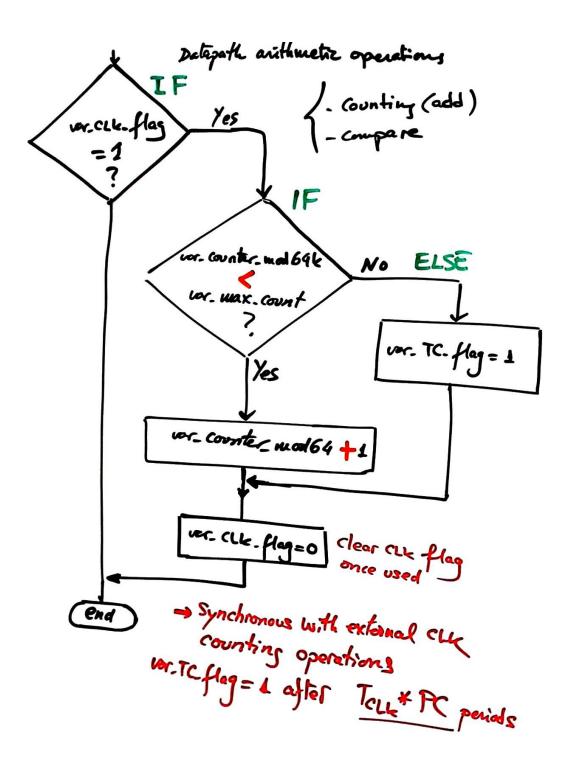

Counter structure in the datapath, a software/algorithmic/behavioural translation of the datapath operating resources in the hardware-software diagram.

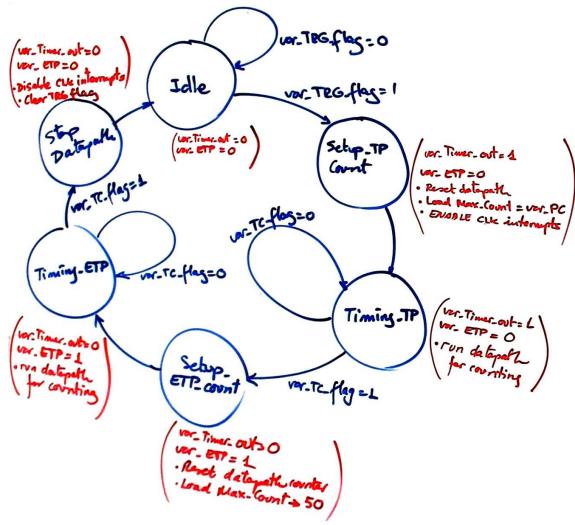

State logic truth table and flowchart

Oscilloscope measurements and watch window for debug.