## SP2\_4 Designing datapath components and assembling the programmable timer

Design the datapath components and complete, develop and test the programmable timer in Fig. 1.

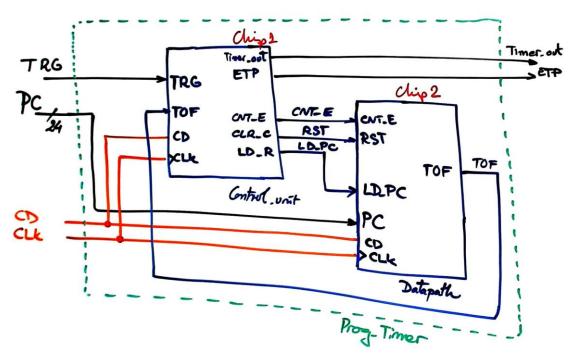

Fig. 1. Symbol

Follow the sequence below to complete this project:

- 1. Implement Comp\_24bit from SP1\_4 or SP2\_1.

- 2. Use the tutorial on <u>plan Y large counters</u> to implement *Counter\_mod16M*.

- 3. Use the tutorial on <u>data registers</u> to implement *Data\_reg\_24bit* (or use again the same *Counter\_mod16M* as a data register.

- 4. Build the *Datapath* component and synthesise it.

- 5. Combine the *Datapath* and the FSM in <u>SP2\_3</u> to implement the *Prog\_Timer*. Synthesise it and test the project using both functional and gate-level simulations triggering several times the device for different pulse count (PC) values.

Fig. 2. Programmable timer designed with an internal architecture as a dedicated processor.