## CSD laboratory P\_Ch1: 9-bit arithmetic unit

## Subproject SP1.1 Analysis of Circuit\_SP1\_1

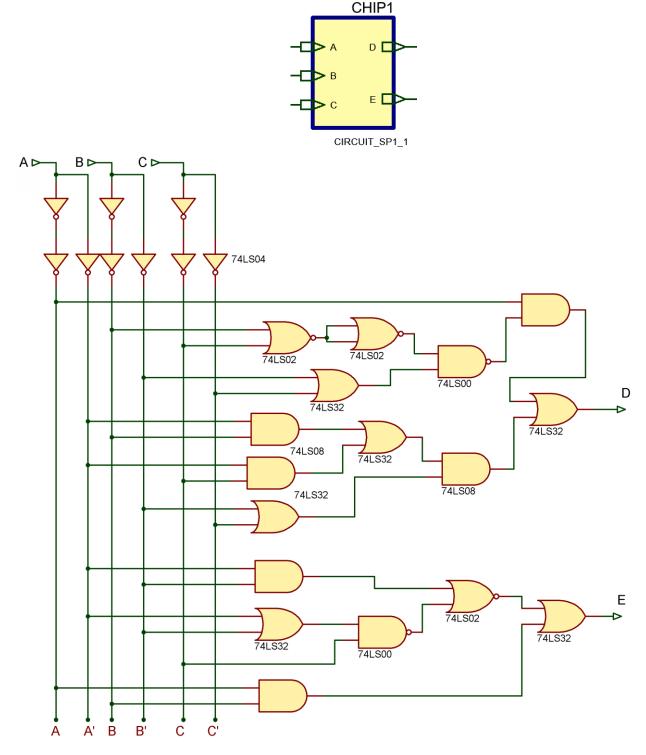

The aim of this laboratory exercise is to analyse  $Circuit\_SP1\_1$  in Fig. 1 to deduce its truth table using up to two methods from this <u>concept map</u><sup>1</sup>: D = f(A, B, C); E = f(A, B, C)

- Method 1: Using Proteus and simulation models from the LS-TTL (Low-power Schottky Transistor–transistor logic) components library.

- Method 2: Using WolframAlpha

Fig. 1 Circuit\_SP1\_1 composed of a network of logic gates.

<sup>&</sup>lt;sup>1</sup> Method 3 can be used as an additional classroom exercise, and method 4 will be the subject of next SP1\_2.