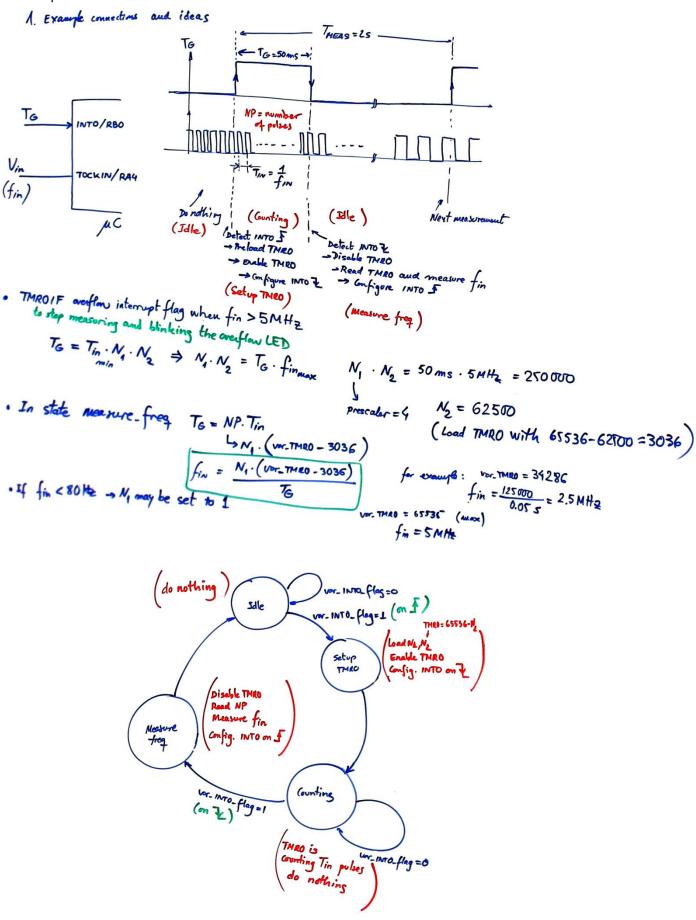

1. Frequency meter basic diagram. Example project <u>1-digit BCD counter with LCD and TMR0</u> on counting external pulses.

2. <u>P11</u> on using the LCD as a design phase #2. Two design steps are possible: (1) printing simple static ASCII text, (2) printing numerical dynamic data

How to use <u>TMR2</u> as timer counting internal pulses from the time base T<sub>osc</sub> derived from the microcontroller oscillator.

TMR2 hardware can count up to  $16 \cdot 256 \cdot 16 = 65536$  pulses before overflow and generate interrupt TMR2IF.

Because F<sub>osc</sub> = 12 MHz, we need another post-scaler to reach TG = 50 ms;

For example N1 = 16; N2 = 125; N3 = 5 (Interrupts every 3.33 ms); N4 = 15 (*var\_soft\_postscaler\_N4* char type). In this way we can replace *var\_INTO\_flag* by for instance *var\_COUNT\_flag* to enable TMR0 counter (after  $T_G$  = 50 ms), and also to disable it after the same timing period.

If the external signal  $T_G$  has to be replaced by timings from TMR2, the 2 s measurement period ( $T_{MEAS}$ ) can also be obtained counting TMR2IF interrupts:  $T_{MEAS} = 2 s = 40 \cdot T_G$

This frequency meter is a good example project for developing and testing because the three design phases are specified.

- 4. How to poll switches is explained in this lecture <u>L9.3</u>. This is the task assigned to the function *read\_inputs()* executed in the main loop.

- 5. How to write output pins is explained in this lecture <u>L9.4</u>. This is the task assigned to the function *write\_outputs()* executed in the main loop.

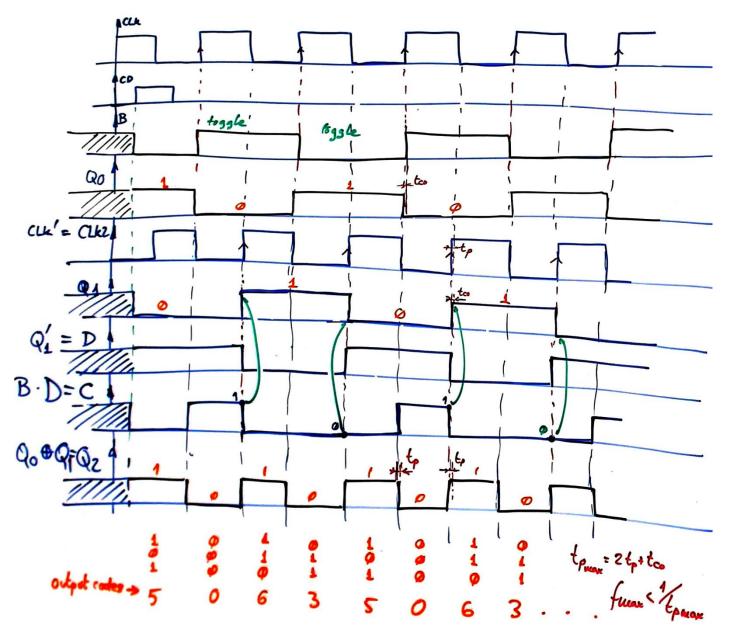

- 6. The BCD code, why is different from binary radix-2. Symbol. Example timing diagram. Truncating counters and expanding counters are concepts developed in this lecture <u>L7.3</u>, and proposed for instance in the highlighted project <u>P7</u> on the *Hour\_counter* (or up/down counter BCD modulo 24).

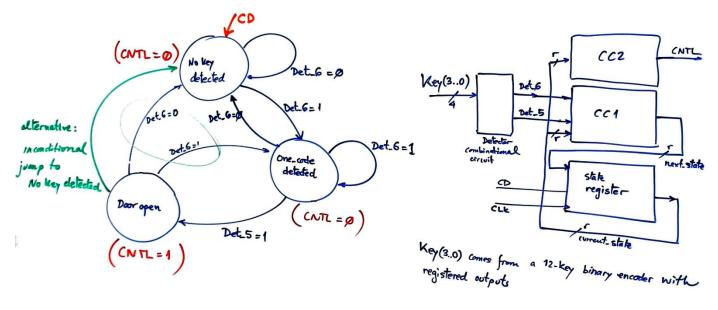

- 7. Two possible alternative designs. Examining the timing diagram, we see that the Key(3..0) vector is generated from a 12-key binary encoder with registered outputs that keep the last key pressed down (for example in this <u>D2.15</u>).

A *hardwired* standard <u>P6</u> FSM application. Changing the secret code represents resynthesizing the full project. The state diagram is similar to the <u>D2.4</u> pattern generator example.

A standard <u>P8</u> dedicated processors including a datapath for solving comparison applications. The secret code is *information* easily saved and modified using switches. In the datapath two chained 4-bit data registers save the last two *Key* sampled values, and a comparator with "65" generates a status signal to control state transitions. This system is easy upgradable to 4-digit or longer secret key. This is an example project <u>D2.8</u>.

- 8. CLK\_generator circuits are explained in lecture <u>L8.2</u>. Adapt the frequency dividers to the desired values.

- 9. Chaining shift registers is explained in this P7 <u>unit</u>.

- 10. This is the circuit modelled in Proteus (analysis method 2). <u>Asynchronous circuit.pdsprj</u>. And how to solve such circuits in paper (analysis method 1) is explained in the many examples in <u>P5</u> of flip-flops. The key idea is to determine the sampled values at the flip-flop control inputs on the CLK rising edges, to be able to infer the outputs using the corresponding function table.