# 2223Q1 Exam 2 solution ideas

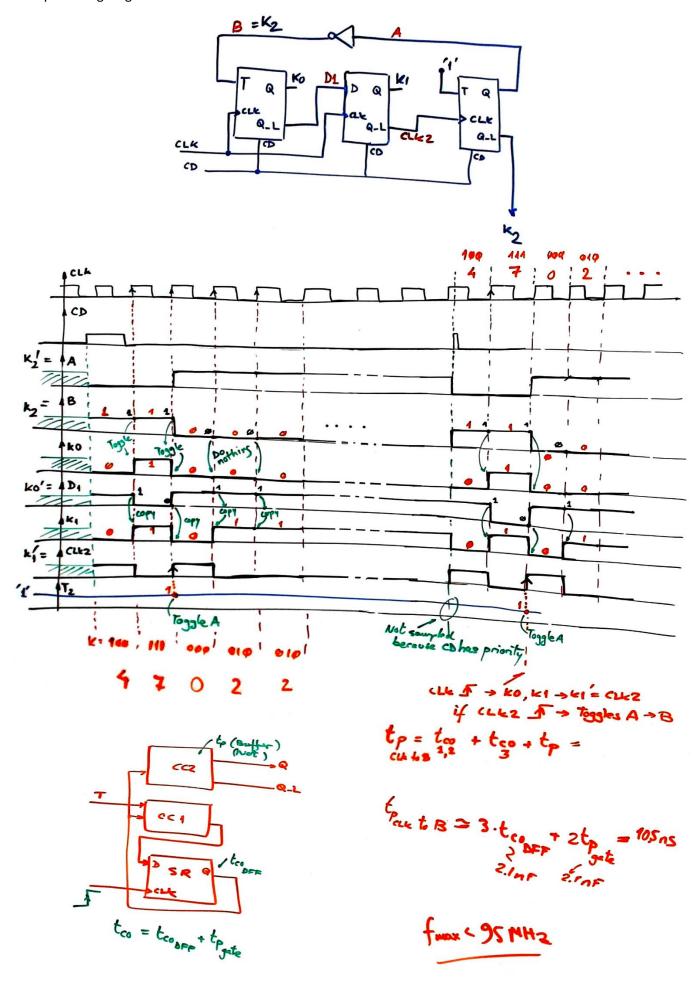

1 Example timing diagram.

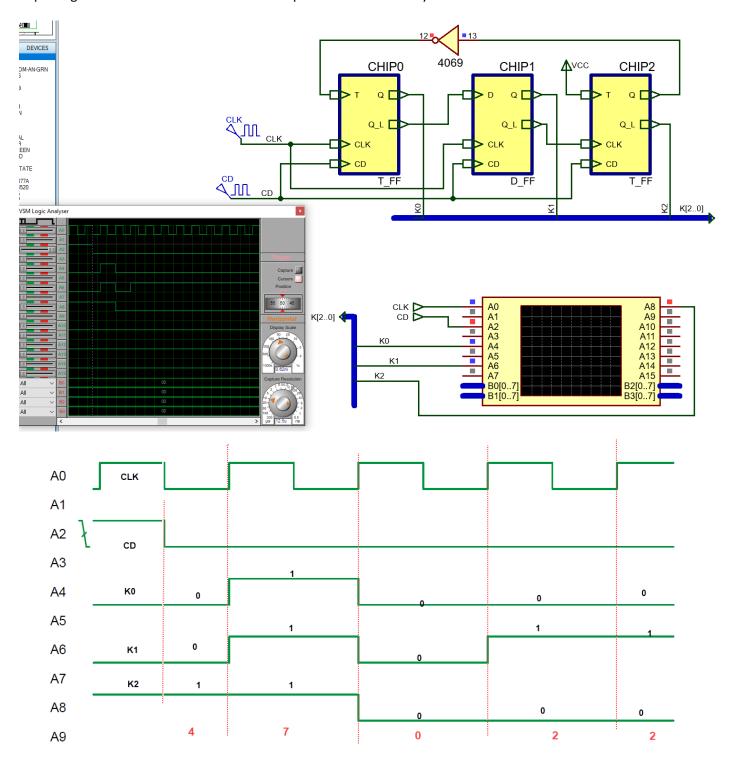

Capturing the circuit in Proteus we can develop this circuit and verify the waveforms

- 2. Chip3 has a different CLK, and this connection complicates the analysis and design. Besides, practically all common applications, like this one, a burst generator of 3-bit digital pattern consisting of codes "4-7-0-2" can be designed using the standard synchronous FSM. Instead of CD, a trigger button can generate such sequence.

- D\_FF.vhd, T\_FF.vhd, Top\_circuit.vhd are required to develop and test this device using FPGA EDA tools. Other examples in P5.

When CLK rising edge, K0 and K1 changes, and so, K1' = CLK2, and from this new rising edge, Chip3 switches A, and finally B.

# Problem 2

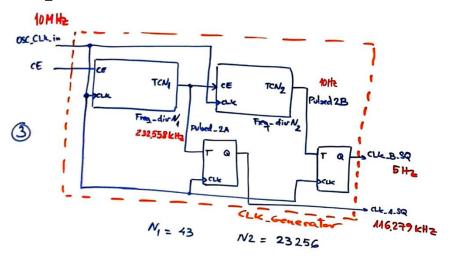

# 3. CLK\_Generator

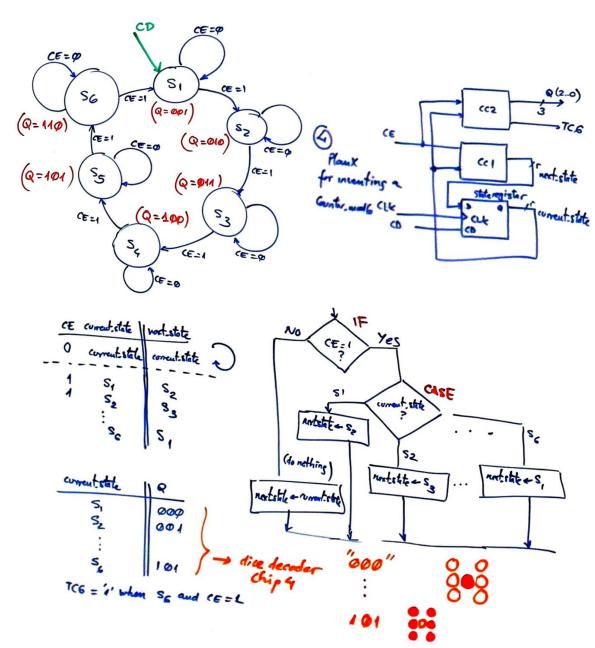

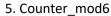

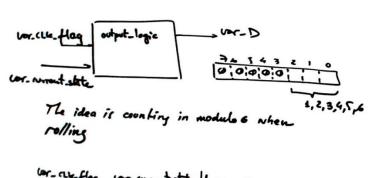

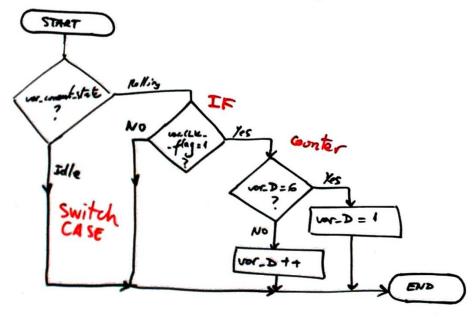

# 4. Counter\_mod6

# 7. VHDL files, D\_FF?

### **Problem 3**

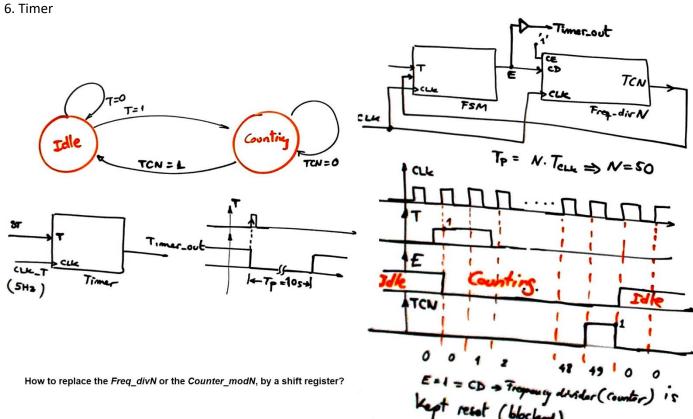

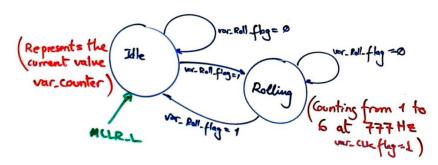

There are several ways to plan and conceive this application. This is only an example considering the state diagram in Fig. 5.

8. Hardware-software diagram

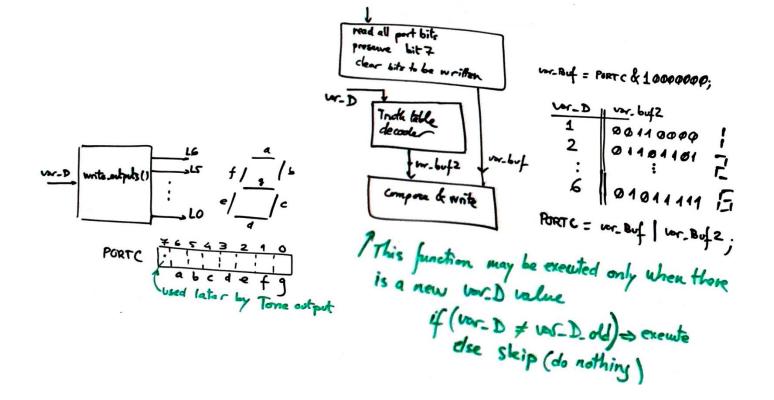

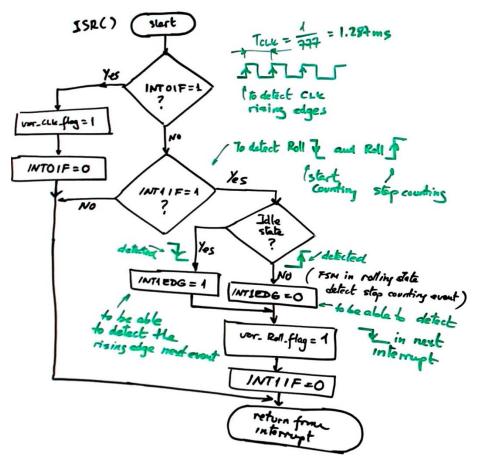

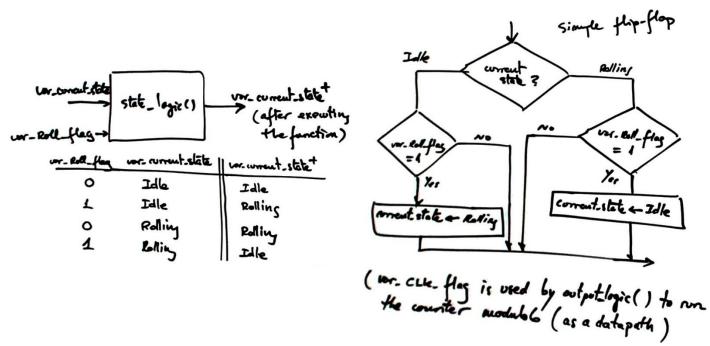

11. State\_logic()

## 12. LCD --- Materials for learning LCD is in P11

The LCD is connected in PORTD, and we can use the library of LCD functions and headers to compile applications and generate \*.HEX and \*.COF files.

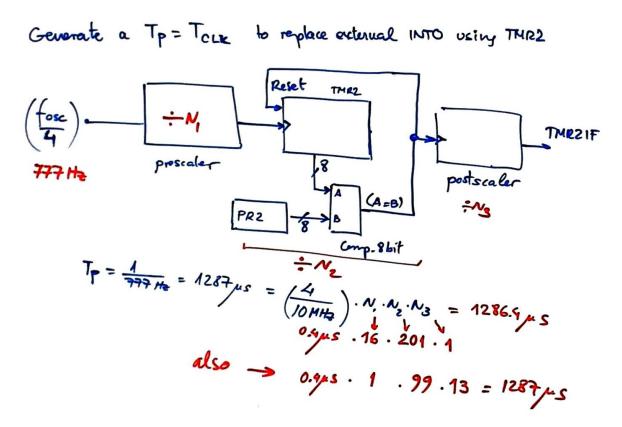

13. TMR2 for generatin a timing period  $T_P = T_{CLK} = 1/777 \text{ Hz} = 1287 \mu \text{s}$

14. TMR0 for generating a tone of 2 kHz, toggle output every  $T_P = 1$  ms