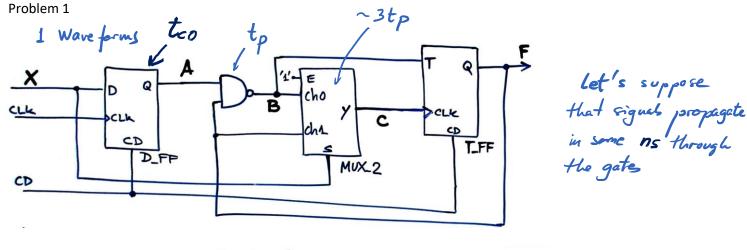

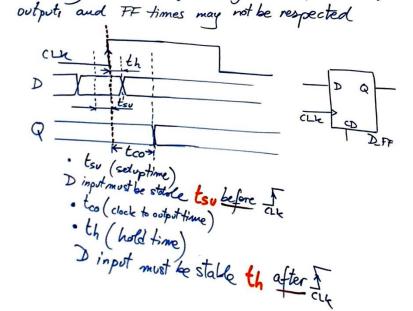

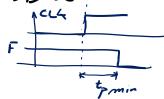

F pulse width depends on the delay between & falling odge and CLLE rising edge

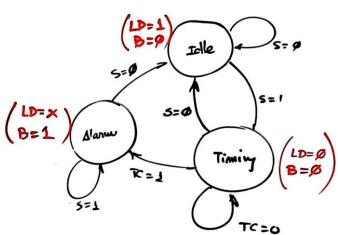

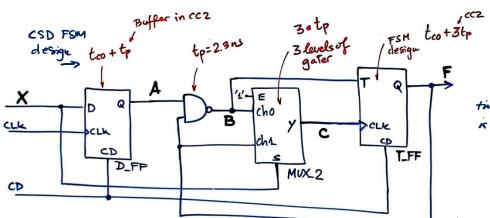

Asynchronous circuits are designed systematically as FSM and their propagation delays is predictable (t.+3.t.p.)

Asynchronous circuits are complicated for two main reasons:

- Several CLK signals do not allow systematic design

- CLK delays in ns range can generate unpredictable,

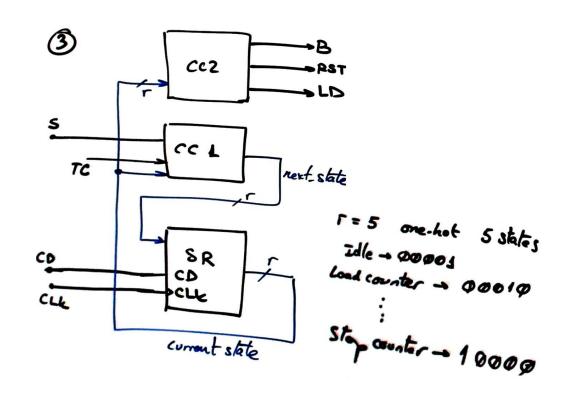

CLK to sitting gates in ccz

This insuit is not standard and its appolication is not clear. Singoly for observing how conflicated is to work with several CLK signals that depends on technologies and propagation times

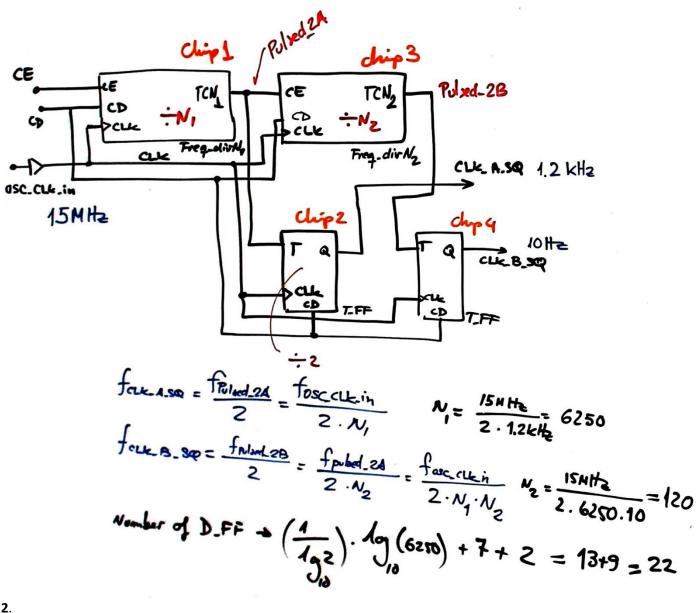

Delay measument between two signals can be implemented viry canonical synchronous FSM where all FF are driven from the same CLK and the technology is not a rellevant parameter if we do not have to work at the maximum frequency of operations.

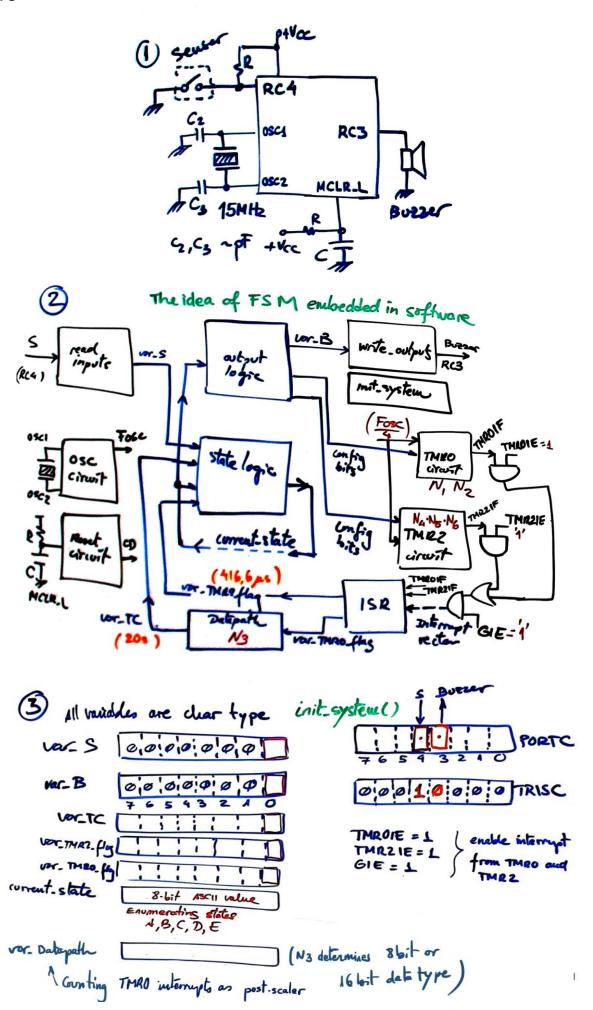

Plan C2 project in VHDL requires D\_FF.vhd, T\_FF.vhd, MUX\_2.vhd and the top Circuit\_P1.vhd files. For testing purposes, the testbench file Circuit\_P1\_tb.vhd is also required.

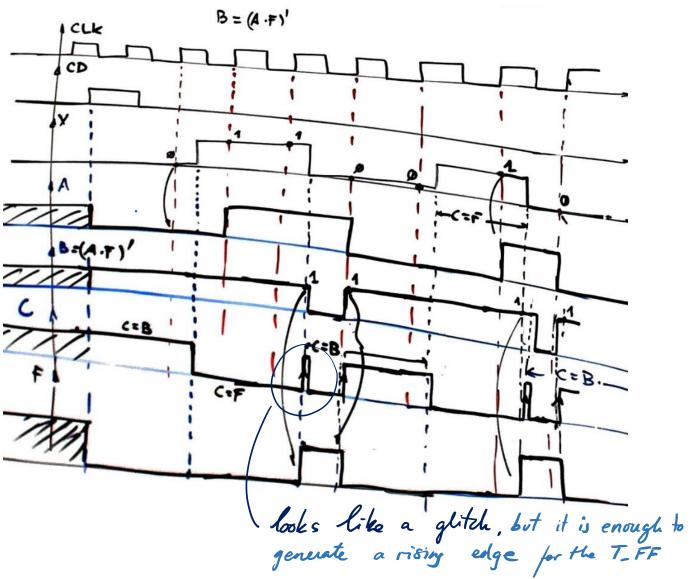

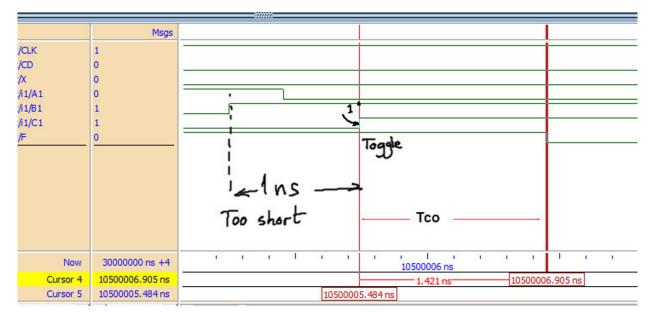

The circuit can be solved, as usual, using three methods: handwritten, Proteus and VHDL. This solution includes all the required files. The circuit works in the range of ns, where an apparent "glitch" is enough for driving the  $T_{\_}FF$ .

Functional simulation is not giving a clear sight of what is happening in the circuit. Thus, using gate-level simulations and trying different target chips (MAX II CPLD, Cyclone IV FPGA, MAX10, FPGA, etc) may give you a better comprehension on how this circuit works.

Preparing a laboratory prototype on a protoboard, for instance using CMOS classic technology chips like in Proteus, is also interesting in this case.

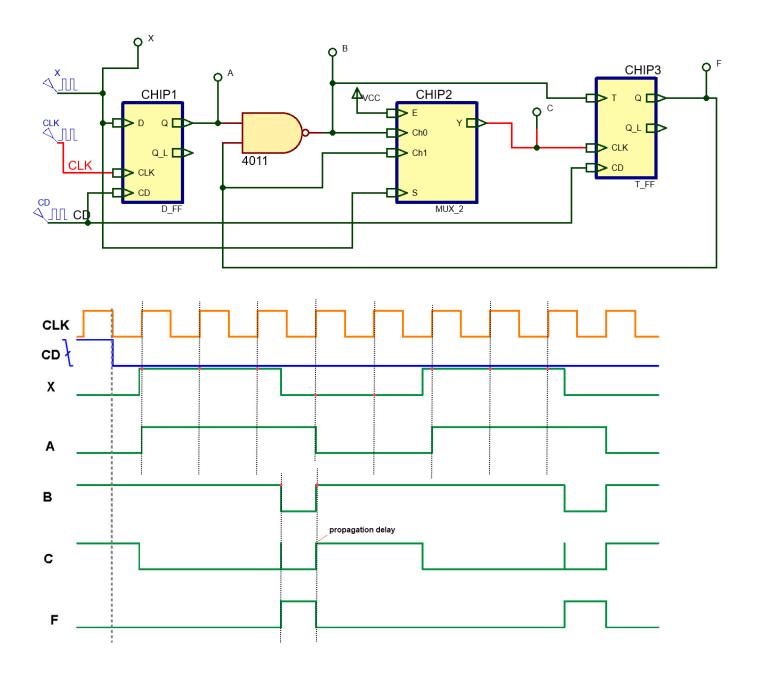

This is the <u>circuit</u> and the timing diagram from Proteus:

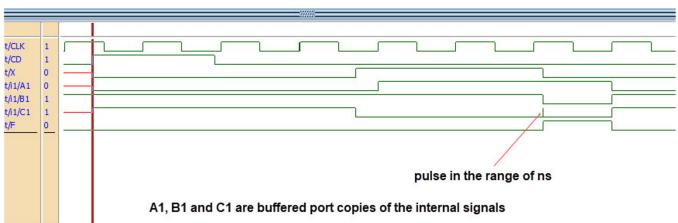

This is the timing diagram from Quartus Prime project and ModelSim targeting a MAXII CPLD device (project files available in DIGSYS).

(\*) Try this gate level simulations using MAXII and Cyclone IV devices

(4) Simply an approximate estimation considering the architecture of the circuit.

let's imagine that the progagation time from the bound for a torny le D.FF is similar to top of one gate

At the limit, we can consider that when there is a CLK rising edge, signals A > B > C switch in a chain, and C I also toggks F value

fmin = tco+tp + tp + 3tp + tco+3tp = 23ns fmax < 43.4 MHz

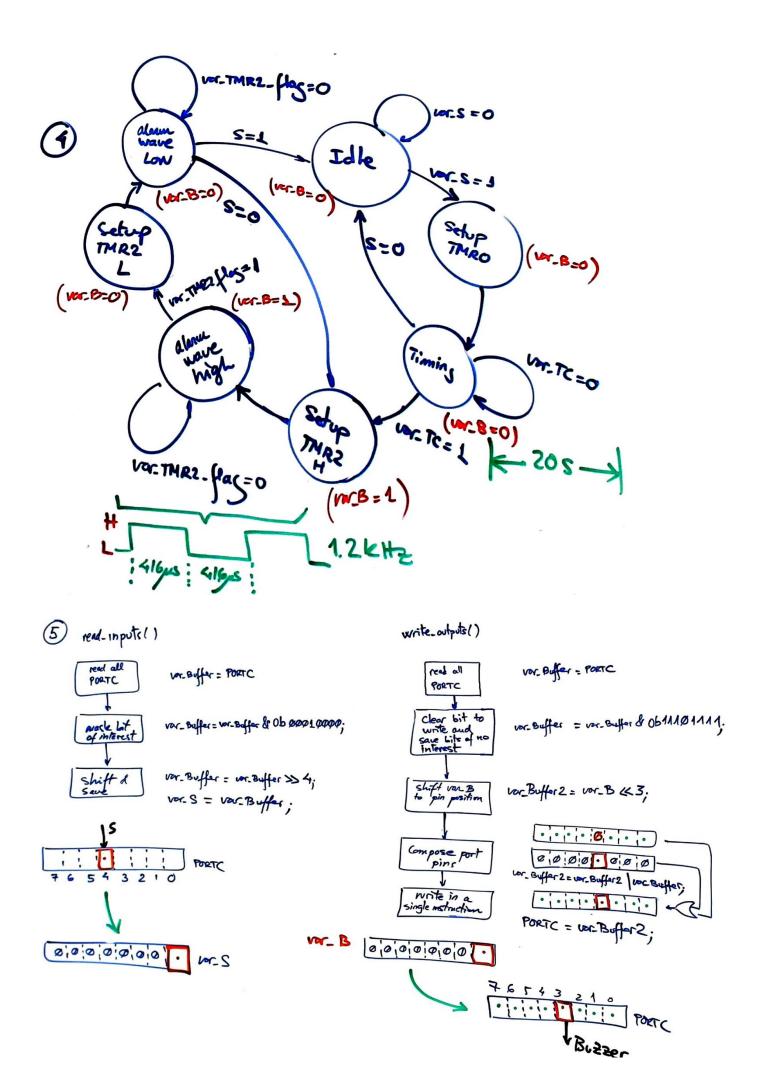

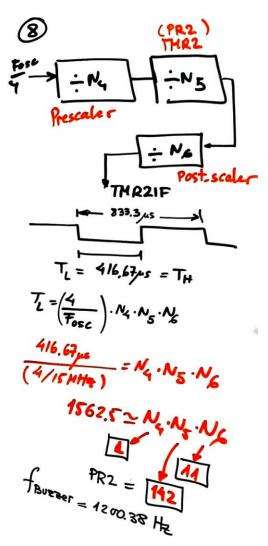

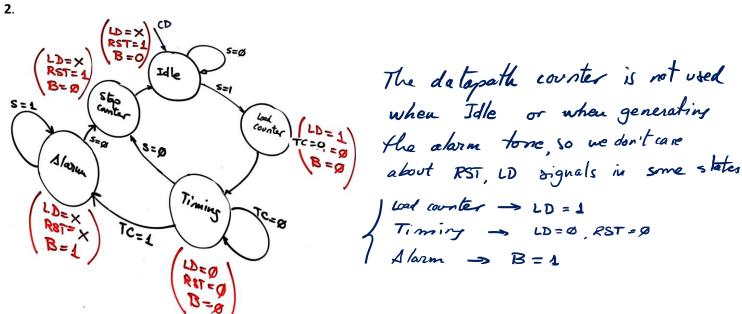

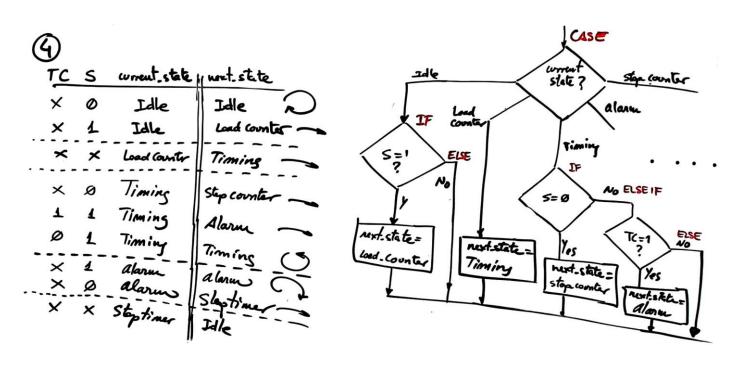

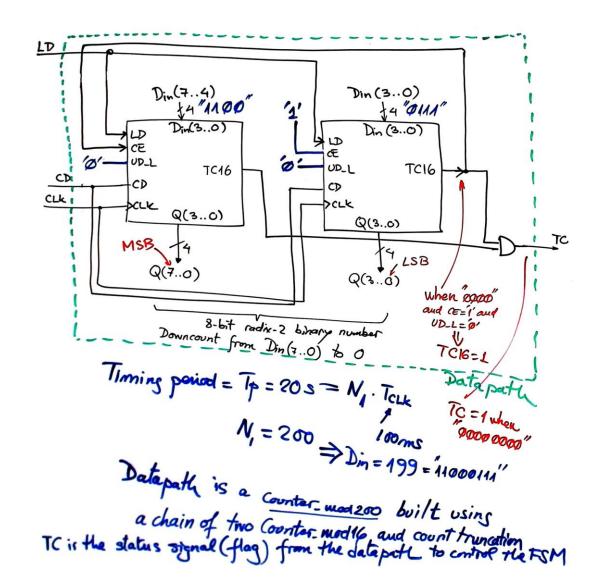

Counter is loading in parallel continuously when Idle and down counting when timing