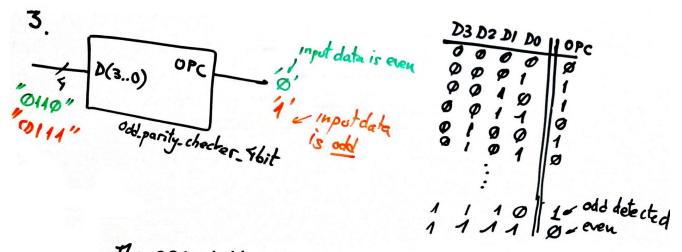

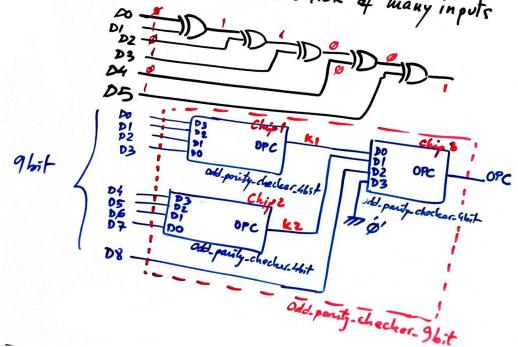

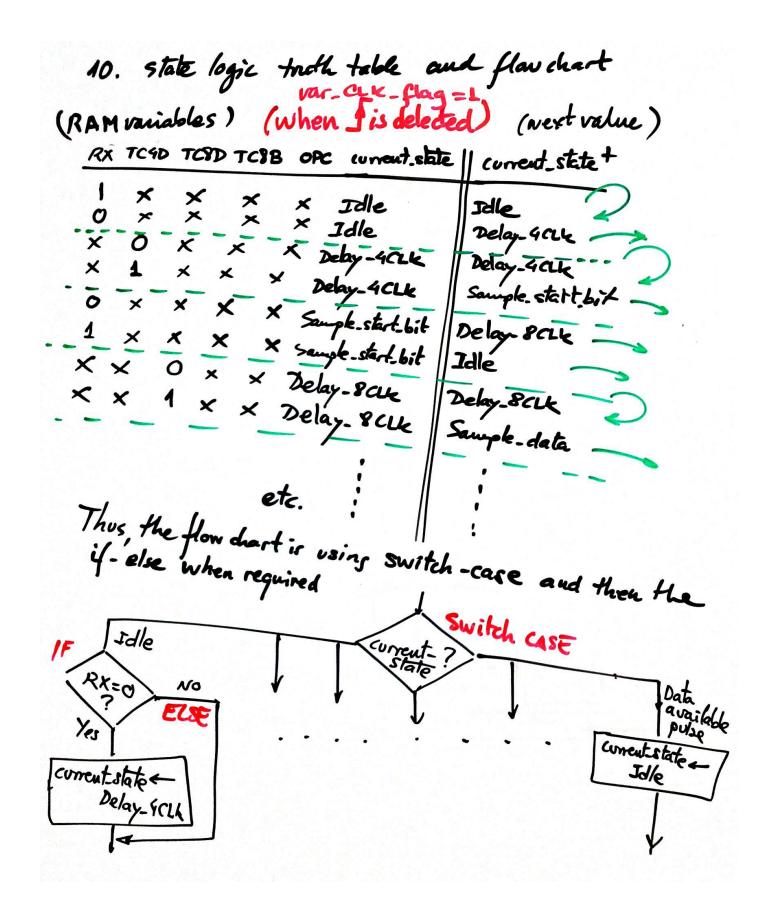

The OPC table is like a XOR of many inputs

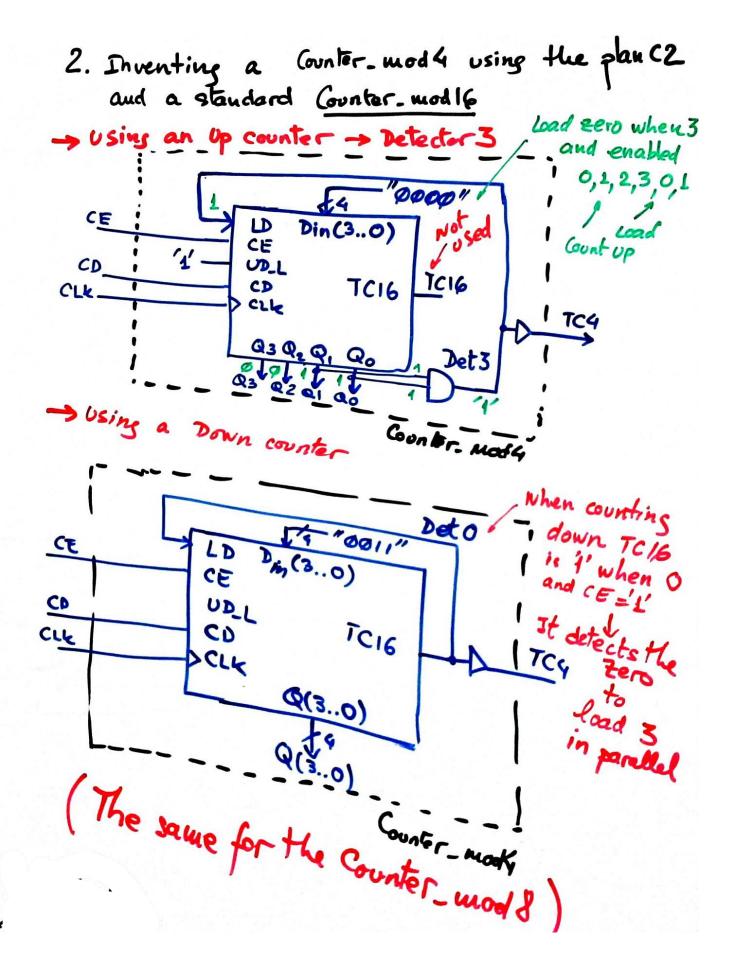

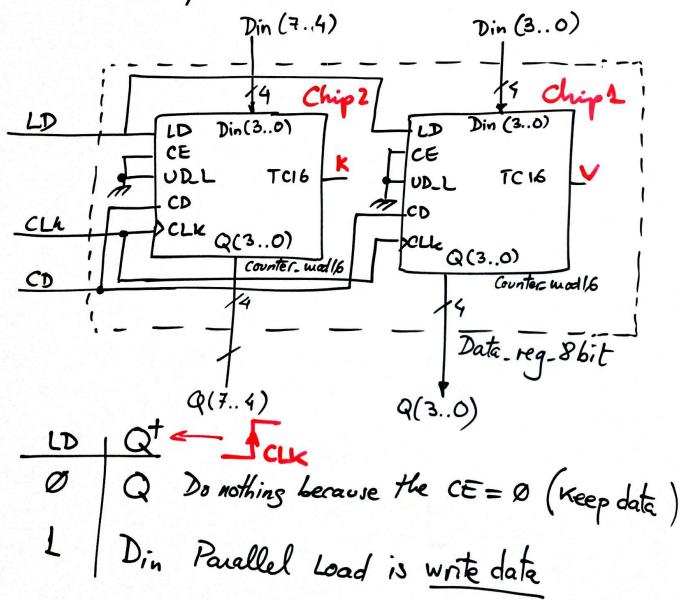

4. 8-boit data register coins the plan (2) and components counter-mod16

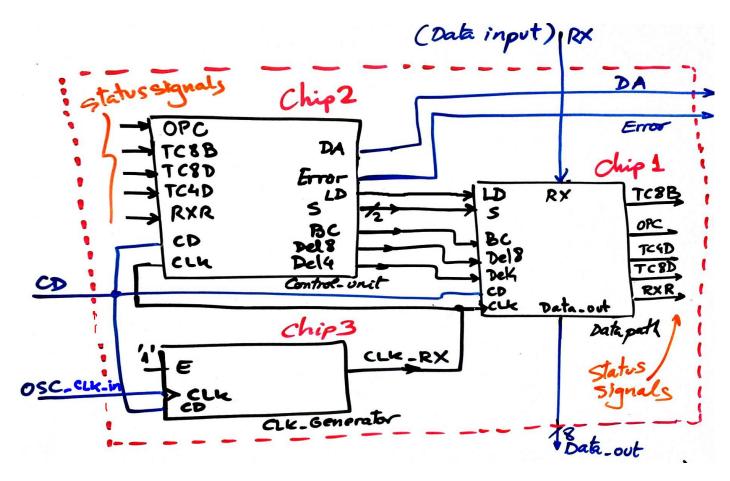

the control unit 6. Example of state diagram for RXR =1' Idle RXR='0' TC40 = ø′ Delay 4che TC4D = 1' RXR=1 start bit Engr RXR=0' RXR='L' Delay TC88=0' Stop bit check 8 CLK OPC='0' TC8D='J'TC8D='Q' Parity check Lood the data register TC&B='A' 5=70" and sample the Stop bit (all signals not indicated are kept 0) Sanyle the parity bit This is an initial state diagram that can be modified on testing design stage

7. Contrel. unit - 4D. FF (Goding in binary)

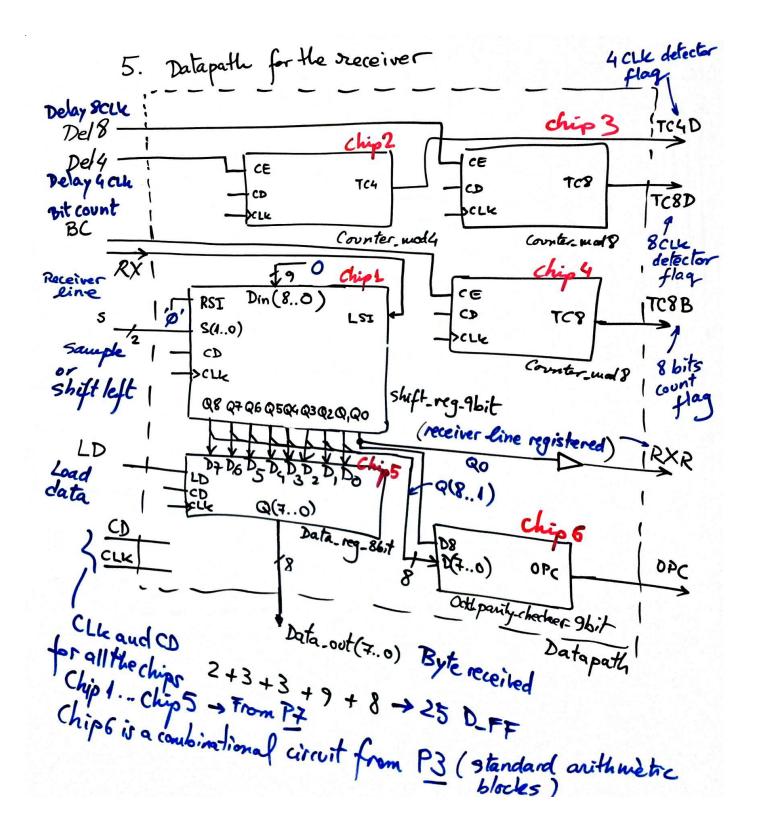

Datapath -> 25 D. FF

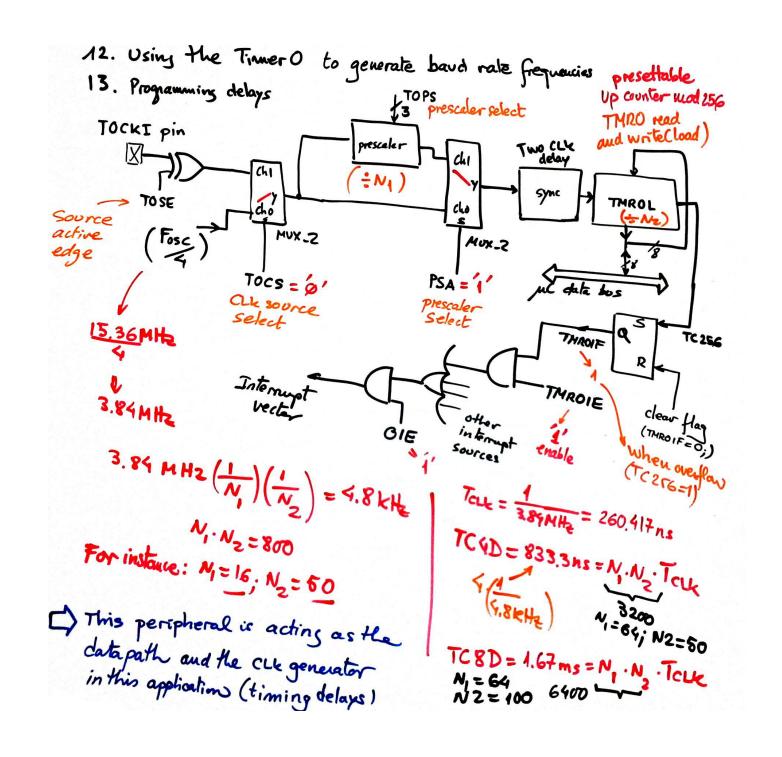

Clk. Generator -> 13 D. FF

So that the stop bit check and the data write can be solved in two states - using components Countermood the Countermood on the VHDL synthesiser of times

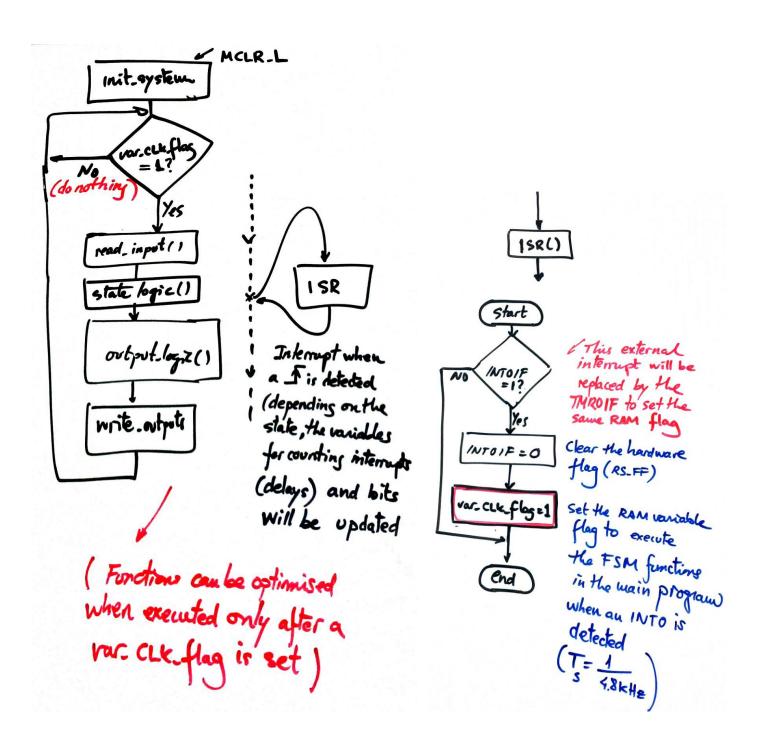

## 8. Solving the project using a mc

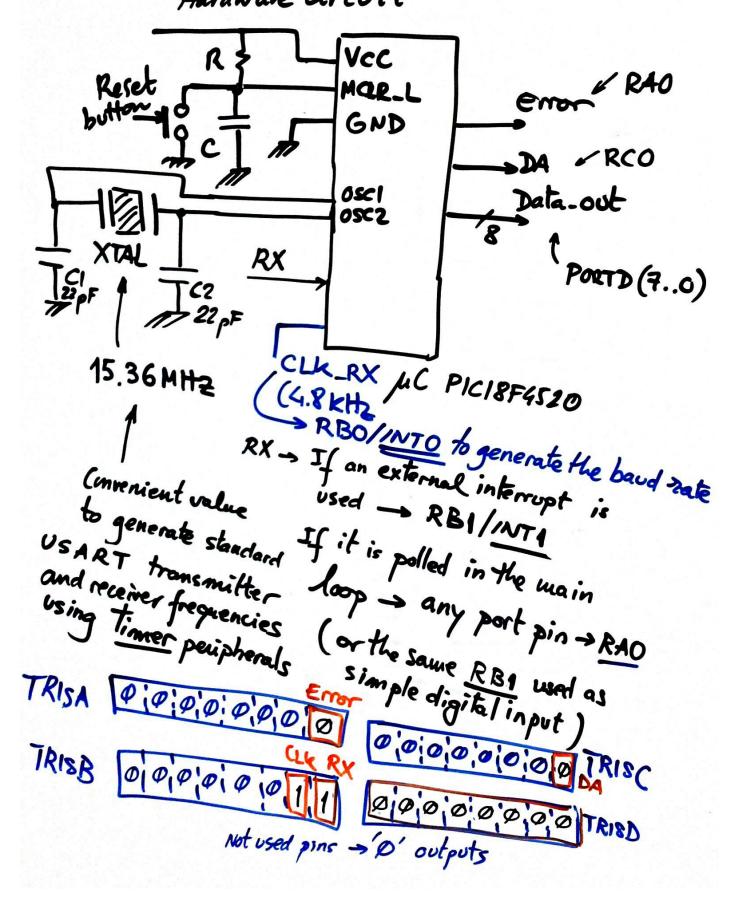

Hardware circuit

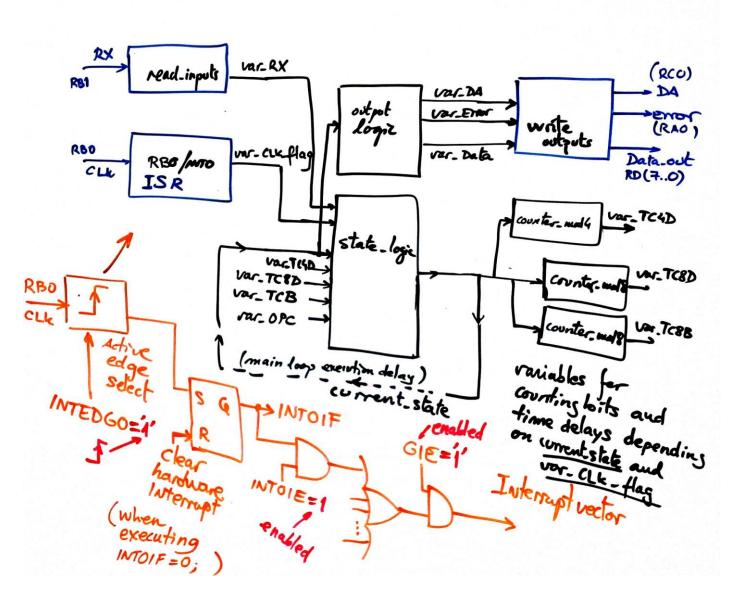

## 9. Software-hardware diagram and RAM variable of interest

## M. output logiz truth table and flanchart

Depends on current. state and RX (only in some states (RAM variables) to be able to corrent state shift data left ) ENOT Data Delay-4CLK 0 0 Saugle\_Start bit 0 Delay-8CLL 0 0 Sample Date 0 RXI Load RX, shift Odd parity-check RX 1 stop bit check Load RX, shift, calculate OPC X 1 Error-pulse 0 Deta X 1 Date. available-pulse switch - case current state Idle Sample data DA EU Enored Data = (Data | RX) << 1 watch window and