UPC. EETAC. Bachelor Degree. 2A. Digital Circuits and Systems (<u>CSD</u>). Grades will be available by October 30. Questions about the exam: office time.

Exam 1. Choose to solve only 10 of the 20 questions proposed (1p each question) October 23, 2023

### Problem 1

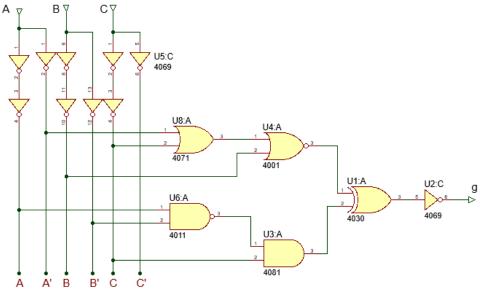

- **1.** Obtain the logic expression  $\mathbf{G} = f(A, B, C)$  of the circuit in Fig. 1. Translate it to VHDL as if you had to analyse the circuit using method III.

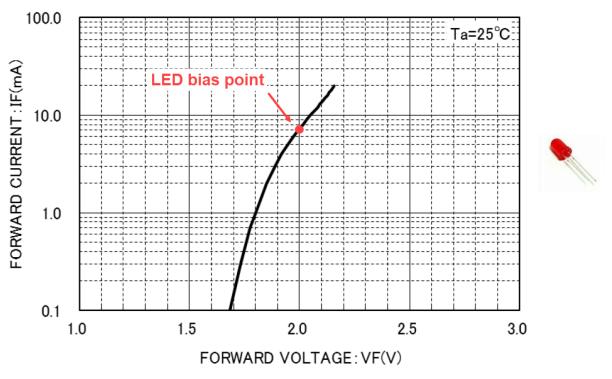

- Calculate the circuit's worst-case propagation time and explain using a timing diagram what is the meaning of such concept. Calculate the circuit's maximum speed using schematics, instruments and timing diagrams. CMOS technology has the characteristics in Fig. 2.

- 3. Calculate the static power consumption. Calculate the dynamic power consumption imagining that all the gates are switching at maximum speed. Represent the transfer function and the noise voltage margins of a CMOS gate.

- **4.** Simplify the circuit to obtain PoS or SoP equations.

- 5. Obtain de truth table of **G** = *f*(A, B, C) and the corresponding canonical equations.

- **6.** Invent a new circuit  $\mathbf{G} = f(A, B, C)$  using only NOR2 logic gates.

Fig. 1. Combinational circuit based on logic gates.

#### Electrical Characteristics – Dynamic

$T_A = 25^{\circ}C$ ; input  $t_r$ ,  $t_f = 20$  ns;  $C_L = 50$  pF;  $R_L = 200$  k $\Omega$  (unless otherwise noted)

| PARAMETER                           |                        | TEST CONDITIONS         | MIN | TYP | MAX | UNIT |   |

|-------------------------------------|------------------------|-------------------------|-----|-----|-----|------|---|

| $t_{PLH},  t_{PHL}$                 | Propagation delay time | V <sub>DD</sub> (V) = 5 |     | 55  | 110 | ns   | ] |

| Electrical Characteristics – Static |                        |                         |     |     |     |      | - |

| PARAMETER                 | TEST CONDITIONS                                                                                  | MIN                                                                                                                                                                                                                                                                 | TYP                                                                                                                                                                                                                                                    | MAX                                                                                                                                                                                                                                                           | UNIT                                                                                                                                                                                                                                                               |

|---------------------------|--------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Low-level output voltage  | V <sub>IN</sub> = 5 V, V <sub>DD</sub> = 5 V                                                     |                                                                                                                                                                                                                                                                     | 0                                                                                                                                                                                                                                                      | 0.05                                                                                                                                                                                                                                                          | V                                                                                                                                                                                                                                                                  |

| High-level output voltage | V <sub>IN</sub> = 0 ∨, V <sub>DD</sub> = 5 ∨                                                     | 4.95                                                                                                                                                                                                                                                                | 5                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                               | V                                                                                                                                                                                                                                                                  |

| Input low voltage         | V <sub>O</sub> = 4.5 ∨, V <sub>DD</sub> = 5 ∨                                                    |                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                        | 1                                                                                                                                                                                                                                                             | V                                                                                                                                                                                                                                                                  |

| Input high voltage        | $V_{\rm O}$ = 0.5 V, $V_{\rm DD}$ = 5 V                                                          | 4                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                               | V                                                                                                                                                                                                                                                                  |

| Quiescent device current  | $V_{\rm O}$ = 0.5 V, $V_{\rm DD}$ = 5 V                                                          |                                                                                                                                                                                                                                                                     | 0.01                                                                                                                                                                                                                                                   | 0.25                                                                                                                                                                                                                                                          | μA                                                                                                                                                                                                                                                                 |

| -                         | Low-level output voltage<br>High-level output voltage<br>Input low voltage<br>Input high voltage | Low-level output voltage $V_{IN} = 5 \lor, \lor_{DD} = 5 \lor$ High-level output voltage $\bigvee_{IN} = 0 \lor, \lor_{DD} = 5 \lor$ Input low voltage $\bigvee_{O} = 4.5 \lor, \lor_{DD} = 5 \lor$ Input high voltage $\bigvee_{O} = 0.5 \lor, \lor_{DD} = 5 \lor$ | Low-level output voltage $V_{IN} = 5 \lor, \lor_{DD} = 5 \lor$ High-level output voltage $\lor_{IN} = 0 \lor, \lor_{DD} = 5 \lor$ Input low voltage $\lor_O = 4.5 \lor, \lor_{DD} = 5 \lor$ Input high voltage $\lor_O = 0.5 \lor, \lor_{DD} = 5 \lor$ | Low-level output voltage $V_{IN} = 5 \lor, \lor V_{DD} = 5 \lor$ 0High-level output voltage $V_{IN} = 0 \lor, \lor V_{DD} = 5 \lor$ 4.95Input low voltage $V_O = 4.5 \lor, \lor V_{DD} = 5 \lor$ 4Input high voltage $V_O = 0.5 \lor, \lor V_{DD} = 5 \lor$ 4 | Low-level output voltage $V_{IN} = 5 \lor, \lor V_{DD} = 5 \lor$ 00.05High-level output voltage $V_{IN} = 0 \lor, \lor V_{DD} = 5 \lor$ 4.955Input low voltage $V_O = 4.5 \lor, \lor V_{DD} = 5 \lor$ 1Input high voltage $V_O = 0.5 \lor, \lor V_{DD} = 5 \lor$ 4 |

$P_S + P_{dyn} = I_{DDQ} \cdot V_{DD} + V_{DD}^2 \cdot C_L \cdot f$

Fig. 2. CMOS technology characteristics for a single typical logic gate.

# Problem 2

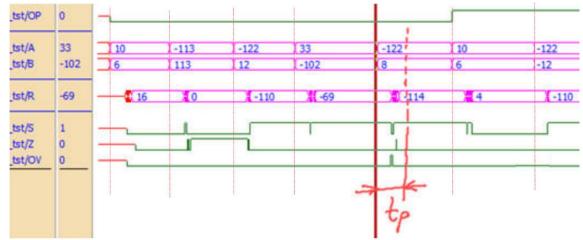

The Fig. 3 shows the symbol and an example of a functional simulation wave diagram of the *Sel\_comp\_8bit* comparator when  $\mathbf{N} = \mathbf{0}^{\prime}$ , and so, the data is unsigned in radix-2.

- **7.** How long is the circuit's truth table? Write some values of the truth table using the input stimulus in Fig. 3 represented in '1' and '0' in radix-2 when  $\mathbf{N} = '0'$ . What is the range of the operands?

- 8. Draw a similar timing diagram and truth table deducing the new output values suposing that now N = '1' and thus the same A and B input combinations in '0' and '1' represent integer numbers in two's complement. What is the range of the operands?

- **9.** Propose a plan C2 hierarchical internal design of the circuit in Fig. 3 based on simpler chips of the same kind. How many components will be necessary? How many VHDL files will contain this project?

- 10. Draw the testbench schematic fixture. If in the testbench the time constant *Min\_Pulse* = 1.75 μs, how long does it take to run the simulation of the complete truth table? If the internal component *Comp\_1bit* is solved using plan A equations in 3-levels-of-gates, and the techology is the CMOS in Fig. 2, what is the minimum *Min\_Pulse* value?

**NOTE** for all questions: explain what you do, how are you inventing the circuits and justify your results and calculations.

## **Problem 3**

The equation in Fig. 4 represents a truth table which is going to be solved in VHDL using the plan B (behavioural) and the plan C2 (hierarchical based on components).

$$\mathbf{P} = f(x_3, x_2, x_1, x_0) = \prod M(1, 2, 5, 7, 8, 10, 13, 15)$$

Fig. 4. Truth table of a 4-input combinational circuit named *Circuit\_P*.

- **11.** Solve the function **P** using a plan B, a behavioural approach. Represent a schematic or flowchart and explain how to translate it into VHDL. What resources are used when synthesising this circuit in an FPGA?

- 12. Solve the function P using the method of decoders (MoD).

- **13.** Invent a decoder *Dec\_4\_16* using components of the same kind *Dec\_2\_4* and logic gates if necessary.

- **14.** Solve the function **P** using the method of multiplexers (MoM) and a *MUX\_4*.

- **15.** Invent a *MUX\_16* using components of the same kind (*MUX\_4* and *MUX\_2*) and logic gates if necessary.

- Draw and calculate a circuit to drive a LED active-low connected at output P in the indicated bias point in Fig. 5.

Use the chip technology in Fig. 2.

Fig. 5. Typical LED bias characteristics.

## Problem 4

On the design an *Int\_Add\_subt\_9bit* arithmetic circuit for 2C integer numbers.

**17.** Draw the circuit symbol and example truth table observing simulation results in Fig. 6 and considering the operands in 2C. Determine the range of the operands (A, B) and result (R). Perform using binary symbols ('0' and '1'), some operations for integers in binary two's complement to demonstrate the algorithm.

Fig. 6. Example of *Int\_Add\_Subt\_9bit* simulation wave results.

- 18. Using Fig. 6 as a reference, draw an ideal timing diagram adding some new operands in 2C to demonstrate as well how the circuit overflows (OV = '1'). Perform the arithmetic to calculate results using binary symbols ('0' and '1'). What is the OV detection algorithm or function?

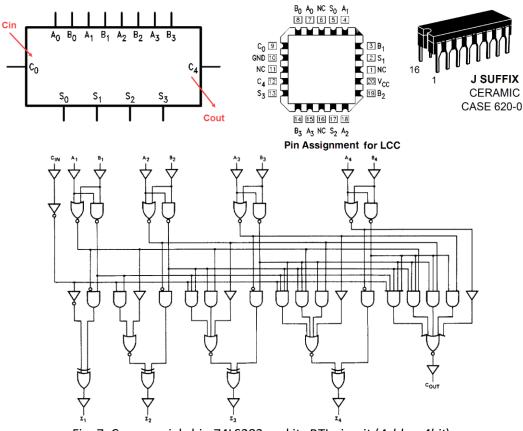

- **19.** Propose and draw a hierarchical plan C2 internal circuit based on binary radix-2 adder components such the classic chip 74LS283 represented in Fig. 7.

Fig. 7. Commercial chip 74LS283 and its RTL circuit (Adder\_4bit).

**20.** Explain what is the parameter  $t_P$  in Fig. 6 and how and using which tools such simulation results are obtained. If the technology 74LS has a  $t_{P(1gate)} = 3.6$  ns, calculate and explain the maximum operating speed of the Int\_Add\_Subt\_9bit.