UPC. EETAC. Bachelor Degree. 2A. Digital Circuits and Systems (CSD). Grades will be available online by November 14. Questions about the exam at office time.

| Midterm exam. | November 7, 2022 |

|---------------|------------------|

|               |                  |

## **Problem 1**

1. Solve the function K in Fig. 1 using only 2-input NAND.

$$K = f(X_3, X_2, X_1, X_0) = \sum m(0, 1, 4, 7, 11, 14) + \sum d(6, 9, 13)$$

Fig. 1. Truth table of *Circuit\_K*. ('d' are don't care terms).

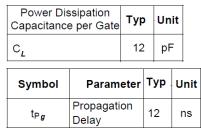

- 2. *Circuit K* invented in **1** will be implemented using a classic technology HCT (High Speed CMOS with TTL outputs) with the characteristics shown in Fig. 2. Deduce and explain the maximum speed of computing and estimate the total power consumption at such frequency.

- 3. What is the minimum value of *Min Pulse* if we intent to run gate-level simulations?

| Symbol          | Parameter                   | Test Conditions         | T <sub>A</sub> = -40°C | C to +85°C | Unit | Power Dis                 | ssipation   | -    | <b></b> |                |

|-----------------|-----------------------------|-------------------------|------------------------|------------|------|---------------------------|-------------|------|---------|----------------|

| Symbol          | Farameter                   | $V_{CC} = 5 V$          | Min                    | Max        |      | Capacitanc                | e per Gate  | Тур  | Un      | It             |

| VIH             | High-level Input<br>Voltage |                         | 2.0                    |            | V    | CL                        |             | 12   | pF      | =              |

| VIL             | Low-level Input<br>Voltage  |                         |                        | 0.8        | V    | Symbol                    | Param       | eter | Тур     | Uni            |

| V               | High-level Output           | I <sub>OH</sub> = -20µА | 4.4                    |            |      |                           | Propagati   | on   | 40      |                |

| V <sub>OH</sub> | Voltage                     | I <sub>OH</sub> = -4mA  | 3.84                   |            | _ ヾ  | t <sub>Pg</sub>           | Delay       |      | 12      | ns             |

|                 | Low-level Output            | I <sub>OL</sub> = 20μΑ  |                        | 0.1        | V    |                           |             |      |         |                |

| Vol             | Voltage                     | I <sub>OL</sub> = 4.0mA |                        | 0.33       |      | $P_{gate} = P_S + P_{dv}$ | $= I_{CCO}$ | Vcc  | + l     | $r_{cc}^{2}$ . |

| Icc             | Supply Current              | VI = GND or Vcc         |                        | 20         | μA   | gate - 5 · - dy           | n ccy       |      |         | 55             |

Fig. 2. Technology characteristics of HCT logic gates (adapted from 74HCT00 datasheet).

- 4. Invent Circuit\_K using the method of multiplexers with a MUX\_8. Solve the MUX\_8 expanding only MUX\_2 and logic if necessary. How many VHDL files will this project contain?

- 5. Firstly, invent Circuit\_K using the method of decoders. Secondly, solve your decoder expanding Dec\_2\_4 and logic if necessary.

## Problem 2

(4p)

(3p)

The truth table in Fig. 3 represents a Selectable Add Subt Comp 12bit arithmetic circuit for operating with 6. both integer (N = 1) and radix-2 (N = 0) numbers. Draw its symbol. Find the range of input and output data.

| N | OP | A       | в       | $C_{\text{out}}$ | R      | ov | Z | GT | EQ | LT |

|---|----|---------|---------|------------------|--------|----|---|----|----|----|

| 0 | Х  | 36      | 157     | 0                | 193    | Х  | 0 | 0  | 0  | 1  |

| 0 | х  | 3571    | 3571    | 1                | 3046   | х  | 0 | 0  | 1  | 0  |

| 1 | 0  | (+2030) | (-1562) | х                | (+468) | 0  | 0 | 1  | 0  | 0  |

| 1 | 1  | (-2030) | (-2030) | х                | 0      | 0  | 1 | 0  | 1  | 0  |

| 1 | 0  | (-2030) | (-2030) | х                | х      | 1  | 0 | 0  | 1  | 0  |

| 1 | 1  | (+1562) | (-2030) | х                | х      | 1  | 0 | 1  | 0  | 0  |

| 1 | 0  | (-2030) | (+1562) | х                | (-468) | 0  | 0 | 0  | 0  | 1  |

Fig. 3. Truth table of the arithmetic circuit Selectable\_Add\_Subt\_Comp\_12bit

- 7. Convert the signed and unsigned numbers in Fig. 3 into binary.

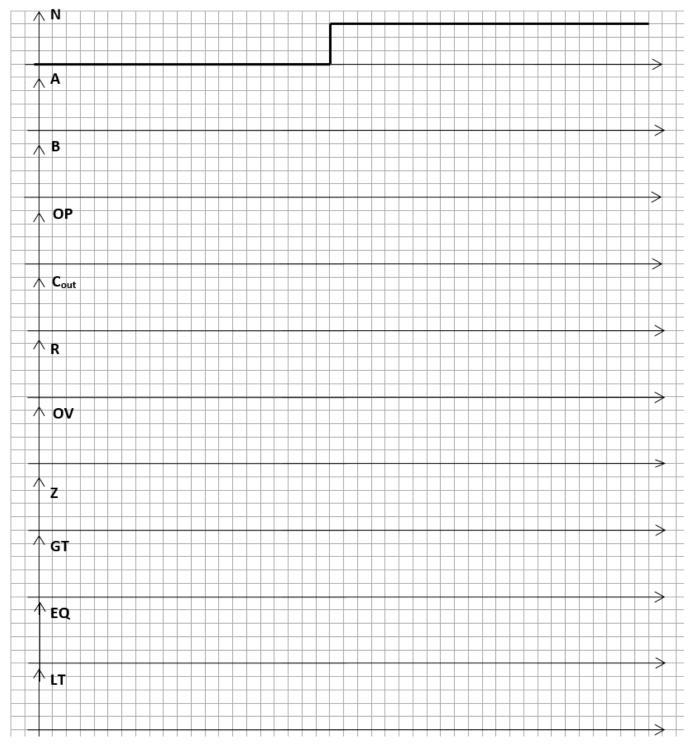

- 8. Draw an example of timing diagram (use the Fig. 4 template). Supposing Min Pulse = 105 ns calculate how long does it take to test all the truth table of Selectable\_Add\_Subt\_Comp\_12bit.

- Design the Selectable\_Add\_Subt\_Comp\_12bit circuit using components. 9.

- 10. Propose an internal circuit for the Int Add Subt 12bit using components.

- Design a Comp\_4bit using Comp\_1bit. 11.

- 12. Design the output EQ using XOR gates.

- 13. Design an Adder 1bit using maxterms.

Fig. 4. Waveform template for representing the timing diagram in question 8.

## Problem 3

(3p)

Draw the symbol of the circuit represented by the truth table in Fig. 5 and calculate the limiting resistors to drive active-low LEDs (V<sub>AKQ</sub> = 1.7 V, I<sub>DQ</sub> = 3.5 mA) connected at the outputs supposing the electrical characteristics in Fig. 2.

| Ρ | К | Y | Т | V_L | W_L | Z_L |

|---|---|---|---|-----|-----|-----|

| 0 | Х | Х | Х | 1   | 0   | 0   |

| 1 | 0 | Х | Х | 0   | Х   | 1   |

| 1 | 1 | 1 | Х | 0   | 1   | 0   |

| 1 | 1 | 0 | 1 | 0   | 1   | 0   |

| 1 | 1 | 0 | 0 | 1   | 0   | 0   |

- **15.** Write the *Circuit\_1* equations using PoS or SoP and draw the logic circuit.

- **16.** Plan *Circuit\_1* drawing a flowchart or schematic using plan B. Translate the main details to VHDL.